SWAU130A March 2023 – December 2023

2.2.4 JTAG Headers

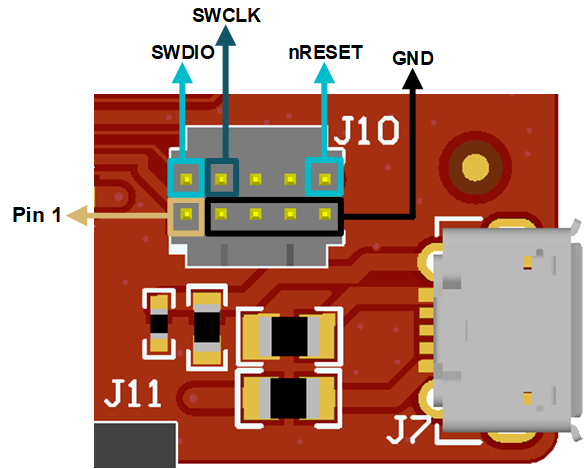

The BP-CC3301 was designed with 2 JTAG headers (J10, J11) for SWD interface with the XDS110 debug probe. The signal assignment for these headers are described in the figures and tables below.

The main JTAG interface for the BP-CC3301 is via the LP-XDS110 (ET) that is connected to the 20pin header (J11). A XDS110 debug probe can also interface with this board via a 10-pin header (J10), however this header is not populated with the default kit.

Figure 2-4 ARM 10 pin JTAG Connector (J10)

Figure 2-4 ARM 10 pin JTAG Connector (J10)Table 2-5 ARM 10 pin JTAG Connector (J10) Assignment

| Pin | Signal Name | Description |

|---|---|---|

| J10.1 | VCC_BRD_1V8 | 1.8V supply for reference voltage to connector |

| J10.2 | SWDIO | Serial wire data in/out |

| J10.4 | SWCLK | Serial wire clock |

| J10.10 | RESET_1V8 | nReset (Enable line for CC3301) |

| J10.3, J10.5, J10.7, J10.9 | GND | Board ground |

Figure 2-5 20 pin

LP-XDS110 Connector (J11)

Figure 2-5 20 pin

LP-XDS110 Connector (J11)Table 2-6 20 Pin LP-XDS110 Connector (J11)

Assignment

| Pin | Signal Name | Description |

|---|---|---|

| J11.6 | SWCLK | Serial wire clock |

| J11.8 | SWDIO | Serial wire data in/out |

| J11.10 | RESET_1V8 | nReset (Enable line for the CC3301) |

| J11.12 | UART_TX_1V8 | The CC3301 UART TX to host for BLE host controller interface |

| J11.14 | UART_RX_1V8 | The CC3301 UART RX from host for BLE host controller interface |

| J11.16 | VCC_BRD_1V8 | 1.8V supply for reference voltage to connector |

| J11.18 | VCC_BRD_5V | 5 V supply to BP-CC3301 from LP-XDS110 |

| J11.1, J11.7, J11.13, J11.19, J11.20 | GND | Board ground |