TIDUEY8 March 2023

- Description

- Resources

- Features

- Applications

- 5

- 1System Description

-

2System Overview

- 2.1 Design Block Diagram

- 2.2 Highlighted Products

- 2.3

Design Steps

- 2.3.1 Multiple JESD204B Synchronization Requirements

- 2.3.2 Clock Tree Design

- 2.3.3 Power Management

- 3Getting Started Hardware and Software

- 4Testing and Results

- 5Design and Documentation Support

- 6About the Authors

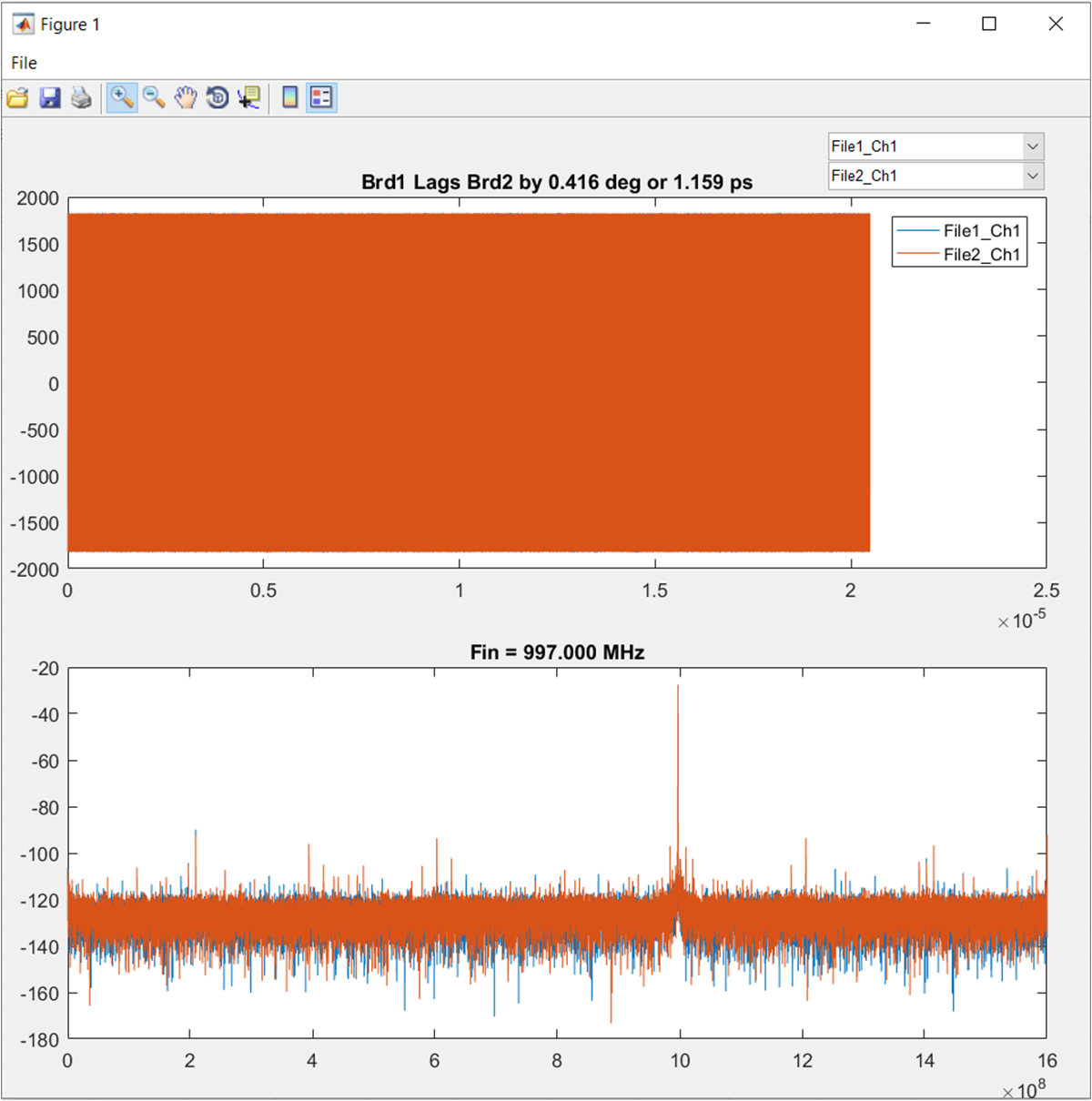

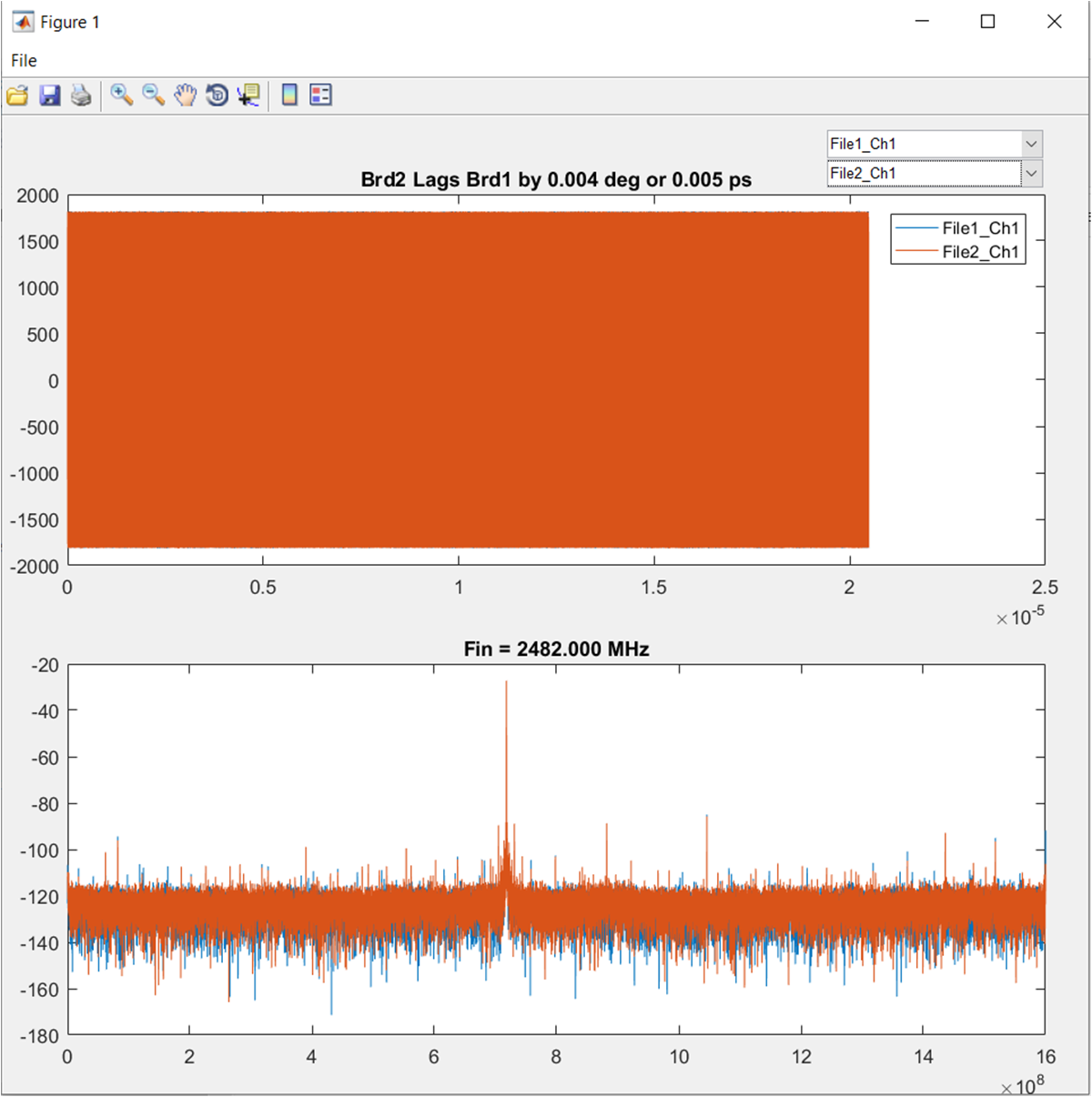

4.2.4 Channel-to-Channel Skew Measurement

Figure 4-12 and Figure 4-13 show the time skew between two ADC12DJ3200EVMCVAL channels at different input frequencies. This skew is evaluated by calculating the phase difference between signals captured from each ADC. These measurements were taken at a 3.2-GHz sampling frequency and the measured time skew was < 5 ps for each input frequency.

Figure 4-12 shows the plot of the output samples of the two ADCs for a 997-MHz input, this plot is in the first Nyquist zone for a 3200-MHz sampling clock. Figure 4-13 is the plot of the output samples for a 2482-MHz input, which is in the second Nyquist zone for a 3200-MHz sampling clock. The 2482-MHz input signal aliases to 882 MHz.

Figure 4-12 Board Skew at 997

MHz

Figure 4-12 Board Skew at 997

MHz Figure 4-13 Board Skew at 2482

MHz

Figure 4-13 Board Skew at 2482

MHz