TIDUF23 may 2023

- Description

- Resources

- Features

- Applications

- 5

- 1System Description

- 2System Overview

-

3Hardware, Software, Testing Requirements,

and Test Results

- 3.1 Hardware Requirements

- 3.2 Test Setup

- 3.3 Test Procedure

- 3.4 Test Results

- 4General Texas Instruments High Voltage Evaluation (TI HV EVM) User Safety Guidelines

- 5Design and Documentation Support

- 6Terminology

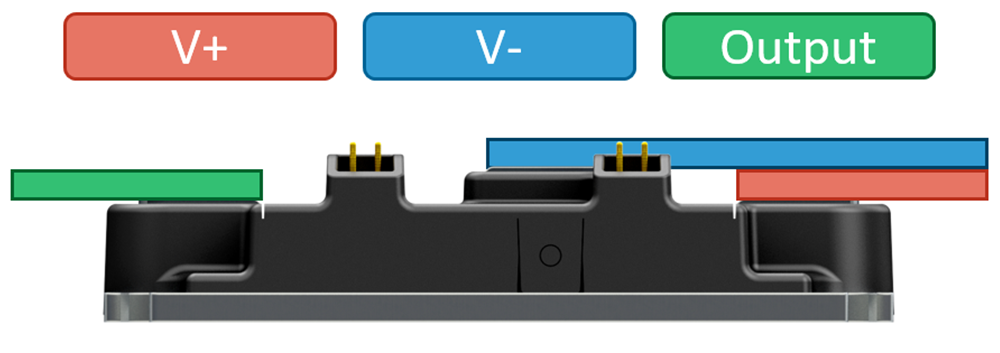

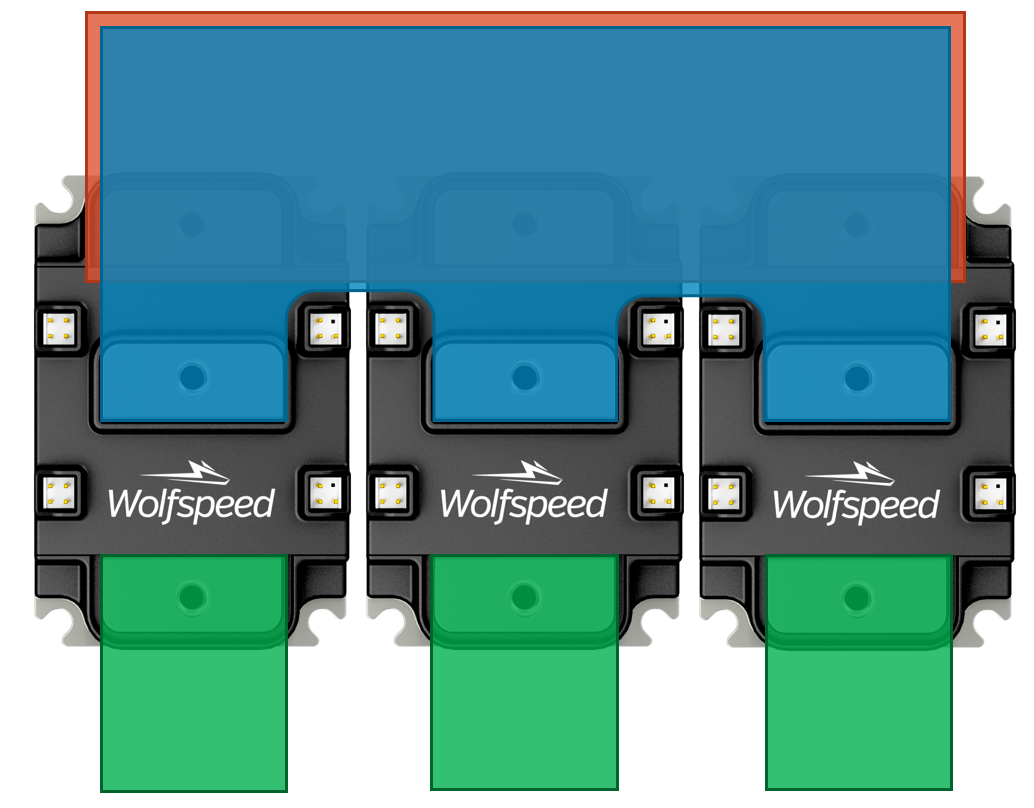

3.1.1.6.2 Module Power Terminals

The current loops in the XM3 power module have been designed such that they are wide, low profile, and evenly distributed between the devices so that they each have equivalent impedances across a switch position. The power terminals are vertically offset as shown in Figure 3-6 such that the bus bars between the DC link capacitors and the module can be laminated all the way up to the module without requiring bends, coining, standoffs, or complex isolation. A representative 3-phase inverter bussing is illustrated in Figure 3-7. Ultimately this achieves a low-inductance throughout the entire power loop from the DC link capacitors to the SiC devices. A XM3 module without devices was connected to a Keysight E4990A Impedance Analyzer to extract the parasitic inductance of the package. The power loop inductance from V+ to V- is 6.7 nH measured at 10 MHz.

Figure 3-6 Side View of XM3 Module

Showing Non-planar Power Leads

Figure 3-6 Side View of XM3 Module

Showing Non-planar Power Leads Figure 3-7 Illustration Showing 3-Phase

Bussing Layout

Figure 3-7 Illustration Showing 3-Phase

Bussing Layout