SNLS568D March 2017 – May 2020 LMH1228

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 4-Level Input Pins and Thresholds

- 7.3.2 OUT0_SEL and SDI_OUT2_SEL Control

- 7.3.3 Input Signal Detect

- 7.3.4 Continuous Time Linear Equalizer (CTLE)

- 7.3.5 Clock and Data (CDR) Recovery

- 7.3.6 Internal Eye Opening Monitor (EOM)

- 7.3.7 Output Function Control

- 7.3.8 Output Driver Control

- 7.3.9 Status Indicators and Interrupts

- 7.4 Device Functional Modes

- 7.5 Register Maps

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RTV|32

Thermal pad, mechanical data (Package|Pins)

- RTV|32

Orderable Information

6.8 Typical Characteristics

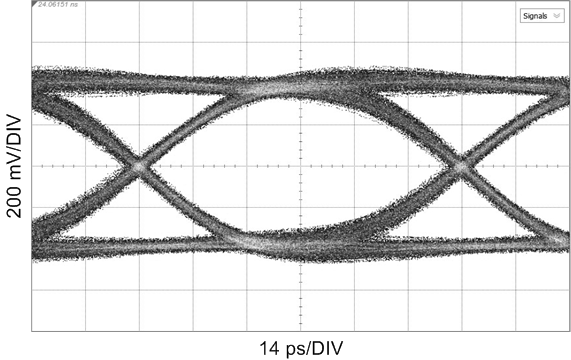

TA = 25°C and VIN = VDD_CDR = 2.5 V (unless otherwise noted) Figure 4. Output at 11.88 Gbps, Measured at SDI_OUT1+,

Figure 4. Output at 11.88 Gbps, Measured at SDI_OUT1+,

20-in. FR4 Before IN0±

Measured with LMH1297EVM

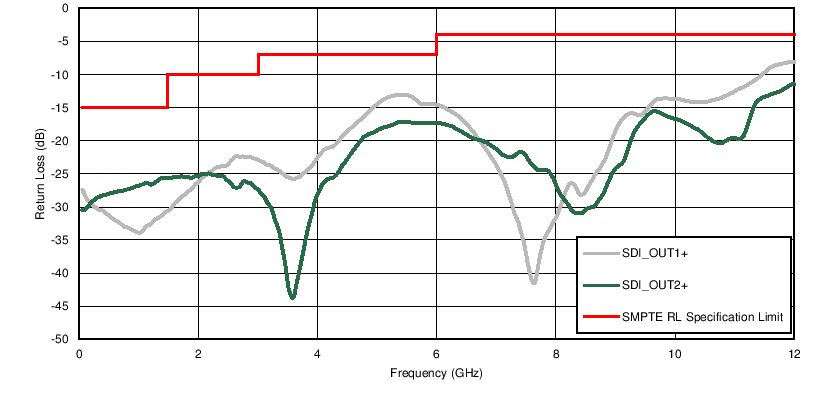

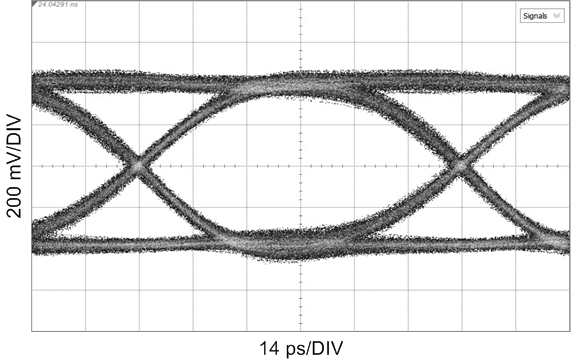

Figure 8. Return Loss (RL) vs Frequency  Figure 5. Output at 11.88 Gbps, Measured at SDI_OUT2+,

Figure 5. Output at 11.88 Gbps, Measured at SDI_OUT2+,

20-in. FR4 Before IN0±

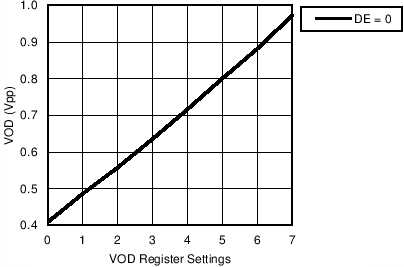

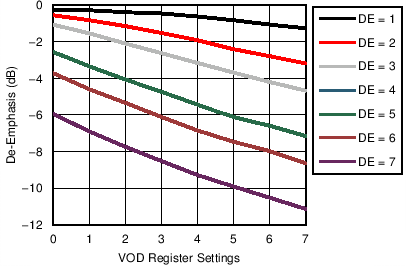

Figure 7. OUT0 De-Emphasis vs. OUT0 VOD and DE

Figure 7. OUT0 De-Emphasis vs. OUT0 VOD and DE

Register Settings