JAJSIA3C February 2010 – December 2019 CSD17308Q3

PRODUCTION DATA.

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- DQG|8

サーマルパッド・メカニカル・データ

発注情報

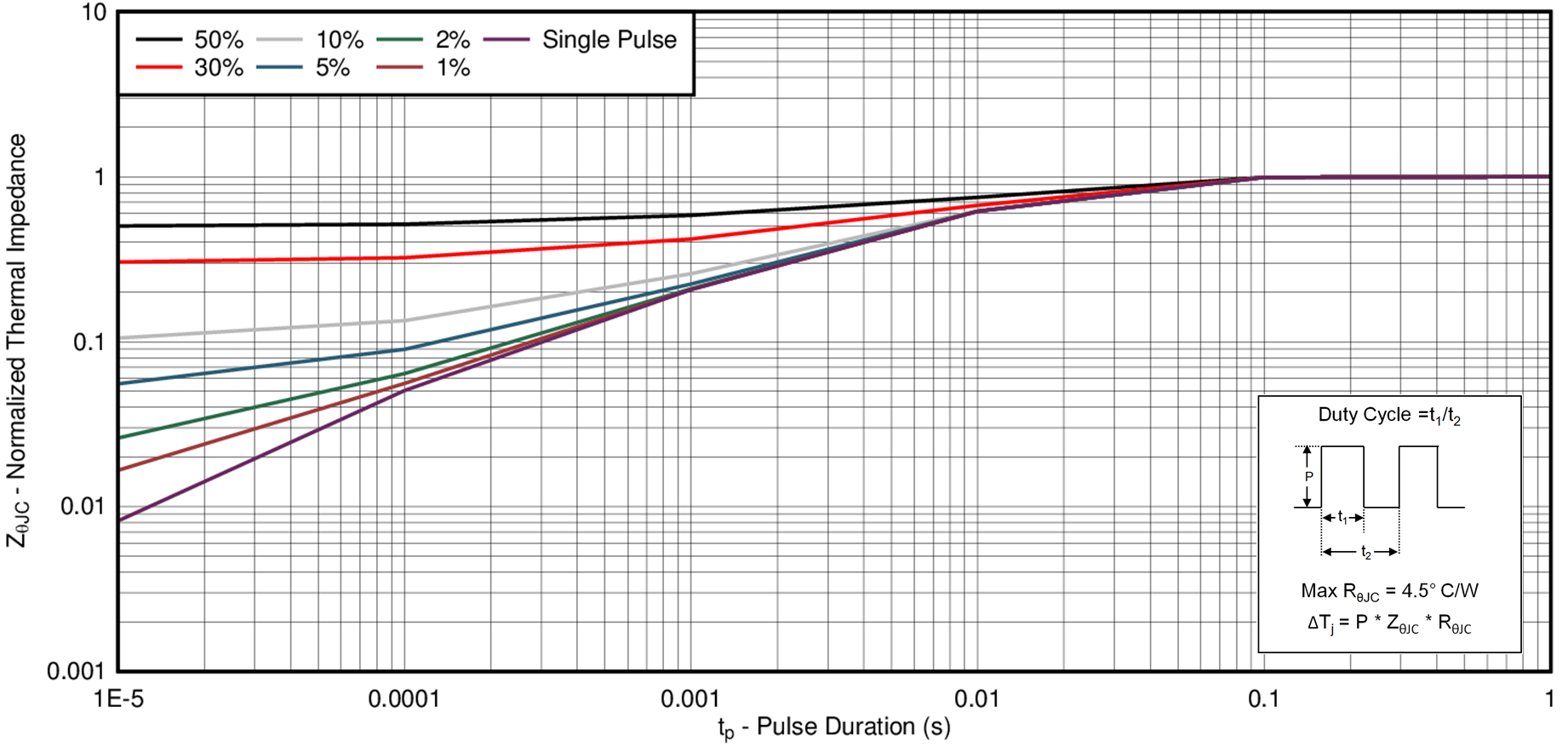

5.3 Typical MOSFET Characteristics

TA = 25°C unless otherwise stated

| VDS = 5 V |

| ID = 10 A | VDS = 15 V |

| ID = 250 µA |

| ID = 10 A |