JAJSLB2D november 2014 – april 2023 DLP9500UV

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 概要 (続き)

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 Storage Conditions

- 7.3 ESD Ratings

- 7.4 Recommended Operating Conditions

- 7.5 Thermal Information

- 7.6 Electrical Characteristics

- 7.7 LVDS Timing Requirements

- 7.8 LVDS Waveform Requirements

- 7.9 Serial Control Bus Timing Requirements

- 7.10 Systems Mounting Interface Loads

- 7.11 Micromirror Array Physical Characteristics

- 7.12 Micromirror Array Optical Characteristics

- 7.13 Chipset Component Usage Specification

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 DLPC410 - Digital Controller for DLP Discovery 4100 Chipset

- 8.3.2 DLPA200 - DMD Micromirror Drivers

- 8.3.3 DLPR410 - PROM for DLP Discovery 4100 Chipset

- 8.3.4 DLP9500 - DLP 0.95 1080p 2xLVDS UV Type-A DMD 1080p DMD

- 8.3.5 Measurement Conditions

- 8.4 Device Functional Modes

- 8.5 Window Characteristics and Optics

- 8.6 Micromirror Array Temperature Calculation

- 8.7 Micromirror Landed-On and Landed-Off Duty Cycle

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

11.2 Layout Example

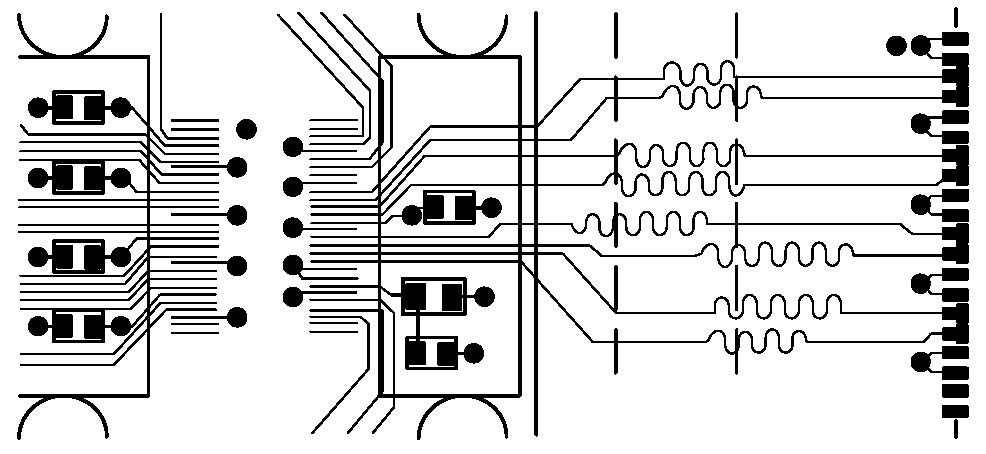

For LVDS (and other differential signal) pairs and groups, it is important to match trace lengths. In the area of the dashed lines, Figure 11-1 shows correct matching of signal pair lengths with serpentine sections to maintain the correct impedance.

Figure 11-1 Mitering LVDS Traces to Match Lengths

Figure 11-1 Mitering LVDS Traces to Match Lengths