JAJU534E october 2022 – july 2023

- 1

- 概要

- リソース

- 特長

- アプリケーション

- 6

- 1システムの説明

- 2システム概要

- 3ハードウェア、ソフトウェア、テスト要件、テスト結果

- 4設計ファイル

- 5関連資料

- 6用語

- 7著者について

- 8改訂履歴

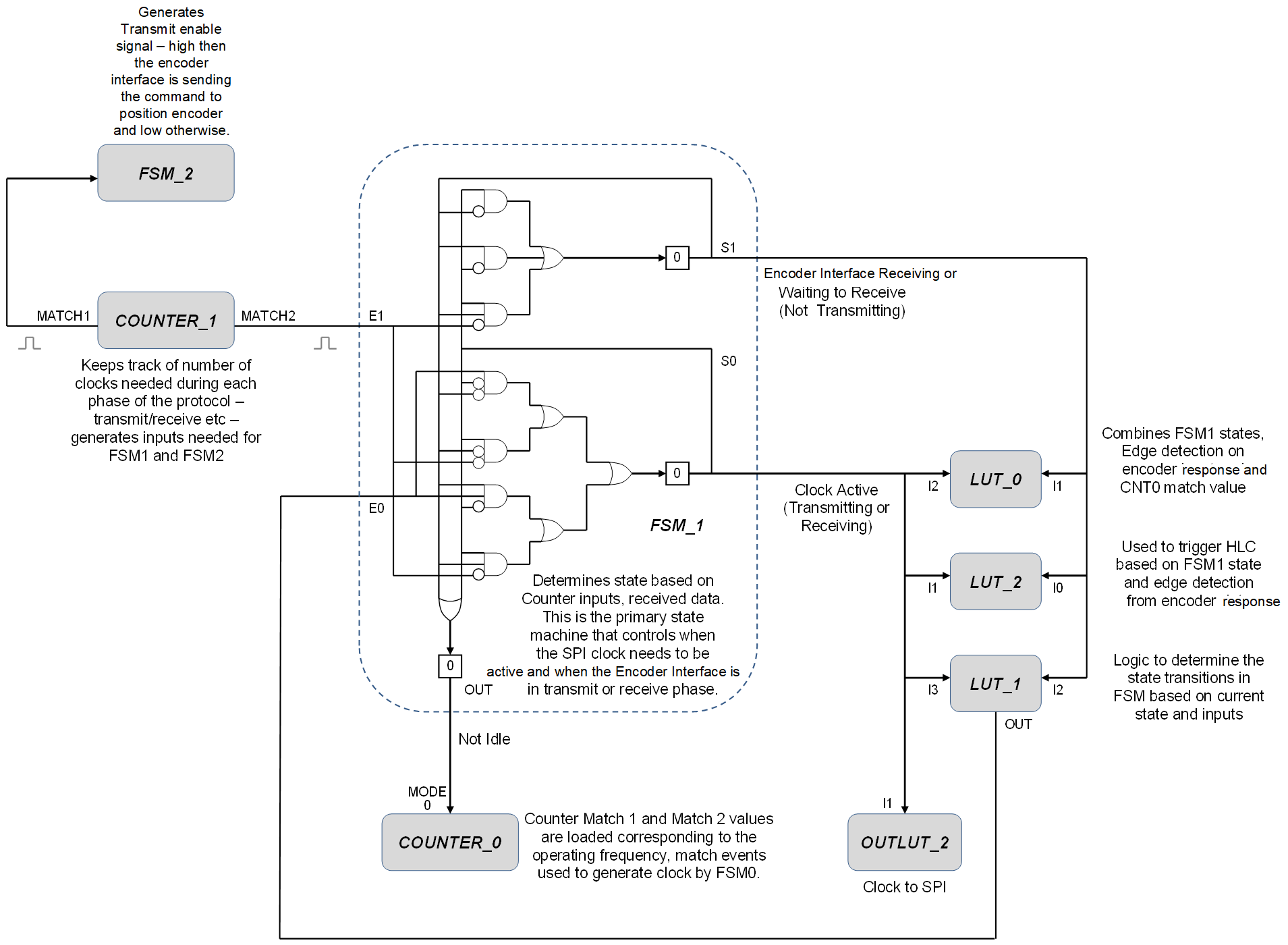

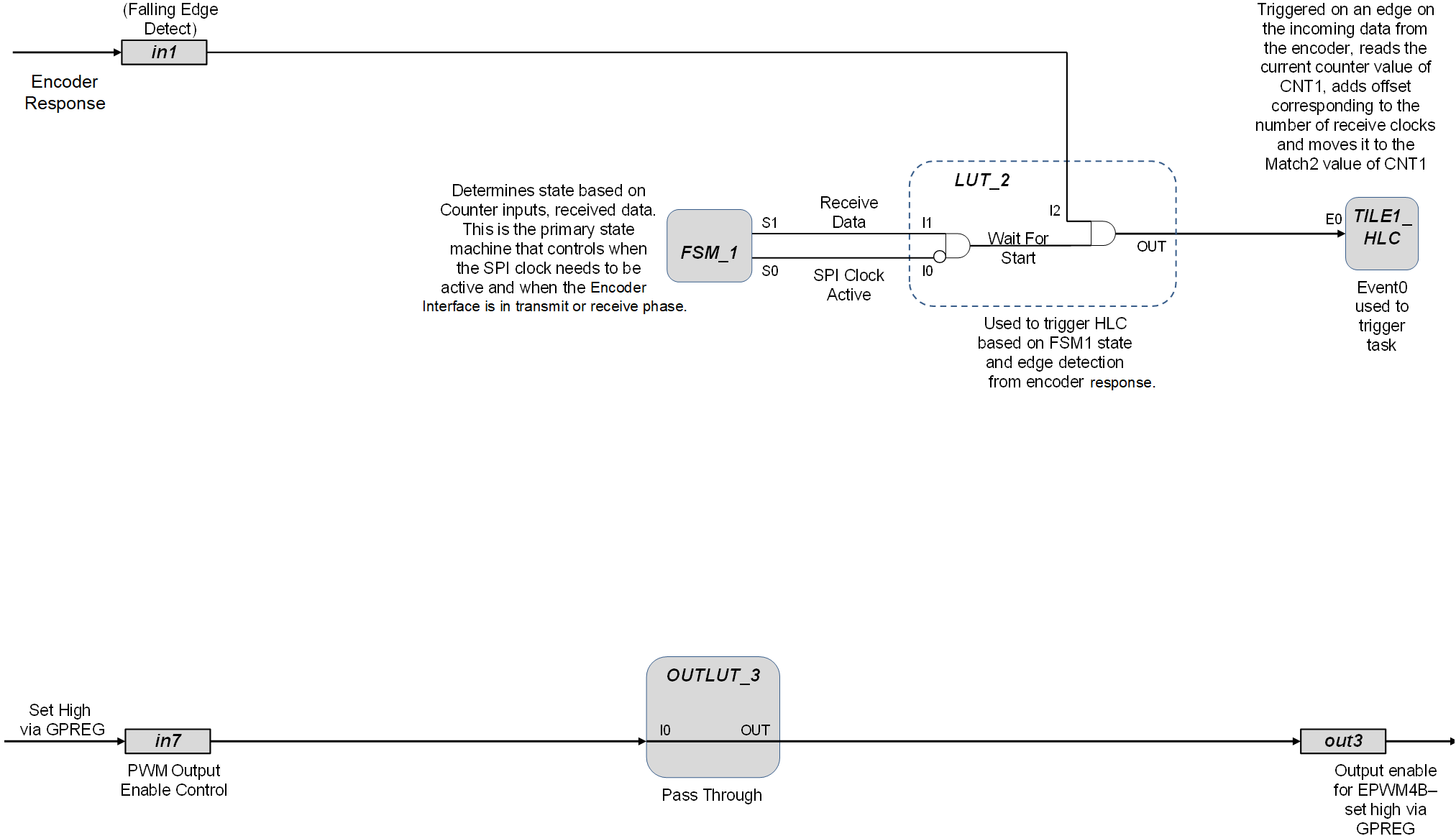

2.3.6.3 ロジック・ビュー

以下の図には、セクション 2.3.6.2 と同じ情報が、ロジック回路図レンズを通して示されています。具体的には次のとおりです。

- 図 2-14 と図 2-15 は、論理ゲートを使用する CLB ブロックの内容を示す。

- 図 2-16 は、このロジックを使用して、メイン・ステート・マシンが他のブロックを制御する方法を示す。

- 図 2-17 は、単純な CLB 出力信号を、入力から、いくつかの関連ロジックを通してトレースする。

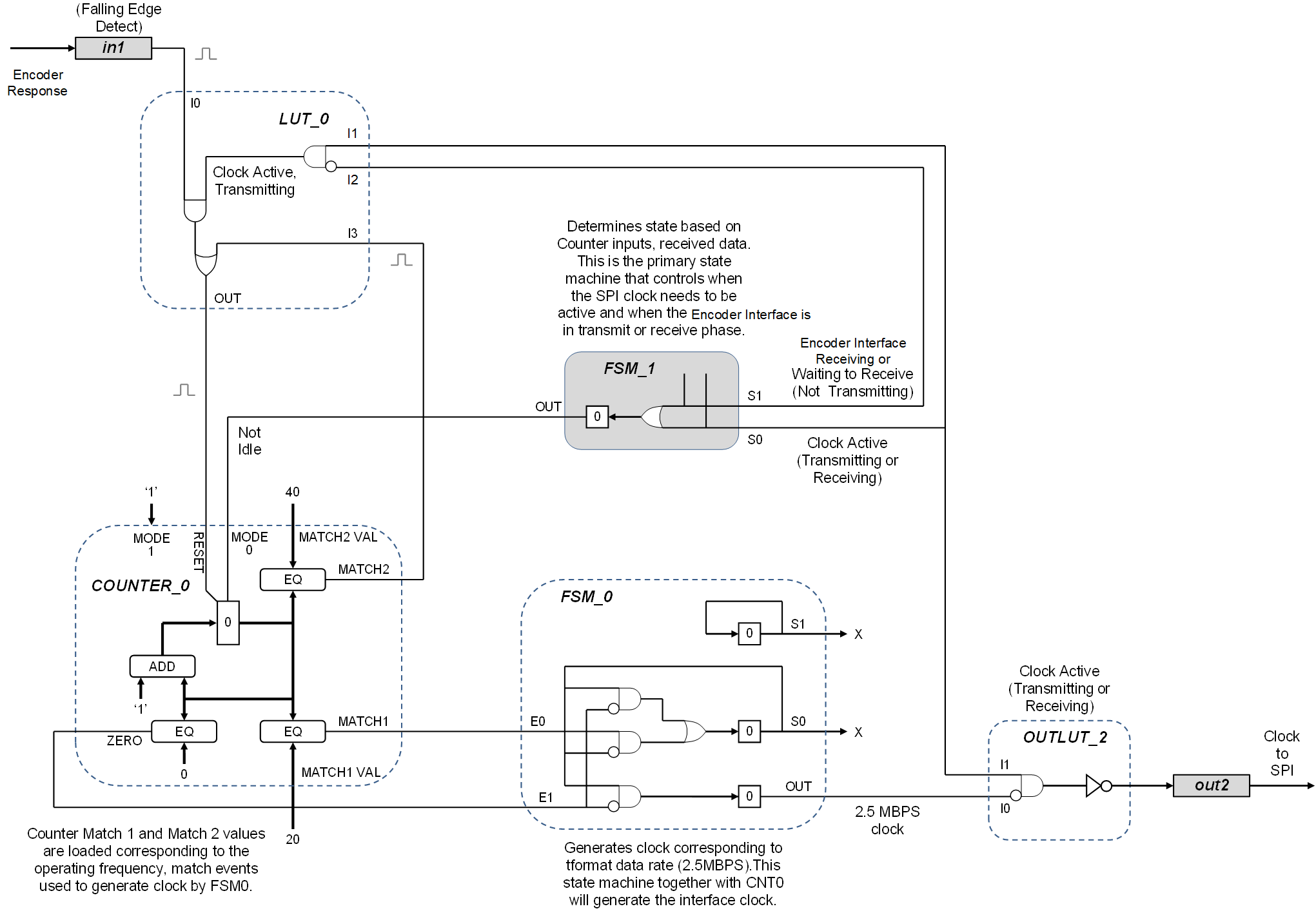

- 図 2-18 は、クロックから SPI への出力を、Input1 から始まって、LUT_0、FSM_0、Counter_0 を通過して Ouput_LUT_0 まで、FSM_1 の 3 つの出力により制御されるものとしてトレースする。

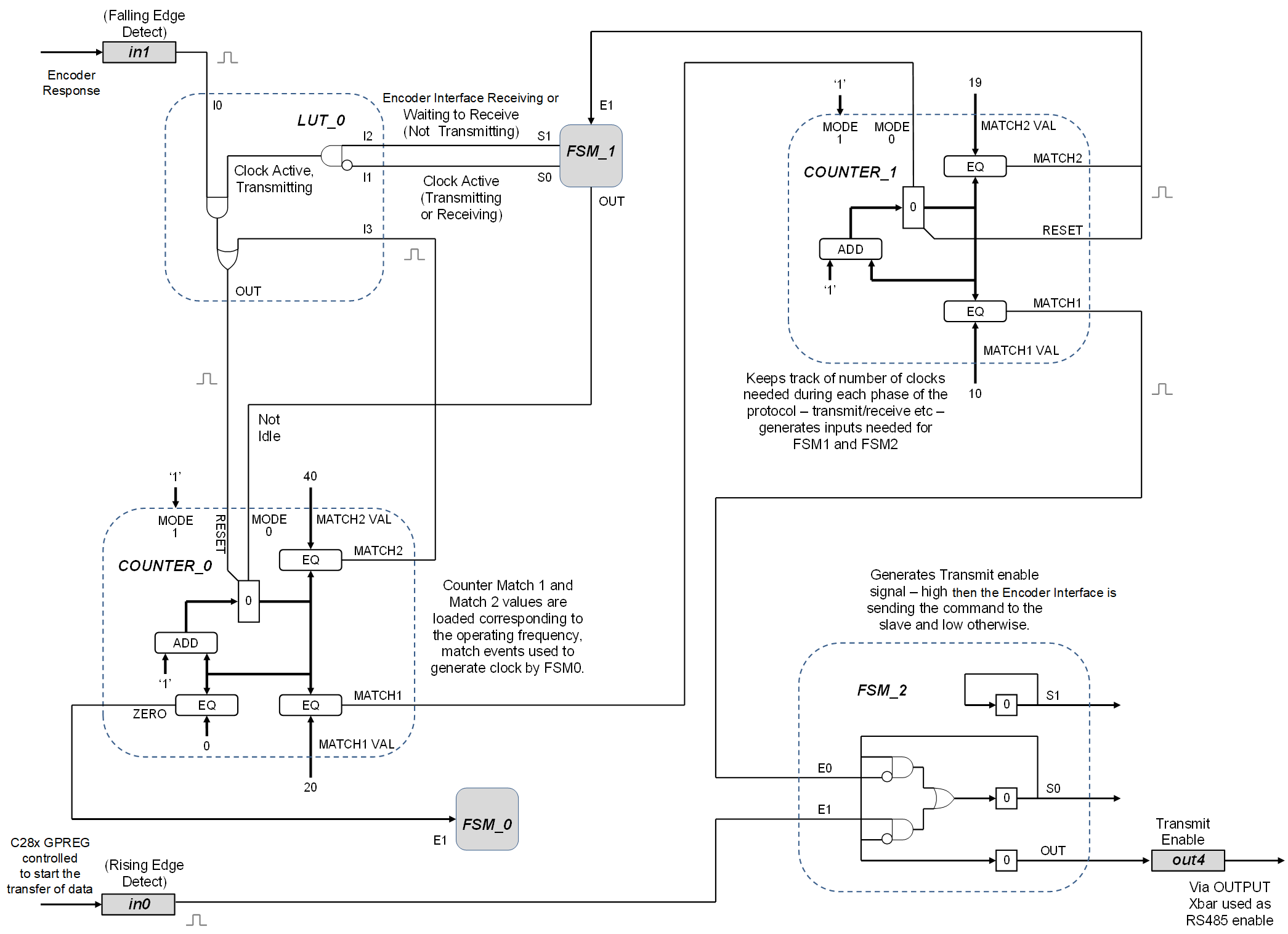

- 図 2-19 は、送信イネーブル出力を、Input0 と Input1 から始まって、LUT_0、Counter_0、Counter1、FSM_2 を通過し、FSM_1 の 3 つの出力で制御されるものとしてトレースする。

図 2-14 LUT、OUTLUT、カウンタ

図 2-14 LUT、OUTLUT、カウンタ 図 2-15 有限ステートマシン

図 2-15 有限ステートマシン 図 2-16 メイン・ステート・マシン

図 2-16 メイン・ステート・マシン 図 2-17 CLB 出力 - HLC Event0 および EPWM 出力イネーブル

図 2-17 CLB 出力 - HLC Event0 および EPWM 出力イネーブル注: EPWM 出力をオーバーライドするのは、F2837xD の設計のみです。

図 2-18 CLB 出力 - クロックから SPI へ

図 2-18 CLB 出力 - クロックから SPI へ 図 2-19 CLB 出力 - RS485 イネーブル

図 2-19 CLB 出力 - RS485 イネーブル