7 Specifications

7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|

MIN |

MAX |

UNIT |

| Supply voltage range, AVDD |

–0.3 |

2.1 |

V |

| Supply voltage range, DVDD |

–0.3 |

2.1 |

V |

| Voltage applied to input pins: |

INAP, INBP, INCP, INDP, INAM, INBM, INCM, INDM |

–0.3 |

Minimum

(AVDD + 0.3, 2.1) |

V |

| CLKP, CLKM(2) |

–0.3 |

Minimum

(AVDD + 0.3, 2.1) |

V |

| SYSREFP, SYSREFM, SYNCP~, SYNCM~ |

–0.3 |

Minimum

(AVDD + 0.3, 2.1) |

V |

| SCLK, SEN, SDATA, RESET, PDN |

–0.3 |

3.6 |

V |

| Temperature range |

Operating free-air, TA |

–40 |

85 |

°C |

| Operating junction, TJ |

|

125 |

°C |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) When AVDD is turned off, TI recommends switching off the input clock (or ensuring the voltage on CLKP, CLKM is less than |0.3 V|). This configuration prevents the ESD protection diodes at the clock input pins from turning on.

7.2 Handling Ratings

|

MIN |

MAX |

UNIT |

| Tstg |

Storage temperature range |

–65 |

150 |

°C |

| V(ESD) |

Electrostatic discharge |

Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins(1) |

|

2 |

kV |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

7.3 Recommended Operating Conditions(2)

over operating free-air temperature range (unless otherwise noted)

|

MIN |

NOM |

MAX |

UNIT |

| SUPPLIES |

| AVDD |

Analog supply voltage range |

1.7 |

1.8 |

1.9 |

V |

| DVDD |

Digital supply voltage range |

1.7 |

1.8 |

1.9 |

V |

| ANALOG INPUT |

| VID |

Differential input voltage |

For input frequencies < 450 MHz |

|

2 |

|

VPP |

| For input frequencies < 600 MHz |

|

1 |

|

VPP |

| VIC |

Input common-mode voltage |

VCM ± 0.025 |

|

V |

| CLOCK INPUT |

|

Input clock frequency |

Sampling clock frequency |

15 |

|

160(1) |

MSPS |

|

Input clock amplitude (differential) |

Sine wave, ac-coupled |

0.2 |

1.5 |

|

V |

| LVPECL, ac-coupled |

|

1.6 |

|

V |

| LVDS, ac-coupled |

|

0.7 |

|

V |

|

Input clock duty cycle |

|

35% |

50% |

65% |

|

|

Input clock common-mode voltage |

|

|

0.95 |

|

V |

| DIGITAL OUTPUTS |

| CLOAD |

Maximum external load capacitance from each output pin to GND |

|

|

3.3 |

|

pF |

| RLOAD |

Single-ended load resistance |

|

|

50 |

|

Ω |

(1) With the clock divider enabled by default for divide-by-1. Maximum sampling clock frequency for the divide-by-4 option is 640 MSPS.

(2) After power-up, to reset the device for the first time, only use the RESET pin; see the

Register Initialization section.

7.4 Summary of Special Mode Registers

Table 1 lists the location, value, and functions of special mode registers in the device.

Table 1. Special Modes Summary

| MODE |

LOCATION |

VALUE AND FUNCTION |

| Dither mode |

DIS DITH CHA |

01h [7:6], 134h[5,3] |

Creates a noise floor cleaner and improves SFDR; see the Internal Dither Algorithm section.

0000 = Dither disabled

1111 = Dither enabled |

| DIS DITH CHB |

01h [5:4], 434h[5,3] |

| DIS DITH CHC |

01h [3:2], 534h[5,3] |

| DIS DITH CHD |

01h [1:0], 234h[5,3] |

| Special mode 1 |

SPECIAL MODE 1 CHA |

06h[4:2] |

Use for better HD3.

000 = Default after reset

010 = Use for frequency < 120 MHz

111 = Use for frequency > 120 MHz |

| SPECIAL MODE 1 CHB |

07h[4:2] |

| SPECIAL MODE 1 CHC |

08h[4:2] |

| SPECIAL MODE 1 CHD |

09h[4:2] |

| Special mode 2 |

SPECIAL MODE 2 CHA |

122h[1:0] |

Helps improve HD2.

00 = Default after reset

11 = Improves HD2 |

| SPECIAL MODE 2 CHB |

422h[1:0] |

| SPECIAL MODE 2 CHC |

522h[1:0] |

| SPECIAL MODE 2 CHD |

222h[1:0] |

7.5 Thermal Information

| THERMAL METRIC(1) |

ADC34J4x |

UNIT |

| RGZ (VQFN) |

| 48 PINS |

| RθJA |

Junction-to-ambient thermal resistance |

25.7 |

°C/W |

| RθJC(top) |

Junction-to-case (top) thermal resistance |

18.9 |

| RθJB |

Junction-to-board thermal resistance |

3.0 |

| ψJT |

Junction-to-top characterization parameter |

0.2 |

| ψJB |

Junction-to-board characterization parameter |

3 |

| RθJC(bot) |

Junction-to-case (bottom) thermal resistance |

0.5 |

(1) For more information about traditional and new thermal metrics, see the

IC Package Thermal Metrics application report,

SPRA953.

7.6 Electrical Characteristics: ADC34J44, ADC34J45

Typical values are at TA = 25°C, full temperature range is TMIN = –40°C to TMAX = 85°C, maximum sampling rate, 50% clock duty cycle, AVDD = DVDD = 1.8 V, and –1-dBFS differential input, unless otherwise noted.

| PARAMETER |

ADC34J44 |

ADC34J45 |

UNIT |

| MIN |

TYP |

MAX |

MIN |

TYP |

MAX |

|

ADC clock frequency |

|

|

125 |

|

|

160 |

MSPS |

|

Resolution |

|

|

14 |

|

|

14 |

Bits |

|

1.8-V analog supply (AVDD) current |

|

318 |

|

|

354 |

490 |

mA |

|

1.8-V digital supply current |

|

79 |

|

|

97 |

150 |

mA |

|

Total power dissipation |

|

715 |

|

|

812 |

1010 |

mW |

|

Global power-down dissipation |

|

22 |

|

|

22 |

|

mW |

|

Wake-up time from global power-down |

|

85 |

|

|

85 |

100 |

µs |

|

Standby power-down dissipation |

|

177 |

|

|

185 |

|

mW |

|

Wake-up time from standby power-down |

|

35 |

|

|

35 |

300 |

µs |

7.7 Electrical Characteristics: ADC34J42, ADC34J43

Typical values are at TA = 25°C, full temperature range is TMIN = –40°C to TMAX = 85°C, maximum sampling rate, 50% clock duty cycle, AVDD = DVDD = 1.8 V, and –1-dBFS differential input, unless otherwise noted.

| PARAMETER |

ADC34J42 |

ADC34J43 |

UNIT |

| MIN |

TYP |

MAX |

MIN |

TYP |

MAX |

|

ADC clock frequency |

|

|

50 |

|

|

80 |

MSPS |

|

Resolution |

|

|

14 |

|

|

14 |

Bits |

|

1.8-V analog supply current |

|

233 |

|

|

269 |

|

mA |

|

1.8-V digital supply current |

|

39 |

|

|

56 |

|

mA |

|

Total power dissipation |

|

491 |

|

|

584 |

|

mW |

|

Global power-down dissipation |

|

22 |

|

|

22 |

|

mW |

|

Wake-up time from global power-down |

|

85 |

|

|

85 |

|

µs |

|

Standby power-down dissipation |

|

155 |

|

|

166 |

|

mW |

|

Wake-up time from standby power-down |

|

35 |

|

|

35 |

|

µs |

7.8 Electrical Characteristics: General

Typical values are at TA = 25°C, full temperature range is TMIN = –40°C to TMAX = 85°C, maximum sampling rate, 50% clock duty cycle, AVDD = DVDD = 1.8 V, and –1-dBFS differential input, unless otherwise noted.

| PARAMETER |

TEST CONDITIONS |

MIN |

TYP |

MAX |

UNIT |

| ANALOG INPUT |

|

Differential input full-scale |

|

|

2.0 |

|

VPP |

| ri |

Input resistance |

Differential at dc |

|

6.5 |

|

kΩ |

| ci |

Input capacitance |

Differential at dc |

|

5.2 |

|

pF |

| VOC(VCM) |

VCM common-mode voltage output |

|

|

0.95 |

|

V |

|

VCM output current capability |

|

|

10 |

|

mA |

|

Input common-mode current |

Per analog input pin |

|

1.5 |

|

µA/MSPS |

|

Analog input bandwidth (3 dB) |

50-Ω differential source driving 50-Ω termination across INP and INM |

|

450 |

|

MHz |

| DC ACCURACY |

| EO |

Offset error |

|

–20 |

|

20 |

mV |

| EG(REF) |

Gain error as a result of internal reference inaccuracy alone |

|

–3 |

|

3 |

%FS |

| EG(CHAN) |

Gain error of channel alone |

|

|

±1 |

|

%FS |

| α(EGCHAN) |

Temperature coefficient of EG(CHAN) |

|

|

–0.017 |

|

Δ%FS/C |

| CHANNEL-TO-CHANNEL ISOLATION |

|

Crosstalk(1) |

fIN = 10 MHz |

Near channel |

|

105 |

|

dB |

| Far channel |

|

105 |

|

dB |

| fIN = 100 MHz |

Near channel |

|

95 |

|

dB |

| Far channel |

|

105 |

|

dB |

| fIN = 200 MHz |

Near channel |

|

94 |

|

dB |

| Far channel |

|

105 |

|

dB |

| fIN = 230 MHz |

Near channel |

|

93 |

|

dB |

| Far channel |

|

105 |

|

dB |

| fIN = 300 MHz |

Near channel |

|

85 |

|

dB |

| Far channel |

|

105 |

|

dB |

(1) Crosstalk is measured with a –1-dBFS input signal on the aggressor channel and no input on the victim channel.

7.9 AC Performance: ADC34J45

Typical values are at TA = 25°C, full temperature range is TMIN = –40°C to TMAX = 85°C, ADC sampling rate = 160 MSPS, 50% clock duty cycle, AVDD = DVDD = 1.8 V, and –1-dBFS differential input, unless otherwise noted.

| PARAMETER |

TEST CONDITIONS |

ADC34J45 (fS = 160 MSPS) |

UNIT |

| DITHER ON |

DITHER OFF |

| MIN |

TYP |

MAX |

MIN |

TYP |

MAX |

| DYNAMIC AC CHARACTERISTICS |

| SNR |

Signal-to-noise ratio |

fIN = 10 MHz |

|

72.4 |

|

|

72.7 |

|

dBFS |

| fIN = 70 MHz |

70.4 |

71.6 |

|

|

72 |

|

| fIN = 100 MHz |

|

70.9 |

|

|

71.3 |

|

| fIN = 170 MHz |

|

69.9 |

|

|

70.4 |

|

| fIN = 230 MHz |

|

68.8 |

|

|

69.5 |

|

| NSD |

Noise spectral density

(averaged across Nyquist zone) |

fIN = 10 MHz |

|

–151.4 |

|

|

–151.7 |

|

dBFS/Hz |

| fIN = 70 MHz |

–149.5 |

–150.6 |

|

|

–151 |

|

| fIN = 100 MHz |

|

–149.9 |

|

|

–150.3 |

|

| fIN = 170 MHz |

|

–148.9 |

|

|

–149.4 |

|

| fIN = 230 MHz |

|

–147.8 |

|

|

–148.5 |

|

| SINAD |

Signal-to-noise and distortion ratio |

fIN = 10 MHz |

|

72.1 |

|

|

72.4 |

|

dBFS |

| fIN = 70 MHz |

69.6 |

71.2 |

|

|

71.6 |

|

| fIN = 100 MHz |

|

70.7 |

|

|

71.1 |

|

| fIN = 170 MHz |

|

69.5 |

|

|

70 |

|

| fIN = 230 MHz |

|

68.4 |

|

|

69 |

|

| ENOB |

Effective number of bits |

fIN = 10 MHz |

|

11.8 |

|

|

11.8 |

|

Bits |

| fIN = 70 MHz |

11.3 |

11.7 |

|

|

11.7 |

|

| fIN = 100 MHz |

|

11.6 |

|

|

11.6 |

|

| fIN = 170 MHz |

|

11.3 |

|

|

11.3 |

|

| fIN = 230 MHz |

|

11.1 |

|

|

11.1 |

|

| SFDR |

Spurious-free dynamic range |

fIN = 10 MHz |

|

88 |

|

|

86 |

|

dBc |

| fIN = 70 MHz |

81 |

86 |

|

|

85 |

|

| fIN = 100 MHz |

|

86 |

|

|

86 |

|

| fIN = 170 MHz |

|

83 |

|

|

83 |

|

| fIN = 230 MHz |

|

80 |

|

|

80 |

|

| HD2 |

Second harmonic distortion |

fIN = 10 MHz |

|

–91 |

|

|

–93 |

|

dBc |

| fIN = 70 MHz |

81 |

–94 |

|

|

–92 |

|

| fIN = 100 MHz |

|

–93 |

|

|

–91 |

|

| fIN = 170 MHz |

|

–83 |

|

|

–83 |

|

| fIN = 230 MHz |

|

–80 |

|

|

–80 |

|

| HD3 |

Third harmonic distortion |

fIN = 10 MHz |

|

–88 |

|

|

–86 |

|

dBc |

| fIN = 70 MHz |

81 |

–86 |

|

|

–85 |

|

| fIN = 100 MHz |

|

–86 |

|

|

–86 |

|

| fIN = 170 MHz |

|

–92 |

|

|

–87 |

|

| fIN = 230 MHz |

|

–85 |

|

|

–82 |

|

Non

HD2, HD3 |

Spurious-free dynamic range (excluding HD2, HD3) |

fIN = 10 MHz |

|

98 |

|

|

95 |

|

dBc |

| fIN = 70 MHz |

87 |

98 |

|

|

94 |

|

| fIN = 100 MHz |

|

96 |

|

|

93 |

|

| fIN = 170 MHz |

|

92 |

|

|

91 |

|

| fIN = 230 MHz |

|

92 |

|

|

90 |

|

| THD |

Total harmonic distortion |

fIN = 10 MHz |

|

–84 |

|

|

–84 |

|

dBc |

| fIN = 70 MHz |

76.5 |

–86 |

|

|

–83 |

|

| fIN = 100 MHz |

|

–84 |

|

|

–84 |

|

| fIN = 170 MHz |

|

–82 |

|

|

–80 |

|

| fIN = 230 MHz |

|

–78 |

|

|

–77 |

|

| IMD3 |

Third-order intermodulation distortion |

fIN1 = 45 MHz,

fIN2 = 50 MHz |

|

93 |

|

|

93 |

|

dBFS |

fIN1 = 185 MHz,

fIN2 = 190 MHz |

|

88 |

|

|

88 |

|

7.10 AC Performance: ADC34J44

Typical values are at TA = 25°C, full temperature range is TMIN = –40°C to TMAX = 85°C, ADC sampling rate = 125 MSPS, 50% clock duty cycle, AVDD = DVDD = 1.8 V, and –1-dBFS differential input, unless otherwise noted.

| PARAMETER |

TEST CONDITIONS |

ADC34J44 (fS = 125 MSPS) |

UNIT |

| DITHER ON |

DITHER OFF |

| MIN |

TYP |

MAX |

MIN |

TYP |

MAX |

| DYNAMIC AC CHARACTERISTICS |

| SNR |

Signal-to-noise ratio |

fIN = 10 MHz |

|

72.5 |

|

|

72.9 |

|

dBFS |

| fIN = 70 MHz |

70.8 |

72.1 |

|

|

72.5 |

|

| fIN = 100 MHz |

|

71.8 |

|

|

72.3 |

|

| fIN = 170 MHz |

|

70.6 |

|

|

71.4 |

|

| fIN = 230 MHz |

|

69.8 |

|

|

70.6 |

|

| NSD |

Noise spectral density

(averaged across Nyquist zone) |

fIN = 10 MHz |

|

–151.5 |

|

|

–151.9 |

|

dBFS/Hz |

| fIN = 70 MHz |

–148.8 |

–151.1 |

|

|

–151.5 |

|

| fIN = 100 MHz |

|

–150.8 |

|

|

–151.3 |

|

| fIN = 170 MHz |

|

–149.6 |

|

|

–150.4 |

|

| fIN = 230 MHz |

|

–148.8 |

|

|

–149.6 |

|

| SINAD |

Signal-to-noise and distortion ratio |

fIN = 10 MHz |

|

72.4 |

|

|

72.8 |

|

dBFS |

| fIN = 70 MHz |

68.6 |

72.1 |

|

|

72.4 |

|

| fIN = 100 MHz |

|

71.7 |

|

|

72.1 |

|

| fIN = 170 MHz |

|

70.4 |

|

|

70.9 |

|

| fIN = 230 MHz |

|

69.4 |

|

|

70.1 |

|

| ENOB |

Effective number of bits |

fIN = 10 MHz |

|

11.9 |

|

|

11.9 |

|

Bits |

| fIN = 70 MHz |

11.1 |

11.7 |

|

|

11.8 |

|

| fIN = 100 MHz |

|

11.7 |

|

|

11.7 |

|

| fIN = 170 MHz |

|

11.4 |

|

|

11.5 |

|

| fIN = 230 MHz |

|

11.1 |

|

|

11.2 |

|

| SFDR |

Spurious-free dynamic range |

fIN = 10 MHz |

|

93 |

|

|

93 |

|

dBc |

| fIN = 70 MHz |

81 |

94 |

|

|

91 |

|

| fIN = 100 MHz |

|

92 |

|

|

92 |

|

| fIN = 170 MHz |

|

83 |

|

|

83 |

|

| fIN = 230 MHz |

|

81 |

|

|

80 |

|

| HD2 |

Second harmonic distortion |

fIN = 10 MHz |

|

–93 |

|

|

–93 |

|

dBc |

| fIN = 70 MHz |

81 |

–94 |

|

|

–94 |

|

| fIN = 100 MHz |

|

–92 |

|

|

–92 |

|

| fIN = 170 MHz |

|

–83 |

|

|

–83 |

|

| fIN = 230 MHz |

|

–81 |

|

|

–80 |

|

| HD3 |

Third harmonic distortion |

fIN = 10 MHz |

|

–95 |

|

|

–94 |

|

dBc |

| fIN = 70 MHz |

83 |

–94 |

|

|

–91 |

|

| fIN = 100 MHz |

|

–95 |

|

|

–93 |

|

| fIN = 170 MHz |

|

–88 |

|

|

–85 |

|

| fIN = 230 MHz |

|

–90 |

|

|

–90 |

|

Non

HD2, HD3 |

Spurious-free dynamic range (excluding HD2, HD3) |

fIN = 10 MHz |

|

99 |

|

|

96 |

|

dBc |

| fIN = 70 MHz |

87 |

98 |

|

|

95 |

|

| fIN = 100 MHz |

|

98 |

|

|

95 |

|

| fIN = 170 MHz |

|

97 |

|

|

92 |

|

| fIN = 230 MHz |

|

96 |

|

|

93 |

|

| THD |

Total harmonic distortion |

fIN = 10 MHz |

|

–89 |

|

|

–87 |

|

dBc |

| fIN = 70 MHz |

76.5 |

–89 |

|

|

–87 |

|

| fIN = 100 MHz |

|

–88 |

|

|

–86 |

|

| fIN = 170 MHz |

|

–82 |

|

|

–80 |

|

| fIN = 230 MHz |

|

–80 |

|

|

–79 |

|

| IMD3 |

Third-order intermodulation distortion |

fIN1 = 45 MHz,

fIN2 = 50 MHz |

|

92 |

|

|

92 |

|

dBFS |

fIN1 = 185 MHz,

fIN2 = 190 MHz |

|

90 |

|

|

90 |

|

7.11 AC Performance: ADC34J43

Typical values are at TA = 25°C, full temperature range is TMIN = –40°C to TMAX = 85°C, ADC sampling rate = 80 MSPS, 50% clock duty cycle, AVDD = DVDD = 1.8 V, and –1-dBFS differential input, unless otherwise noted.

| PARAMETER |

TEST CONDITIONS |

ADC34J43 (fS = 80 MSPS) |

UNIT |

| DITHER ON |

DITHER OFF |

| MIN |

TYP |

MAX |

MIN |

TYP |

MAX |

| DYNAMIC AC CHARACTERISTICS |

| SNR |

Signal-to-noise ratio |

fIN = 10 MHz |

|

72.3 |

|

|

72.8 |

|

dBFS |

| fIN = 70 MHz |

70.7 |

72 |

|

|

72.4 |

|

| fIN = 100 MHz |

|

71.7 |

|

|

72.1 |

|

| fIN = 170 MHz |

|

70.9 |

|

|

71.3 |

|

| fIN = 230 MHz |

|

70.1 |

|

|

70.5 |

|

| NSD |

Noise spectral density

(averaged across Nyquist zone) |

fIN = 10 MHz |

|

–151.3 |

|

|

–151.8 |

|

dBFS/Hz |

| fIN = 70 MHz |

–146.8 |

–151 |

|

|

–151.4 |

|

| fIN = 100 MHz |

|

–150.7 |

|

|

–151.1 |

|

| fIN = 170 MHz |

|

–149.9 |

|

|

–150.3 |

|

| fIN = 230 MHz |

|

–149.1 |

|

|

–149.5 |

|

| SINAD |

Signal-to-noise and distortion ratio |

fIN = 10 MHz |

|

72.3 |

|

|

72.6 |

|

dBFS |

| fIN = 70 MHz |

68.6 |

71.9 |

|

|

72.2 |

|

| fIN = 100 MHz |

|

71.6 |

|

|

71.9 |

|

| fIN = 170 MHz |

|

70.6 |

|

|

70.9 |

|

| fIN = 230 MHz |

|

69.6 |

|

|

69.9 |

|

| ENOB |

Effective number of bits |

fIN = 10 MHz |

|

11.8 |

|

|

11.8 |

|

Bits |

| fIN = 70 MHz |

11.1 |

11.8 |

|

|

11.9 |

|

| fIN = 100 MHz |

|

11.7 |

|

|

11.7 |

|

| fIN = 170 MHz |

|

11.4 |

|

|

11.4 |

|

| fIN = 230 MHz |

|

11.2 |

|

|

11.2 |

|

| SFDR |

Spurious-free dynamic range |

fIN= 10 MHz |

|

94 |

|

|

94 |

|

dBc |

| fIN = 70 MHz |

82 |

94 |

|

|

94 |

|

| fIN = 100 MHz |

|

89 |

|

|

91 |

|

| fIN = 170 MHz |

|

83 |

|

|

83 |

|

| fIN = 230 MHz |

|

80 |

|

|

81 |

|

| HD2 |

Second harmonic distortion |

fIN = 10 MHz |

|

–94 |

|

|

–94 |

|

dBc |

| fIN = 70 MHz |

82 |

–94 |

|

|

–94 |

|

| fIN = 100 MHz |

|

–91 |

|

|

–91 |

|

| fIN = 170 MHz |

|

–83 |

|

|

–83 |

|

| fIN = 230 MHz |

|

–80 |

|

|

–81 |

|

| HD3 |

Third harmonic distortion |

fIN = 10 MHz |

|

–99 |

|

|

–94 |

|

dBc |

| fIN = 70 MHz |

83 |

–99 |

|

|

–95 |

|

| fIN = 100 MHz |

|

–99 |

|

|

–89 |

|

| fIN = 170 MHz |

|

–99 |

|

|

–90 |

|

| fIN = 230 MHz |

|

–99 |

|

|

–83 |

|

Non

HD2, HD3 |

Spurious-free dynamic range (excluding HD2, HD3) |

fIN = 10 MHz |

|

98 |

|

|

92 |

|

dBc |

| fIN = 70 MHz |

87 |

98 |

|

|

92 |

|

| fIN = 100 MHz |

|

97 |

|

|

92 |

|

| fIN = 170 MHz |

|

95 |

|

|

91 |

|

| fIN = 230 MHz |

|

94 |

|

|

91 |

|

| THD |

Total harmonic distortion |

fIN = 10 MHz |

|

–91 |

|

|

–86 |

|

dBc |

| fIN = 70 MHz |

76.5 |

–91 |

|

|

–86 |

|

| fIN = 100 MHz |

|

–87 |

|

|

–84 |

|

| fIN = 170 MHz |

|

–82 |

|

|

–81 |

|

| fIN = 230 MHz |

|

–78 |

|

|

–78 |

|

| IMD3 |

Third-order intermodulation distortion |

fIN1 = 45 MHz,

fIN2 = 50 MHz |

|

94 |

|

|

94 |

|

dBFS |

fIN1 = 185 MHz,

fIN2 = 190 MHz |

|

89 |

|

|

89 |

|

7.12 AC Performance: ADC34J42

Typical values are at TA = 25°C, full temperature range is TMIN = –40°C to TMAX = 85°C, ADC sampling rate = 50 MSPS, 50% clock duty cycle, AVDD = DVDD = 1.8 V, and –1-dBFS differential input, unless otherwise noted.

| PARAMETER |

TEST CONDITIONS |

ADC34J42 (fS = 50 MSPS) |

UNIT |

| DITHER ON |

DITHER OFF |

| MIN |

TYP |

MAX |

MIN |

TYP |

MAX |

| DYNAMIC AC CHARACTERISTICS |

| SNR |

Signal-to-noise ratio |

fIN = 10 MHz |

70.7 |

72.4 |

|

|

72.8 |

|

dBFS |

| fIN = 70 MHz |

|

72 |

|

|

72.4 |

|

| fIN = 100 MHz |

|

71.9 |

|

|

72.2 |

|

| fIN = 170 MHz |

|

71 |

|

|

71.3 |

|

| fIN = 230 MHz |

|

69.9 |

|

|

70.1 |

|

| NSD |

Noise spectral density

(averaged across Nyquist zone) |

fIN = 10 MHz |

–145.9 |

–151.4 |

|

|

–151.8 |

|

dBFS/Hz |

| fIN = 70 MHz |

|

–151 |

|

|

–151.4 |

|

| fIN = 100 MHz |

|

–150.9 |

|

|

–151.2 |

|

| fIN = 170 MHz |

|

–150 |

|

|

–150.3 |

|

| fIN = 230 MHz |

|

–148.9 |

|

|

–149.1 |

|

| SINAD |

Signal-to-noise and distortion ratio |

fIN = 10 MHz |

68.6 |

72.2 |

|

|

72.6 |

|

dBFS |

| fIN = 70 MHz |

|

71.9 |

|

|

72.2 |

|

| fIN = 100 MHz |

|

71.7 |

|

|

71.9 |

|

| fIN = 170 MHz |

|

70.7 |

|

|

70.9 |

|

| fIN = 230 MHz |

|

69.4 |

|

|

69.5 |

|

| ENOB |

Effective number of bits |

fIN = 10 MHz |

11.1 |

11.8 |

|

|

11.9 |

|

Bits |

| fIN = 70 MHz |

|

11.7 |

|

|

11.7 |

|

| fIN = 100 MHz |

|

11.7 |

|

|

11.8 |

|

| fIN = 170 MHz |

|

11.4 |

|

|

11.4 |

|

| fIN = 230 MHz |

|

11.1 |

|

|

11.1 |

|

| SFDR |

Spurious-free dynamic range |

fIN = 10 MHz |

82 |

93 |

|

|

92 |

|

dBc |

| fIN = 70 MHz |

|

93 |

|

|

92 |

|

| fIN = 100 MHz |

|

90 |

|

|

89 |

|

| fIN = 170 MHz |

|

83 |

|

|

83 |

|

| fIN = 230 MHz |

|

80 |

|

|

80 |

|

| HD2 |

Second harmonic distortion |

fIN = 10 MHz |

82 |

–93 |

|

|

–92 |

|

dBc |

| fIN = 70 MHz |

|

–93 |

|

|

–96 |

|

| fIN = 100 MHz |

|

–90 |

|

|

–90 |

|

| fIN = 170 MHz |

|

–83 |

|

|

–83 |

|

| fIN = 230 MHz |

|

–80 |

|

|

–80 |

|

| HD3 |

Third harmonic distortion |

fIN = 10 MHz |

83 |

–94 |

|

|

–93 |

|

dBc |

| fIN = 70 MHz |

|

–94 |

|

|

–92 |

|

| fIN = 100 MHz |

|

–91 |

|

|

–89 |

|

| fIN = 170 MHz |

|

–91 |

|

|

–90 |

|

| fIN = 230 MHz |

|

–84 |

|

|

–83 |

|

Non

HD2, HD3 |

Spurious-free dynamic range (excluding HD2, HD3) |

fIN = 10 MHz |

87 |

98 |

|

|

92 |

|

dBc |

| fIN = 70 MHz |

|

98 |

|

|

92 |

|

| fIN = 100 MHz |

|

96 |

|

|

92 |

|

| fIN = 170 MHz |

|

96 |

|

|

91 |

|

| fIN = 230 MHz |

|

96 |

|

|

91 |

|

| THD |

Total harmonic distortion |

fIN = 10 MHz |

76.5 |

–91 |

|

|

–85 |

|

dBc |

| fIN = 70 MHz |

|

–89 |

|

|

–85 |

|

| fIN = 100 MHz |

|

–86 |

|

|

–84 |

|

| fIN = 170 MHz |

|

–82 |

|

|

–81 |

|

| fIN = 230 MHz |

|

–78 |

|

|

–78 |

|

| IMD3 |

Third-order intermodulation distortion |

fIN1 = 45 MHz,

fIN2 = 50 MHz |

|

93 |

|

|

93 |

|

dBFS |

fIN1 = 185 MHz,

fIN2 = 190 MHz |

|

86 |

|

|

86 |

|

7.13 Digital Characteristics

The dc specifications refer to the condition where the digital outputs are not switching, but are permanently at a valid logic level 0 or 1. AVDD = DVDD = 1.8 V and –1-dBFS differential input, unless otherwise noted.

| PARAMETER |

TEST CONDITIONS |

MIN |

TYP |

MAX |

UNITS |

| DIGITAL INPUTS (RESET, SCLK, SEN, SDATA, PDN)(1) |

| VIH |

High-level input voltage |

All digital inputs support 1.8-V and 3.3-V logic levels |

1.2 |

|

|

V |

| VIL |

Low-level input voltage |

All digital inputs support 1.8-V and 3.3-V logic levels |

|

|

0.4 |

V |

| IIH |

High-level input current |

SEN |

|

0 |

|

µA |

| RESET, SCLK, SDATA, PDN |

|

10 |

|

µA |

| IIL |

Low-level input current |

SEN |

|

10 |

|

µA |

| RESET, SCLK, SDATA, PDN |

|

0 |

|

µA |

| DIGITAL INPUTS (SYNCP~, SYNCM~, SYSREFP, SYSREFM) |

| VIH |

High-level input voltage |

|

|

1.3 |

|

V |

| VIL |

Low-level input voltage |

|

|

0.5 |

|

V |

| V(CM_DIG) |

Common-mode voltage for SYNC~ and SYSREF |

|

|

0.9 |

|

V |

| DIGITAL OUTPUTS (SDOUT, OVRA, OVRB, OVRC, OVRD) |

| VOH |

High-level output voltage |

|

DVDD – 0.1 |

DVDD |

|

V |

| VOL |

Low-level output voltage |

|

|

|

0.1 |

V |

| DIGITAL OUTPUTS (JESD204B Interface: DxP, DxM)(2) |

| VOH |

High-level output voltage |

|

|

DVDD |

|

V |

| VOL |

Low-level output voltage |

|

DVDD – 0.4 |

|

V |

| VOD |

Output differential voltage |

|

|

0.4 |

|

V |

| VOC |

Output common-mode voltage |

|

DVDD – 0.2 |

|

V |

|

Transmitter short-circuit current |

Transmitter pins shorted to any voltage between –0.25 V and 1.45 V |

–100 |

|

100 |

mA |

| zos |

Single-ended output impedance |

|

|

50 |

|

Ω |

|

Output capacitance |

Output capacitance inside the device,

from either output to ground |

|

2 |

|

pF |

(1) RESET, SCLK, SDATA, and PDN pins have 150-kΩ (typical) internal pull-down resistor to ground, while SEN pin has 150-kΩ (typical) pull-up resistor to AVDD.

(2) 50-Ω, single-ended external termination to 1.8 V.

7.14 Timing Characteristics

Typical values are at 25°C, AVDD = DVDD = 1.8 V, and –1-dBFS differential input, unless otherwise noted. Minimum and maximum values are across the full temperature range: TMIN = –40°C to TMAX = 85°C. See Figure 143.

| PARAMETER |

TEST CONDITIONS |

MIN |

TYP |

MAX |

UNITS |

| SAMPLE TIMING CHARACTERISTICS |

|

Aperture delay |

|

0.85 |

1.25 |

1.65 |

ns |

|

Aperture delay matching |

Between four channels on the same device |

|

±70 |

|

ps |

| Between two devices at the same temperature and supply voltage |

|

±150 |

|

ps |

|

Aperture jitter |

|

|

200 |

|

fS rms |

|

Wake-up time |

Time to valid data after coming out of STANDBY mode |

|

35 |

100 |

µs |

| Time to valid data after coming out of global power-down |

|

85 |

300 |

µs |

| tSU_SYNC~ |

Setup time for SYNC~ |

Referenced to input clock rising edge |

1 |

|

|

ns |

| tH_SYNC~ |

Hold time for SYNC~ |

Referenced to input clock rising edge |

100 |

|

|

ps |

| tSU_SYSREF |

Setup time for SYSREF |

Referenced to input clock rising edge |

1 |

|

|

ns |

| tH_SYSREF |

Hold time for SYSREF |

Referenced to input clock rising edge |

100 |

|

|

ps |

| CML OUTPUT TIMING CHARACTERISTICS |

|

Unit interval |

|

312.5 |

|

1667 |

ps |

|

Serial output data rate |

|

|

|

3.2 |

Gbps |

|

Total jitter |

3.125 Gbps (20x mode, fS = 156.25 MSPS) |

|

0.3 |

|

P-PUI |

| tR, tF |

Data rise time,

data fall time |

Rise and fall times measured from 20% to 80%,

differential output waveform,

600 Mbps ≤ bit rate ≤ 3.125 Gbps |

|

105 |

|

ps |

Table 2. Latency in Different Modes(1)(2)

| MODE |

PARAMETER |

LATENCY (N Cycles) |

TYPICAL DATA DELAY (tD, ns) |

| 20x |

ADC latency |

17 |

0.29 × tS + 3 |

| Normal OVR latency |

9 |

0.5 × tS + 2 |

| Fast OVR latency |

7 |

0.5 × tS + 2 |

| From SYNC~ falling edge to CGS phase(3) |

15 |

0.3 × tS + 4 |

| From SYNC~ rising edge to ILA sequence(4) |

17 |

0.3 × tS + 4 |

| 40x |

ADC latency |

16 |

0.85 × tS + 3.9 |

| Normal OVR latency |

9 |

0.5 × tS + 2 |

| Fast OVR latency |

7 |

0.5 × tS + 2 |

| From SYNC~ falling edge to CGS phase(3) |

14 |

0.9 × tS + 4 |

| From SYNC~ rising edge to ILA sequence(4) |

12 |

0.9 × tS + 4 |

(1) Overall latency = latency + tD.

(2) tS is the time period of the ADC conversion clock.

(3) Latency is specified for subclass 2. In subclass 0, the SYNC~ falling edge to CGS phase latency is 16 clock cycles in 10x mode and 15 clock cycles in 20x mode.

(4) Latency is specified for subclass 2. In subclass 0, the SYNC~ rising edge to ILA sequence latency is 11 clock cycles in 10x mode and 11 clock cycles in 20x mode.

7.15 Typical Characteristics: ADC34J45

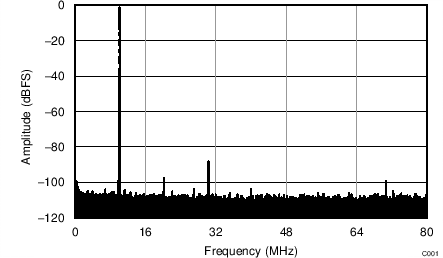

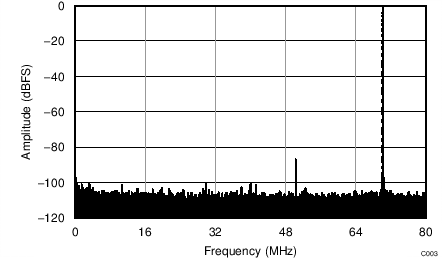

Typical values are at TA= 25°C, ADC sampling rate = 160 MSPS, 50% clock duty cycle, AVDD = DVDD = 1.8 V, –1-dBFS differential input, 2-VPP full-scale, and 32k-point FFT, Dither enable, special modes written, unless otherwise noted.

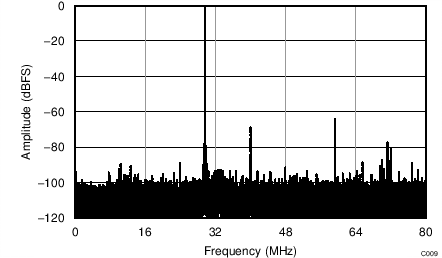

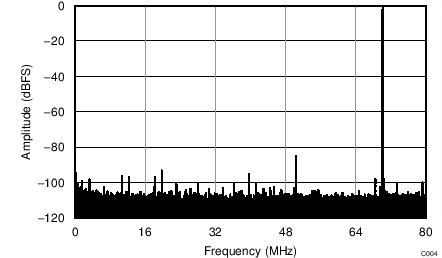

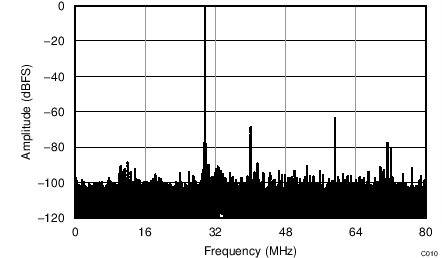

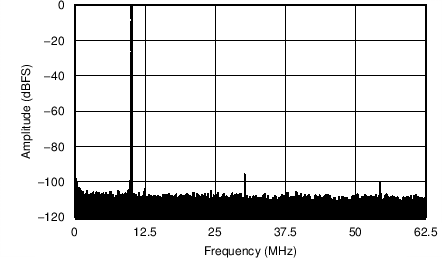

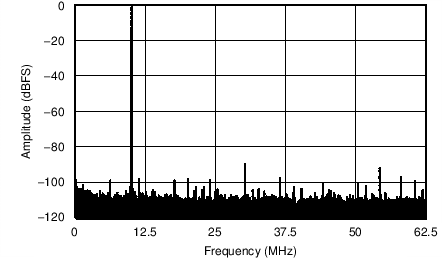

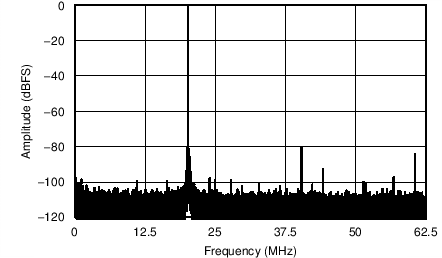

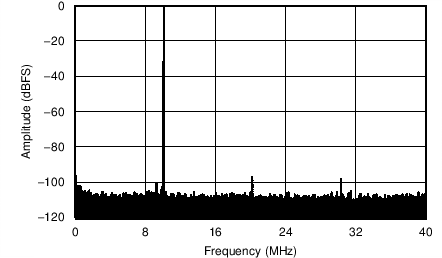

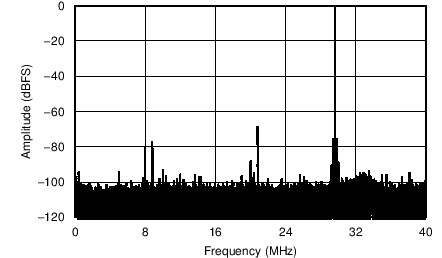

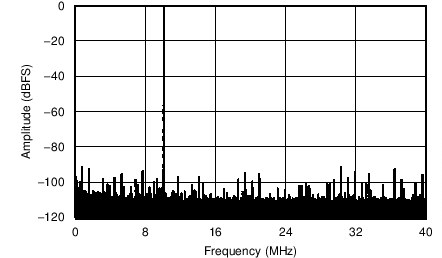

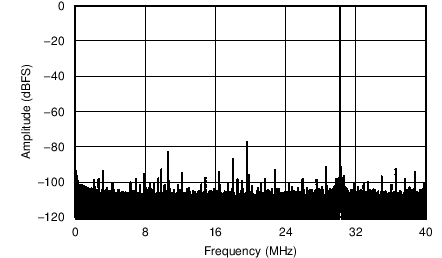

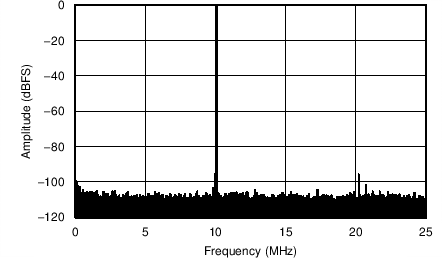

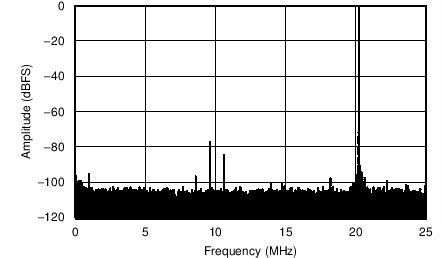

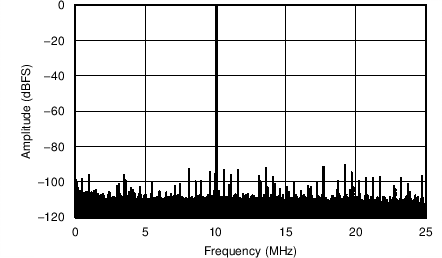

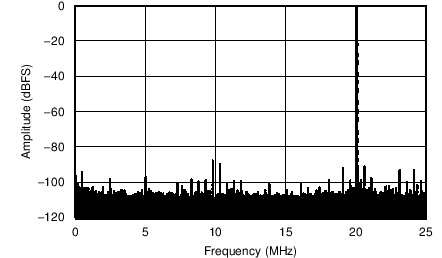

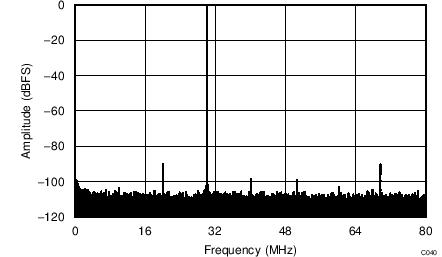

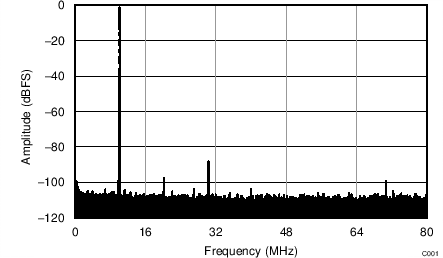

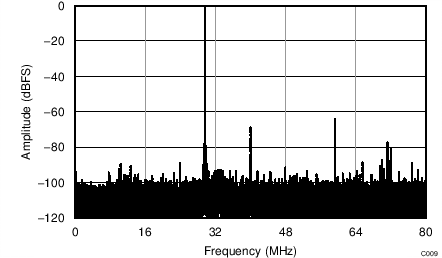

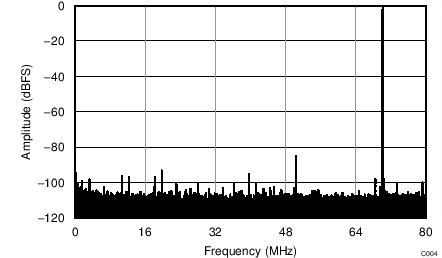

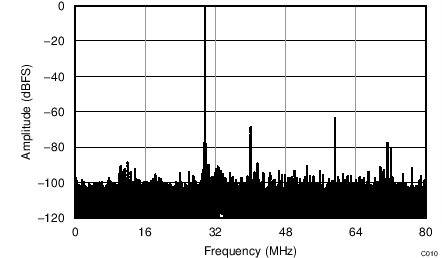

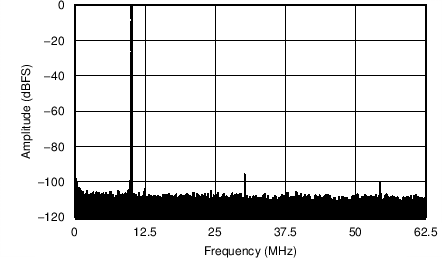

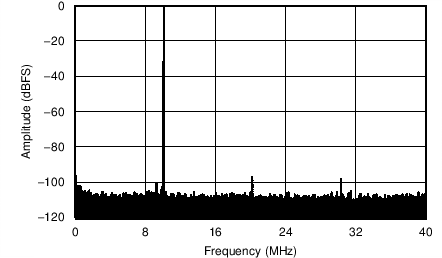

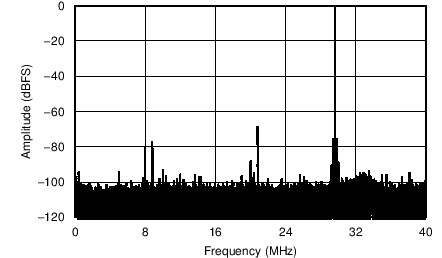

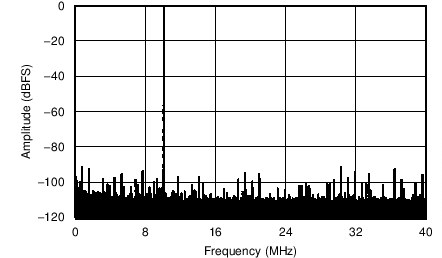

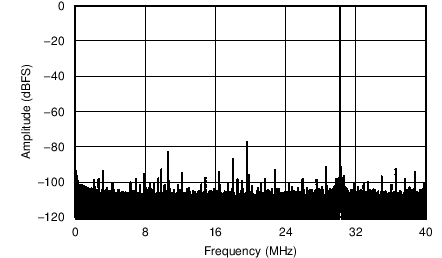

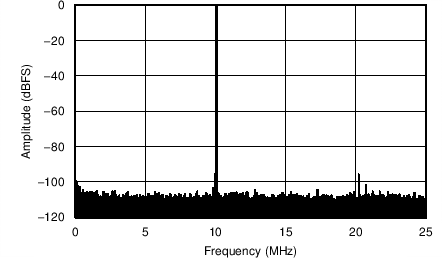

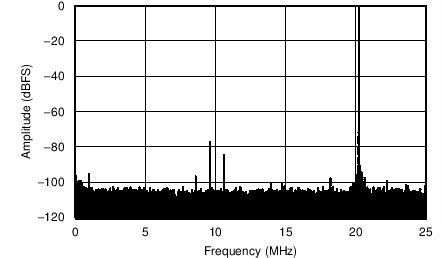

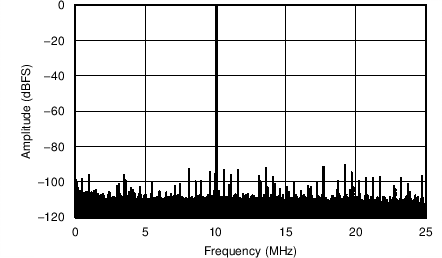

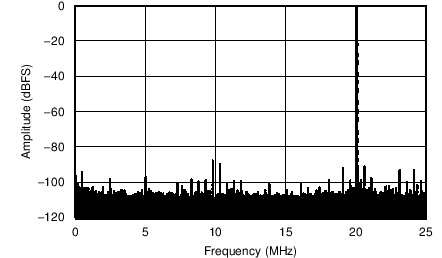

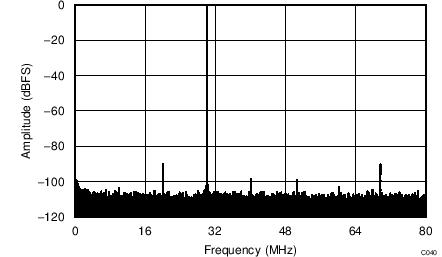

| fS = 160 MSPS, SNR = 72.5 dBFS, fIN = 10 MHz, SFDR = 88 dBc |

Figure 1. FFT for 10-MHz Input signal, Dither On

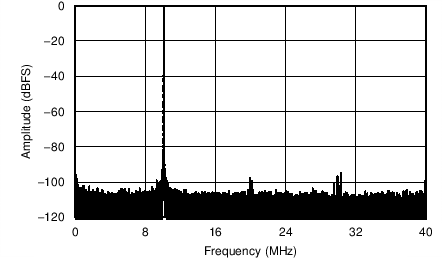

| fS = 160 MSPS, SNR = 71.4 dBFS, fIN = 70 MHz, SFDR = 86 dBc |

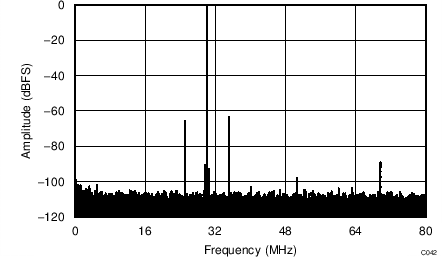

Figure 3. FFT for 70-MHz Input Signal, Dither On

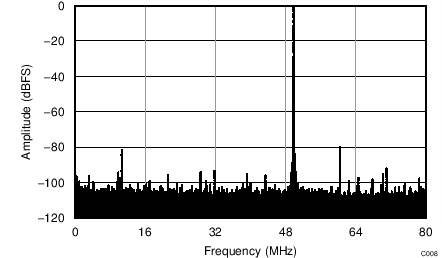

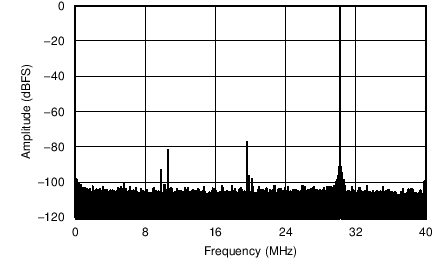

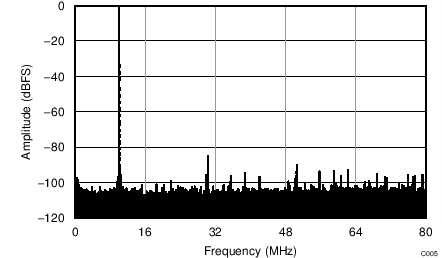

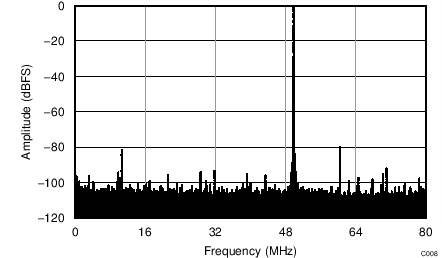

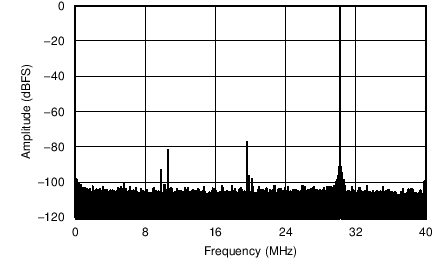

fS = 160 MSPS, SNR = 69.7 dBFS, fIN = 170 MHz,

SFDR = 83 dBc |

Figure 5. FFT for 170-MHz Input Signal, Dither On

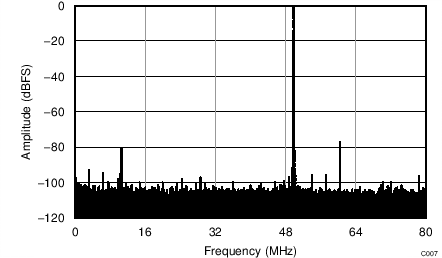

fS = 160 MSPS, SNR = 68.2 dBFS, fIN = 270 MHz,

SFDR = 76 dBc |

Figure 7. FFT for 270-MHz Input Signal, Dither On

fS = 160 MSPS, SNR = 63.3 dBFS, fIN = 450 MHz,

SFDR = 64 dBc |

Figure 9. FFT for 450-MHz Input Signal, Dither On

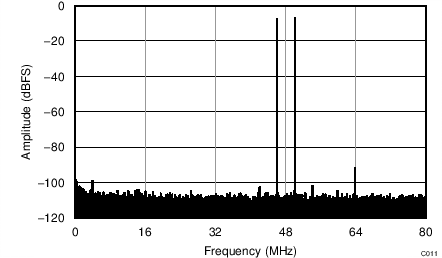

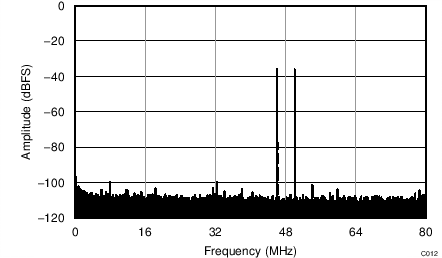

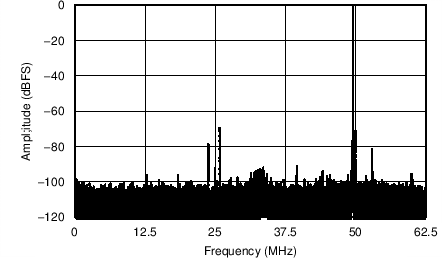

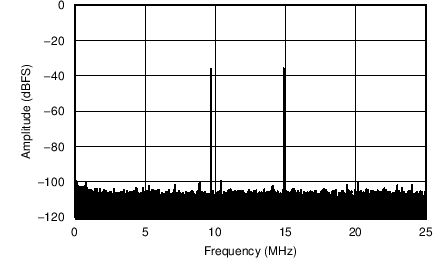

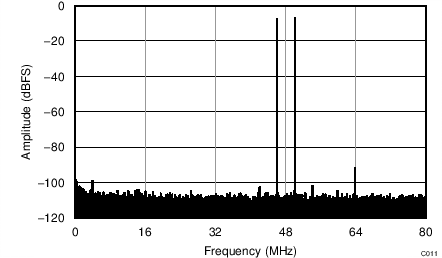

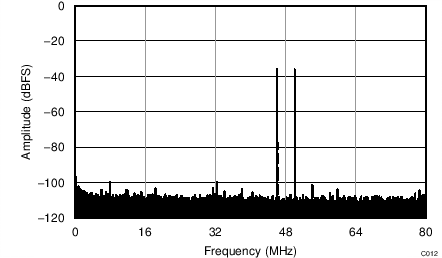

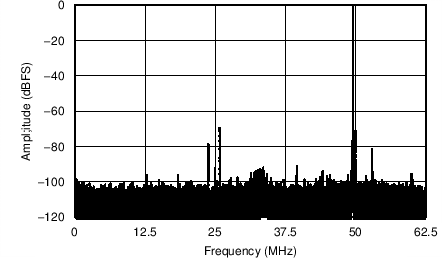

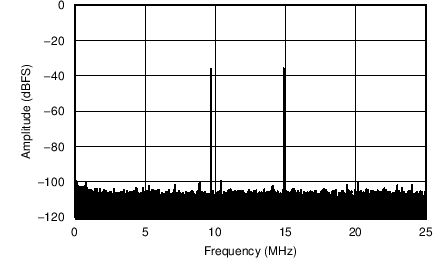

| fS = 160 MSPS, IMD = 92 dBFS, fIN1 = 46 MHz, fIN2 = 50 MHz, SFDR = 99 dBFS |

Figure 11. FFT for Two-Tone Input Signal

(–7 dBFS at 46 MHz and 50 MHz)

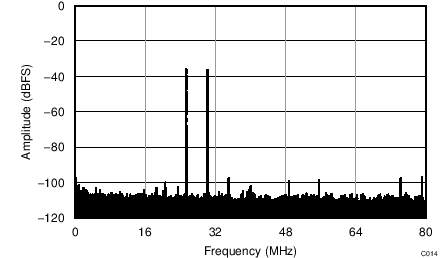

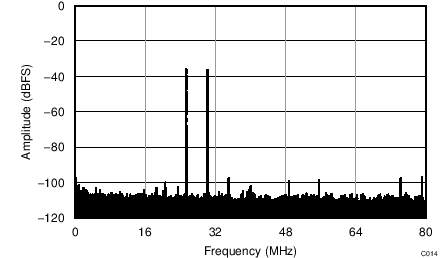

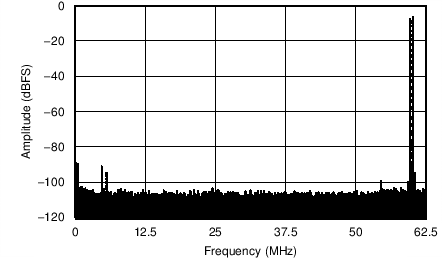

| fS = 160 MSPS, IMD = 87 dBFS, fIN1 = 185 MHz, fIN2 = 190 MHz, SFDR = 90 dBFS |

Figure 13. FFT for Two-Tone Input Signal

(–7 dBFS at 185 MHz and 190 MHz)

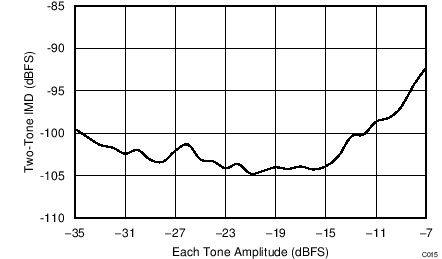

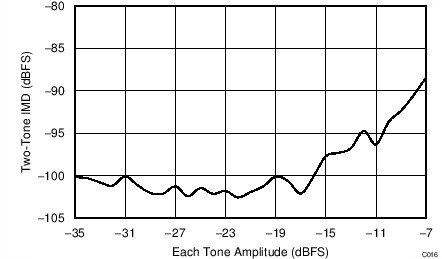

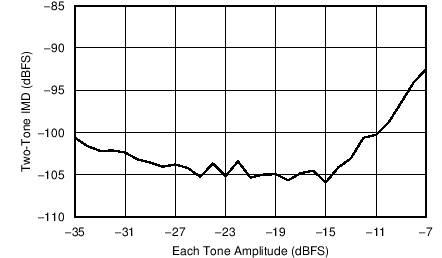

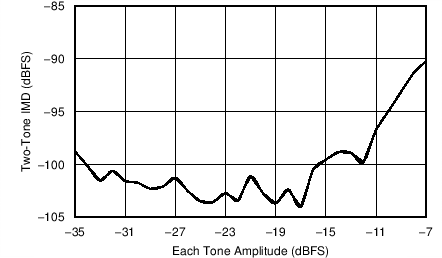

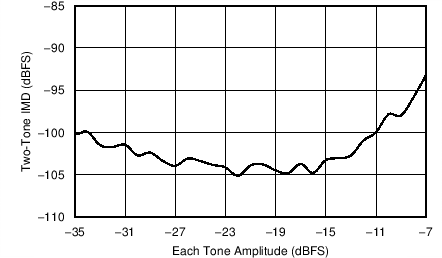

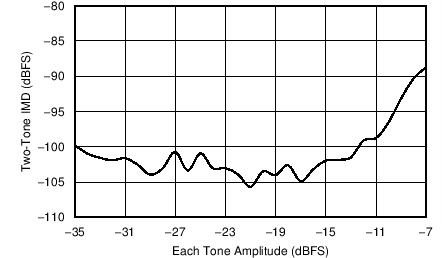

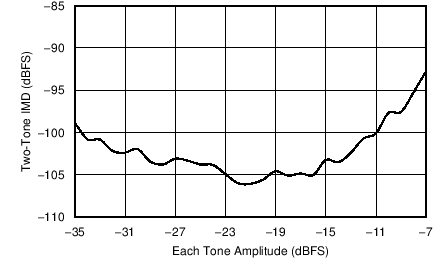

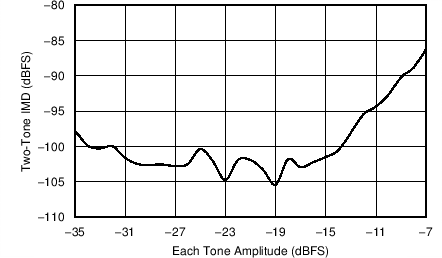

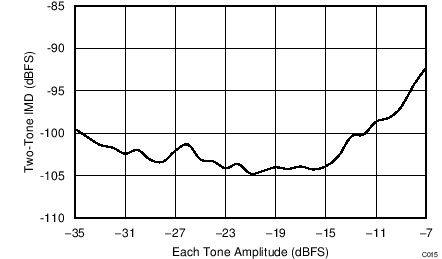

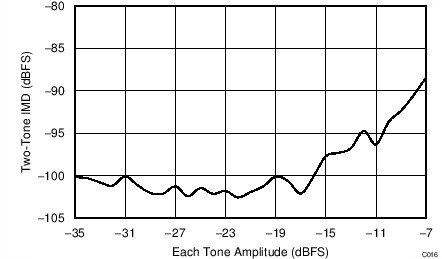

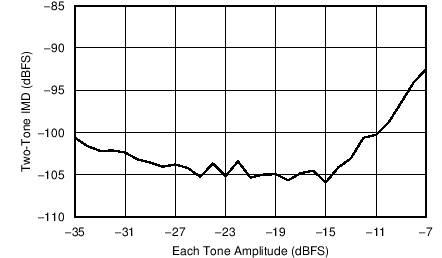

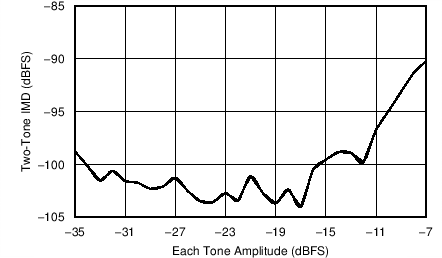

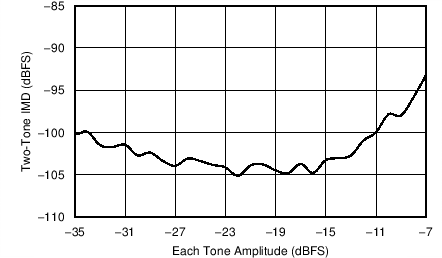

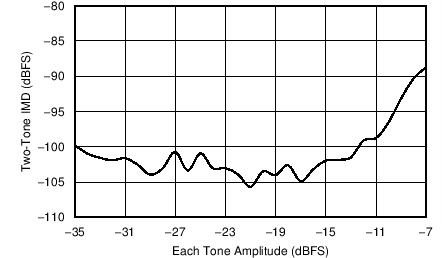

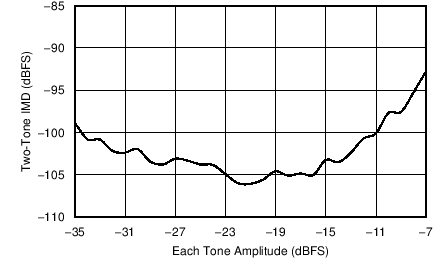

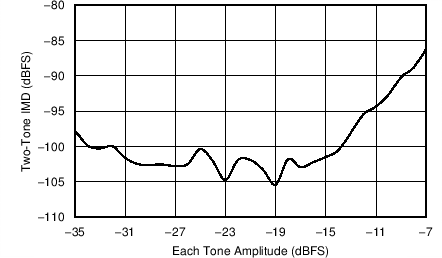

| fS = 160 MSPS, fIN1 = 46 MHz, fIN2 = 50 MHz |

Figure 15. IMD vs Input Amplitude (46 MHz and 50 MHz)

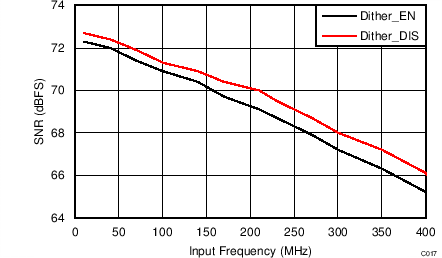

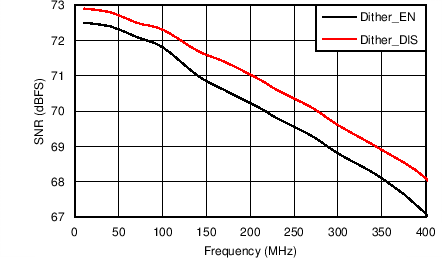

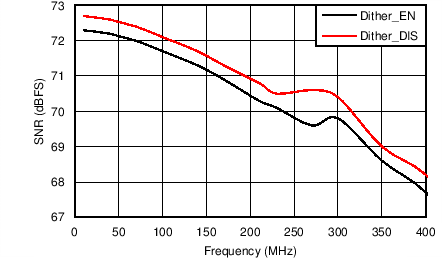

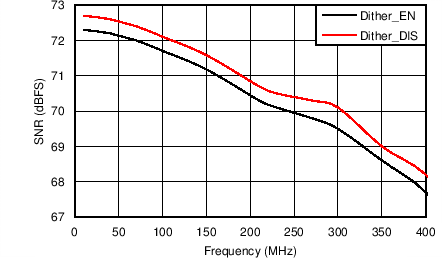

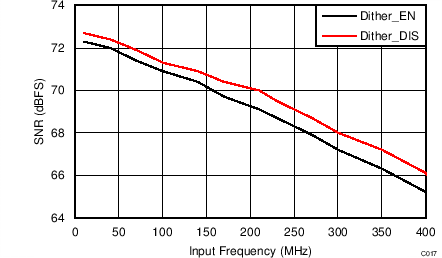

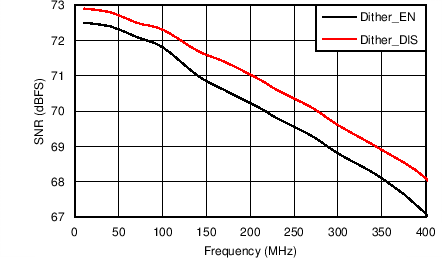

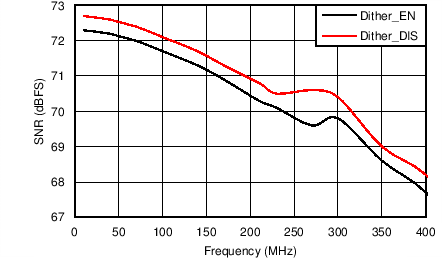

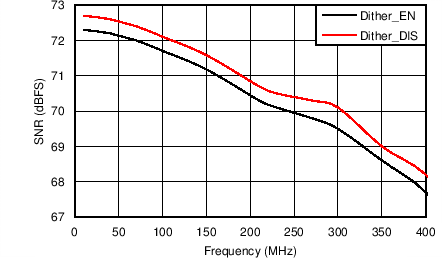

Figure 17. SNR vs Input Frequency

Figure 17. SNR vs Input Frequency

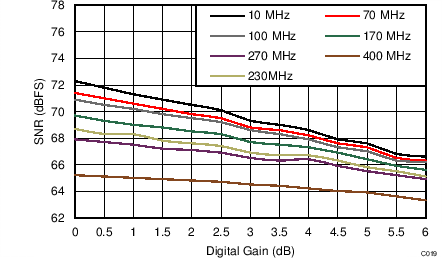

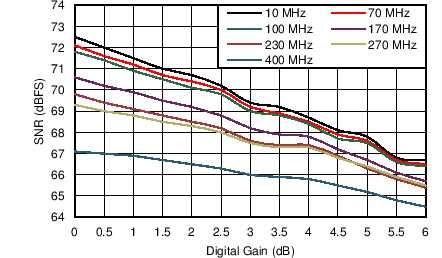

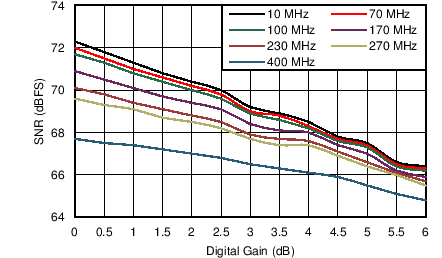

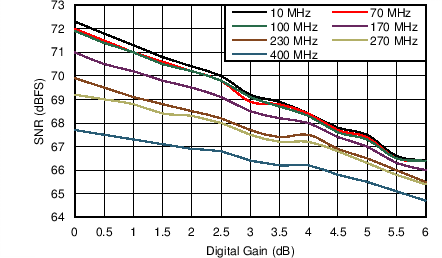

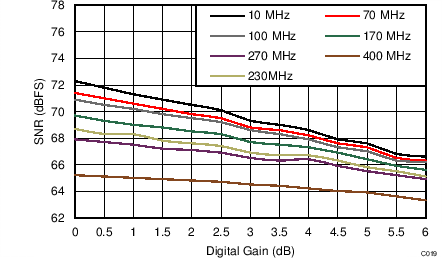

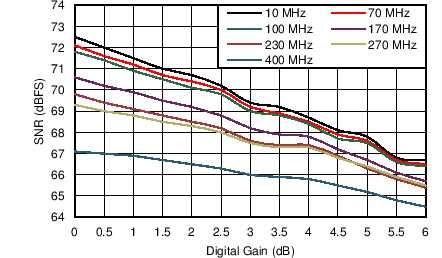

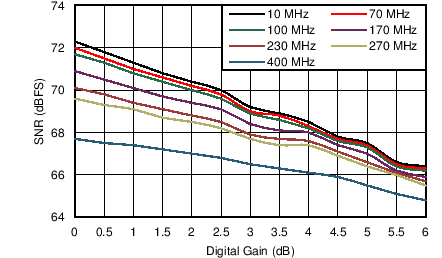

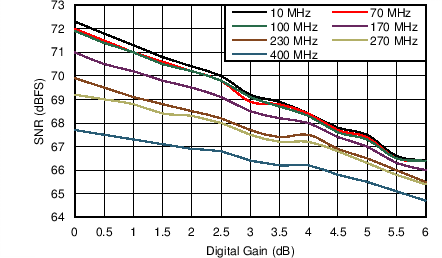

Figure 19. SNR vs Digital Gain and Input Frequency

Figure 19. SNR vs Digital Gain and Input Frequency

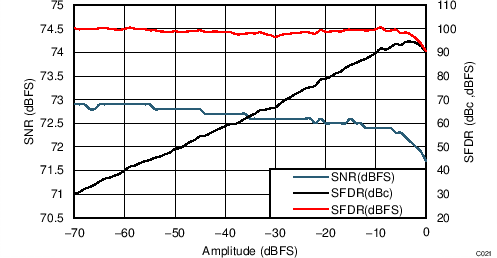

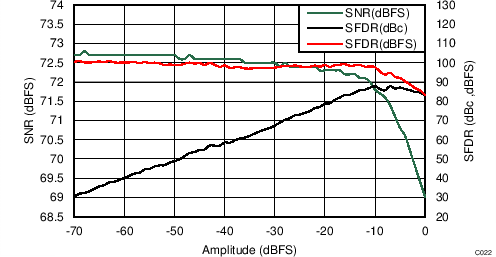

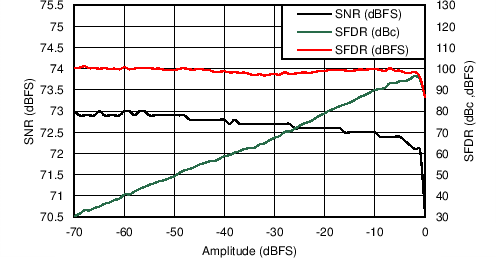

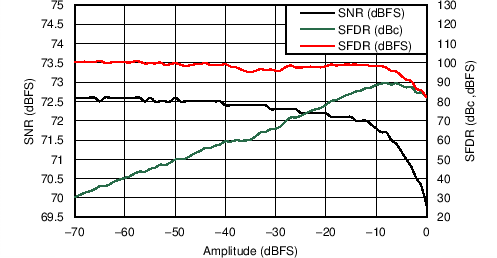

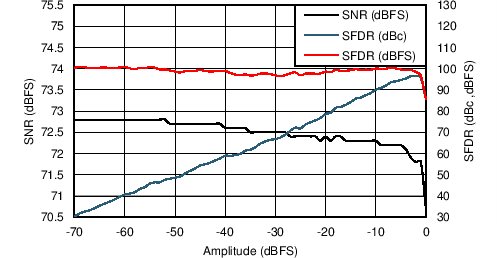

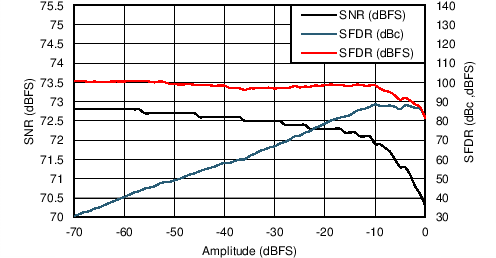

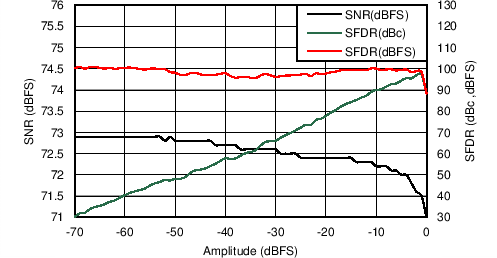

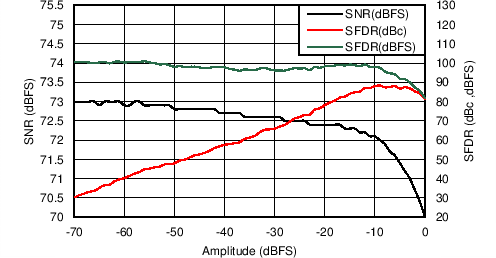

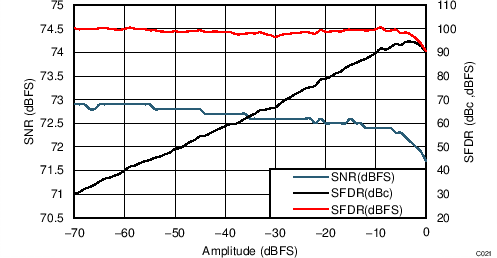

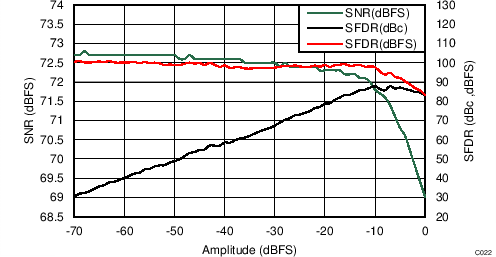

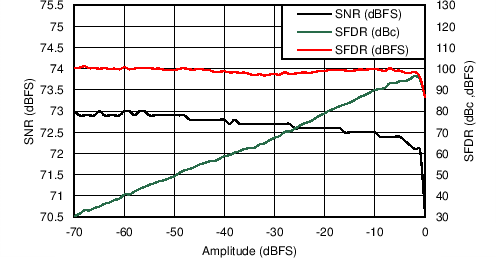

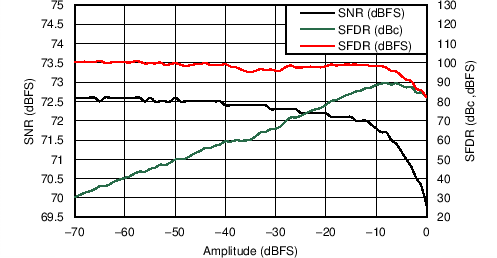

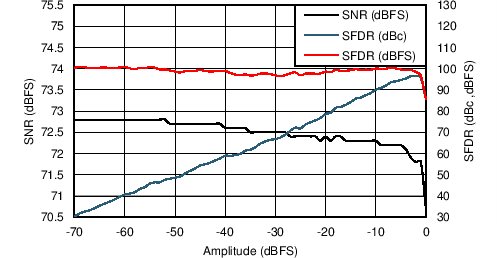

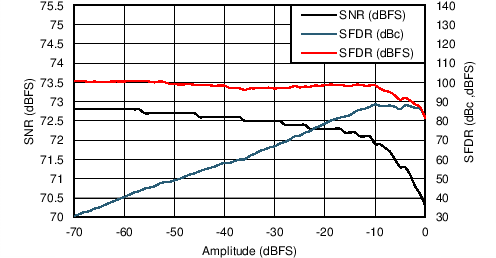

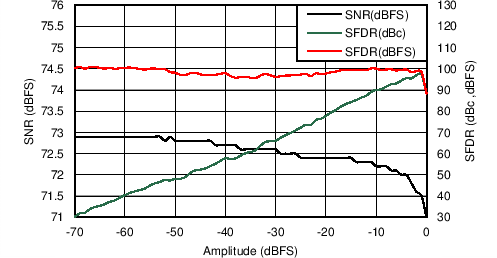

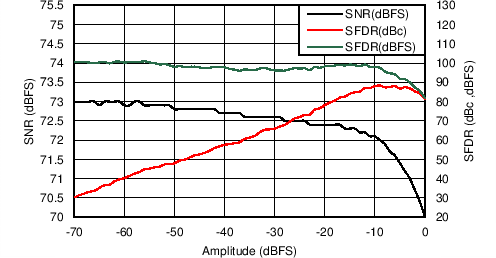

Figure 21. Performance Across Input Amplitude (30 MHz)

Figure 21. Performance Across Input Amplitude (30 MHz)

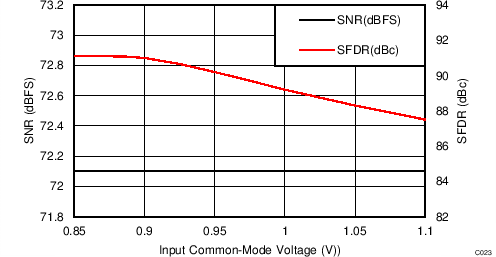

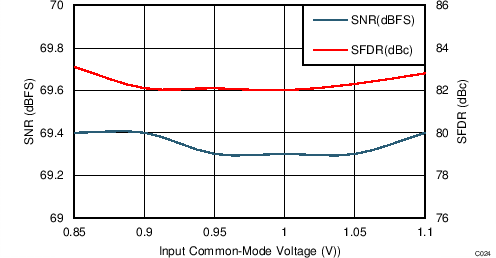

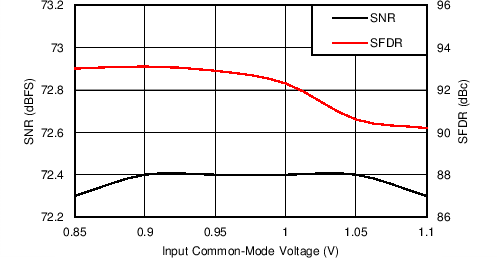

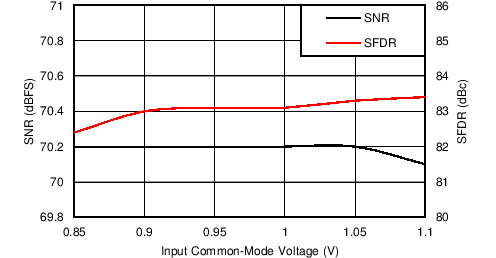

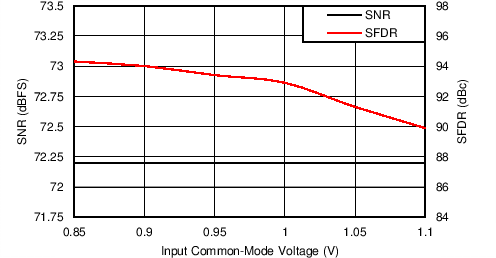

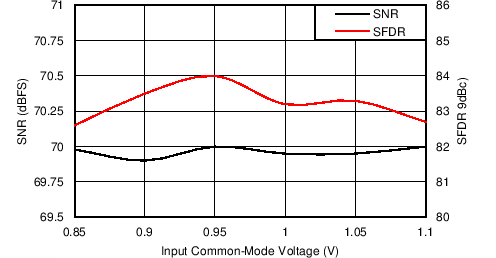

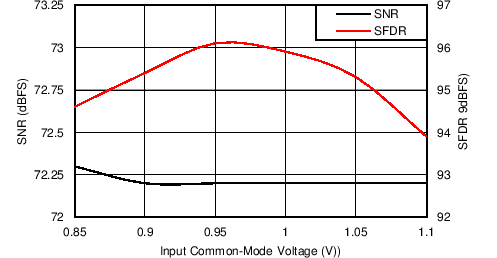

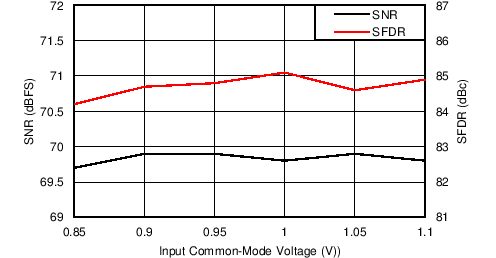

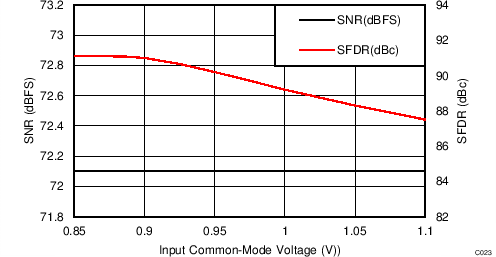

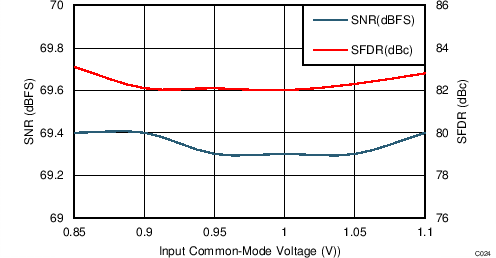

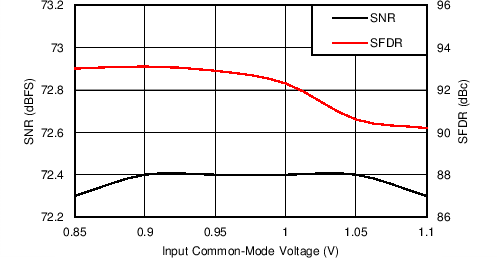

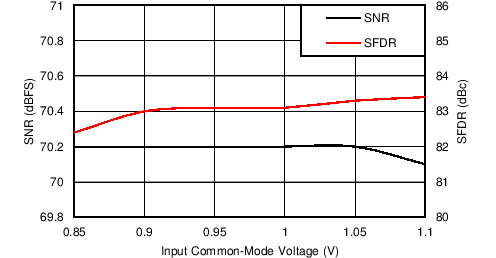

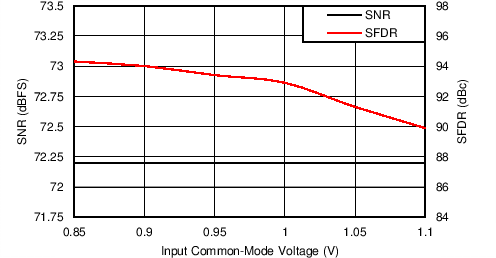

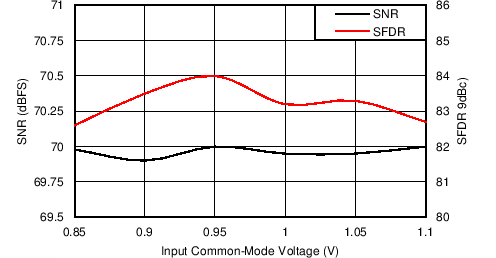

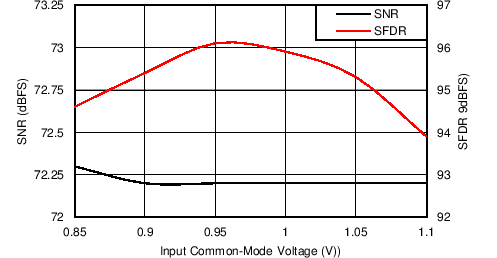

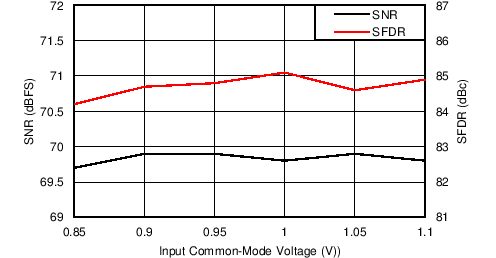

Figure 23. Performance vs Input Common-Mode Voltage

Figure 23. Performance vs Input Common-Mode Voltage

(30 MHz)

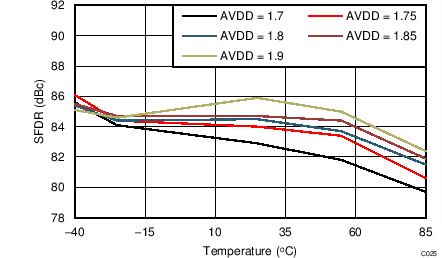

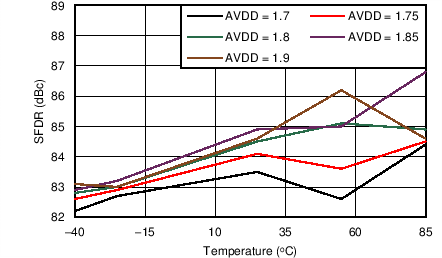

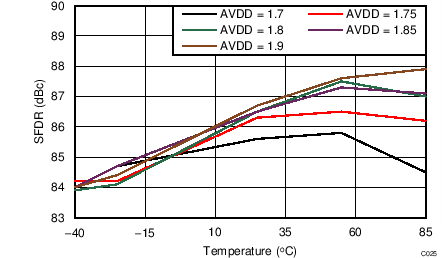

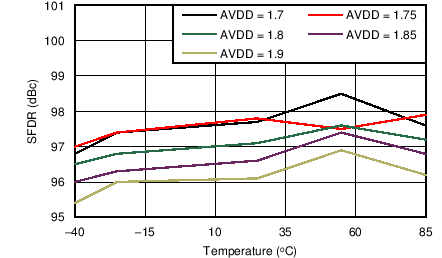

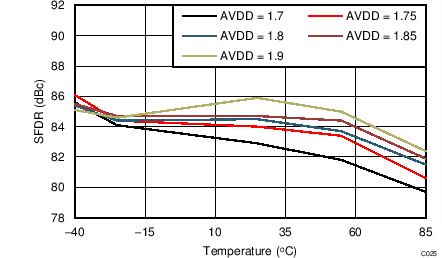

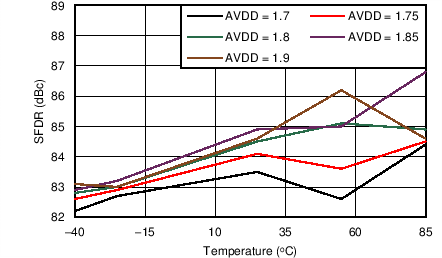

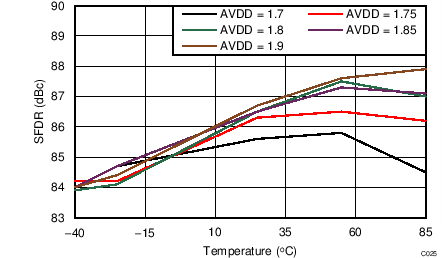

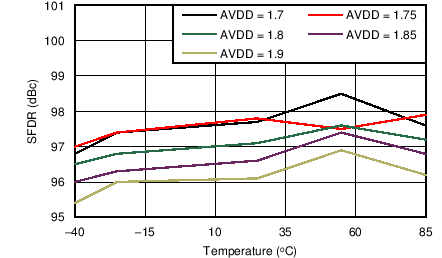

Figure 25. SFDR vs AVDD Supply and Temperature

Figure 25. SFDR vs AVDD Supply and Temperature

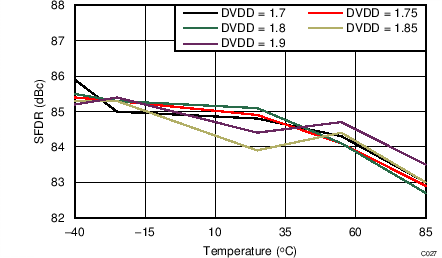

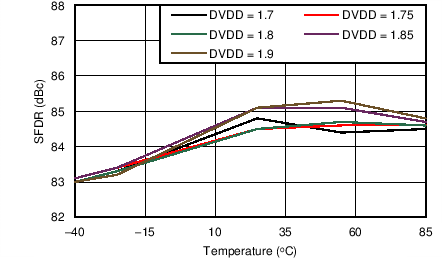

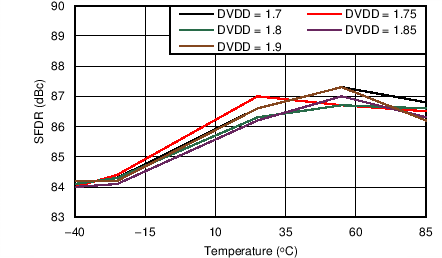

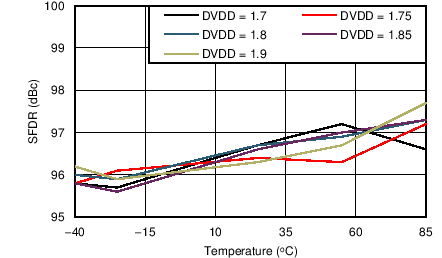

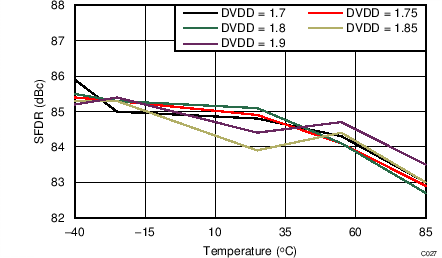

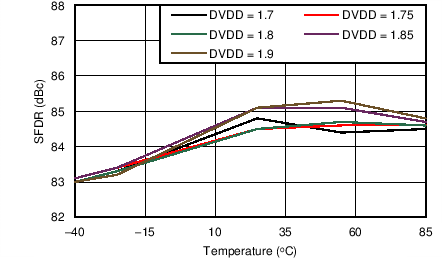

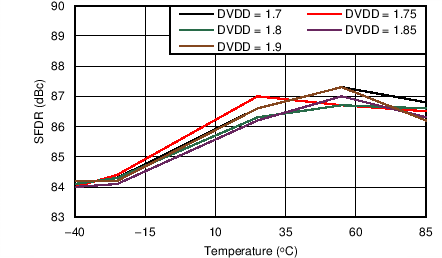

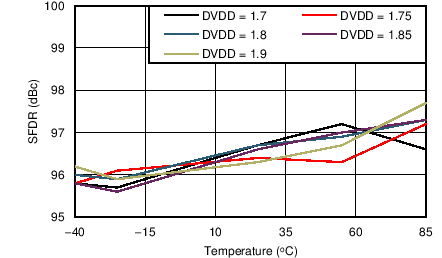

Figure 27. SFDR vs DVDD Supply and Temperature

Figure 27. SFDR vs DVDD Supply and Temperature

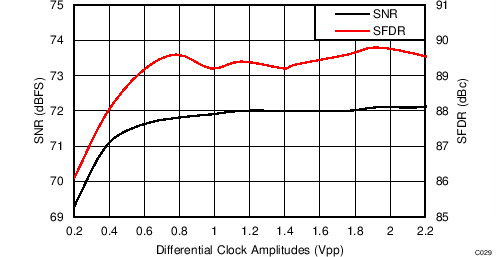

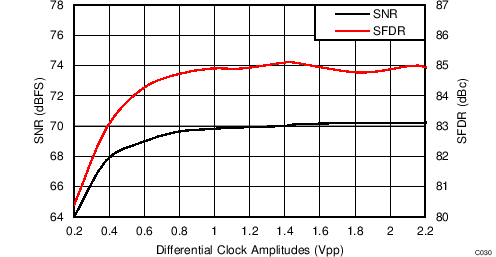

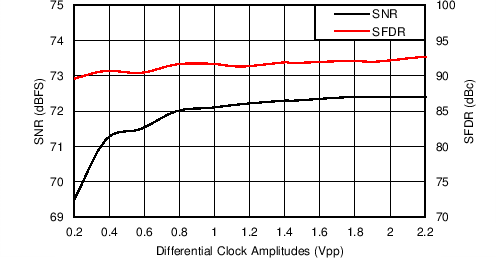

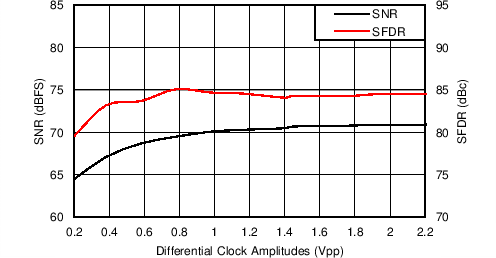

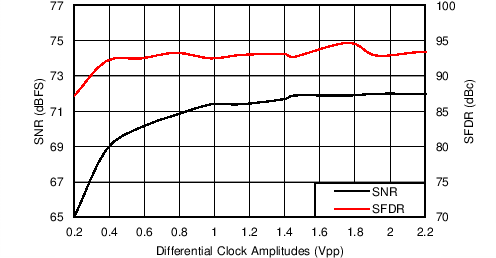

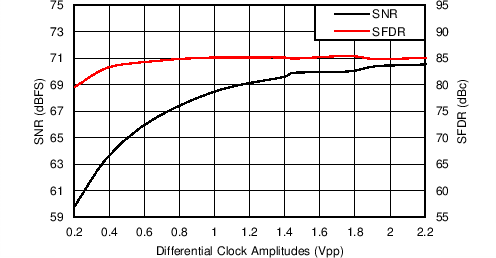

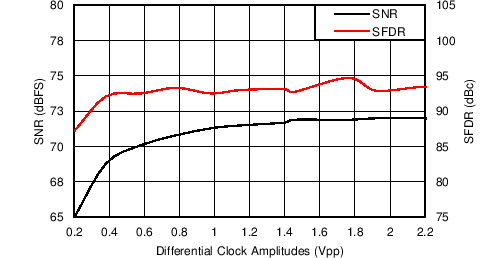

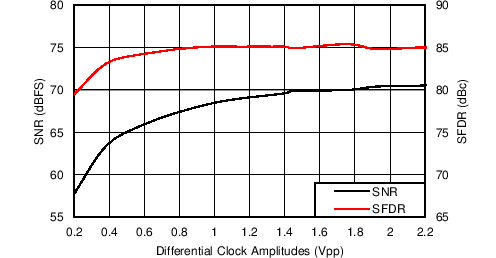

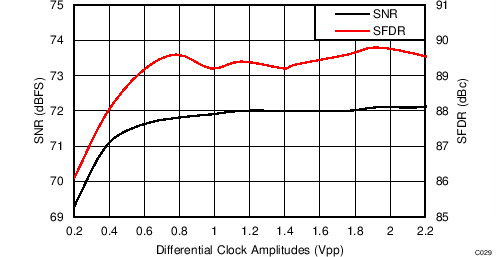

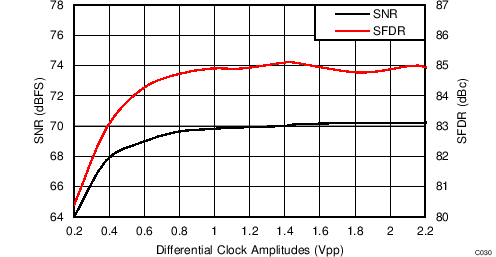

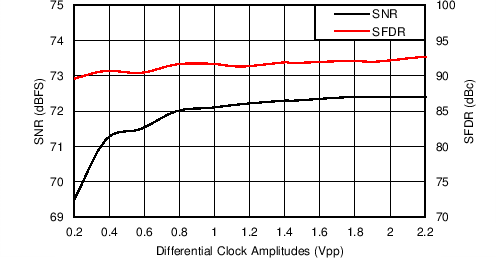

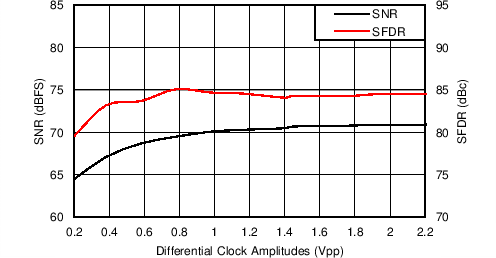

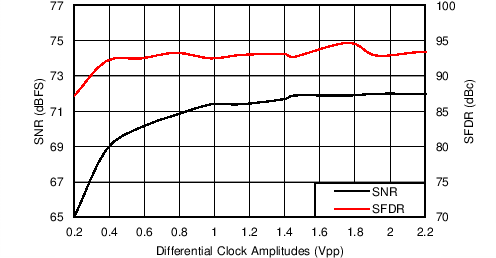

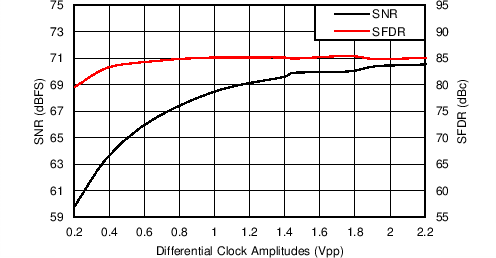

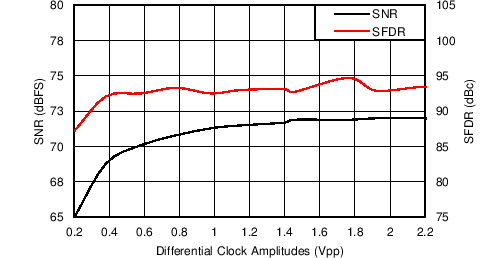

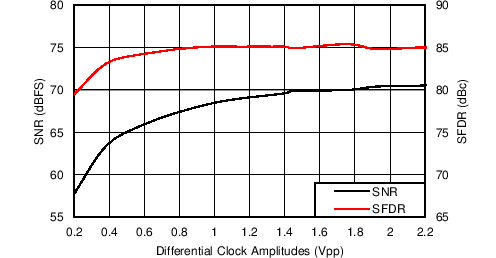

Figure 29. Performance vs Clock Amplitude (40 MHz)

Figure 29. Performance vs Clock Amplitude (40 MHz)

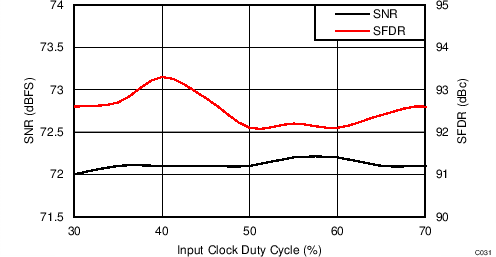

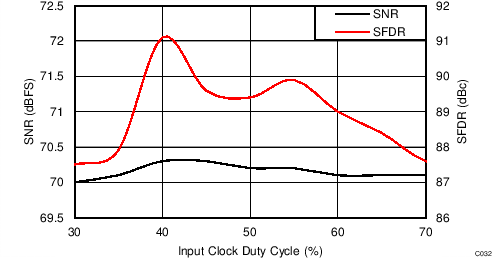

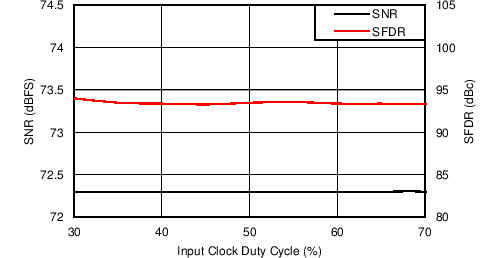

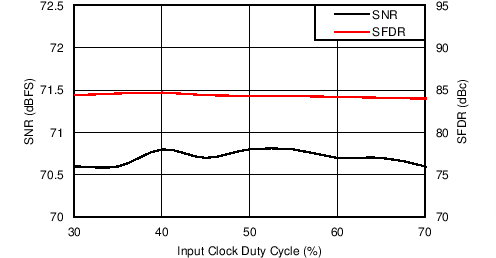

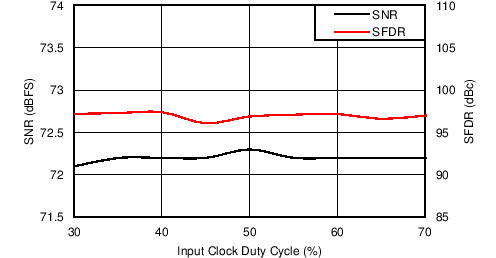

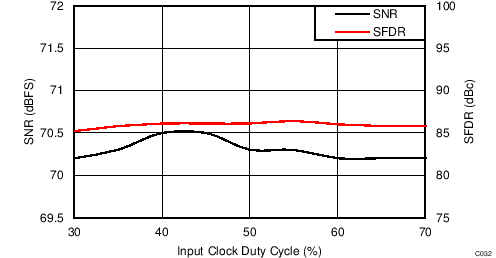

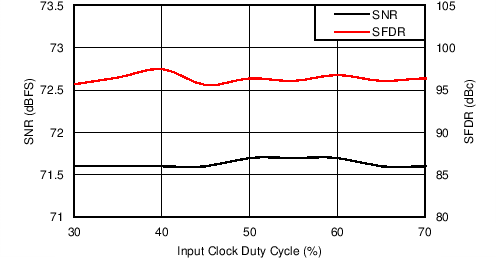

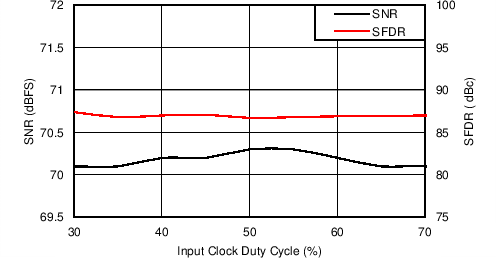

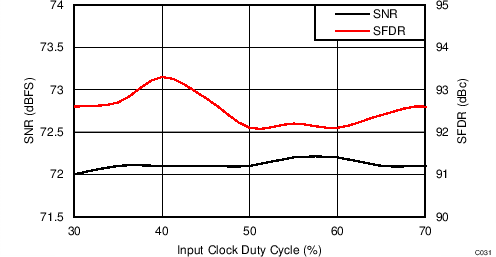

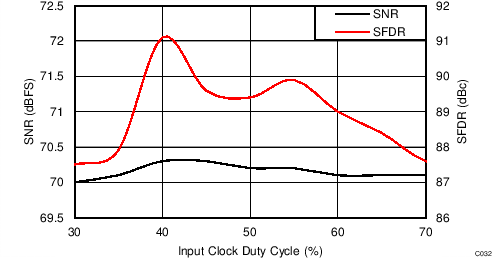

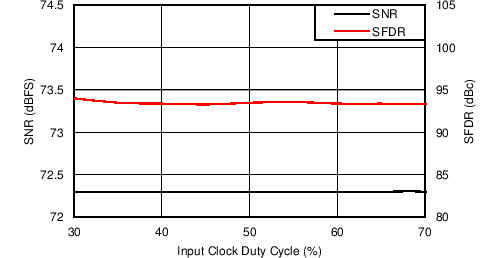

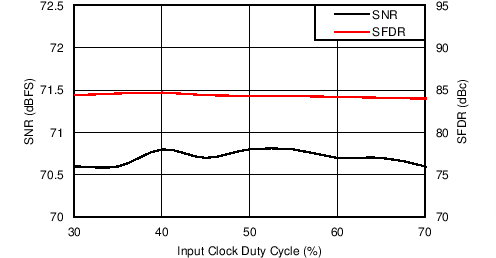

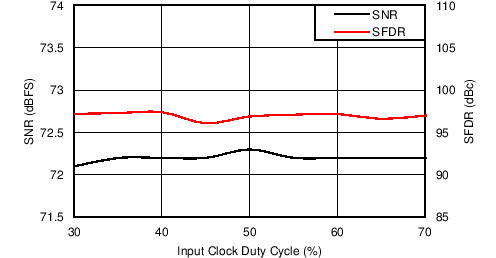

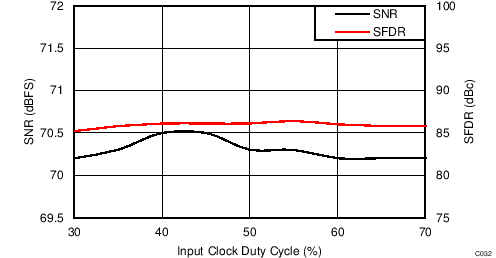

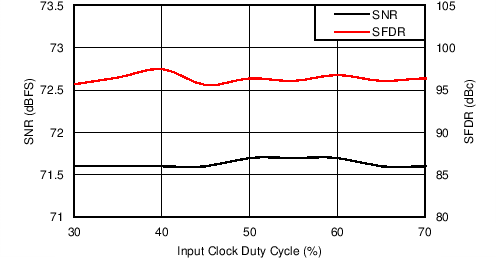

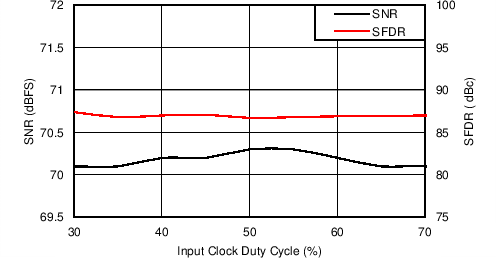

Figure 31. Performance vs Clock Duty Cycle (40 MHz)

Figure 31. Performance vs Clock Duty Cycle (40 MHz)

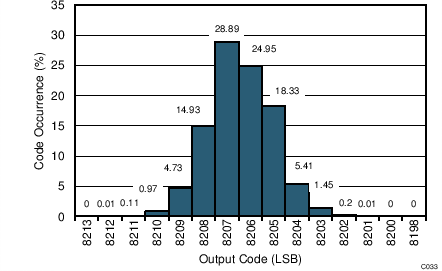

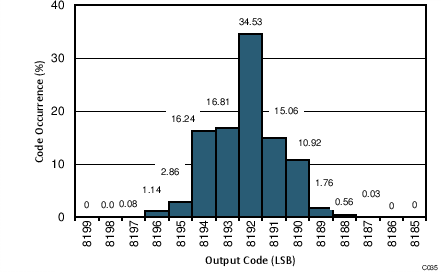

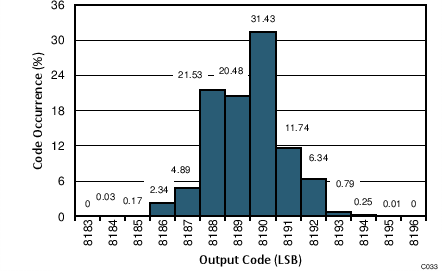

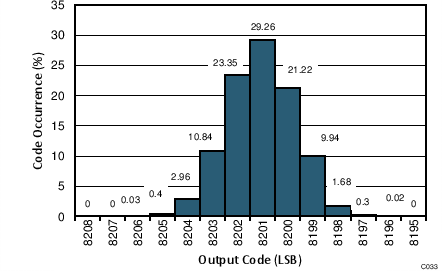

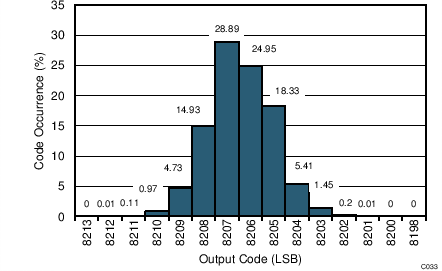

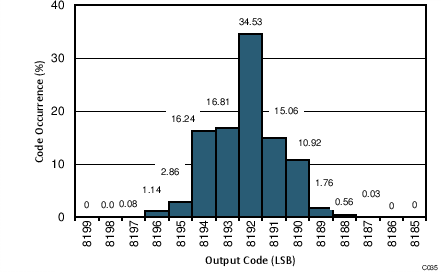

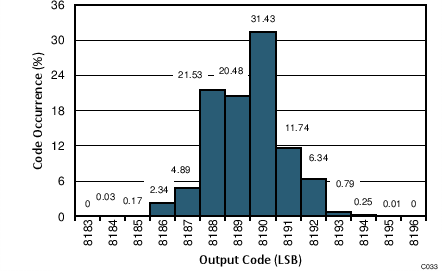

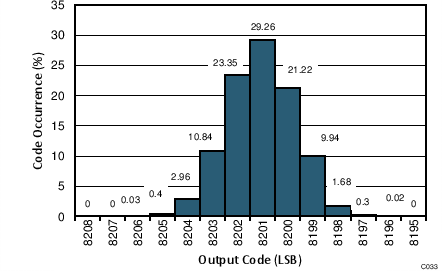

Figure 33. Idle Channel Histogram

Figure 33. Idle Channel Histogram

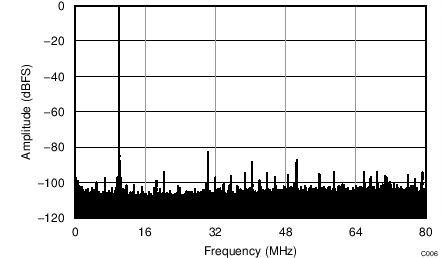

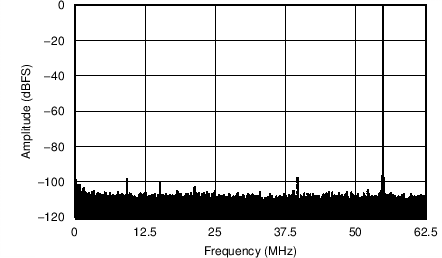

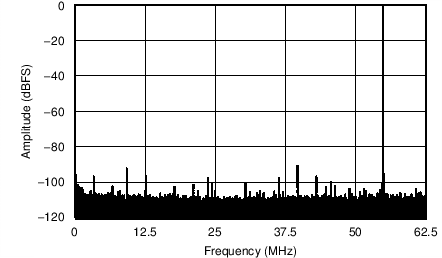

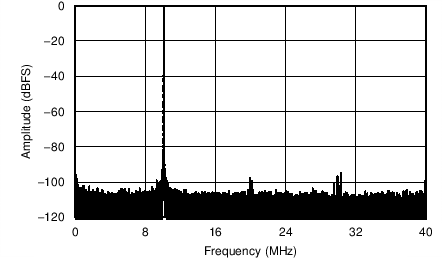

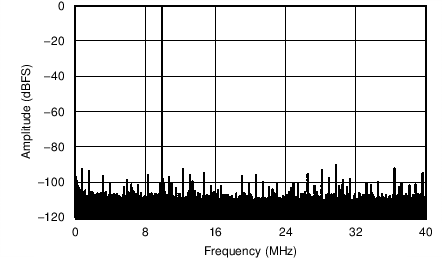

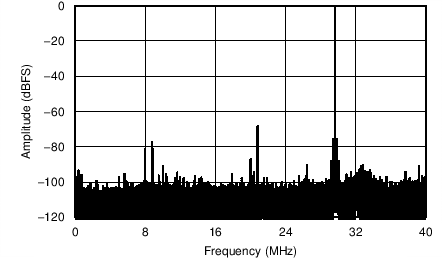

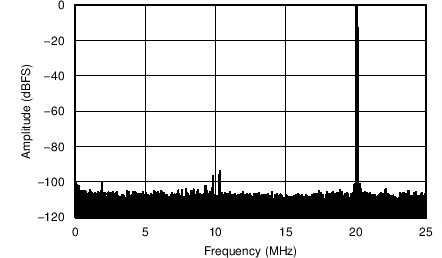

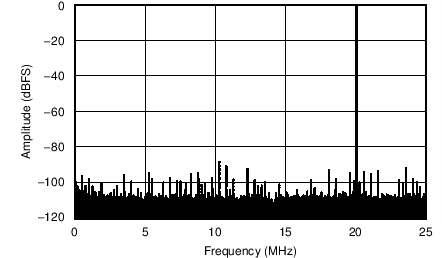

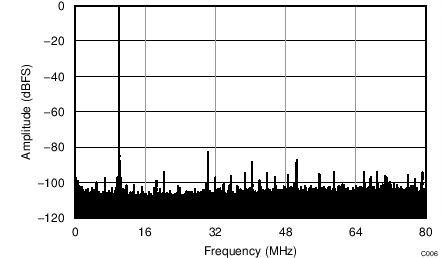

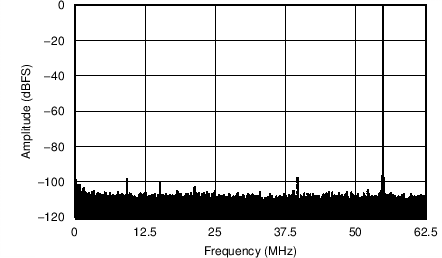

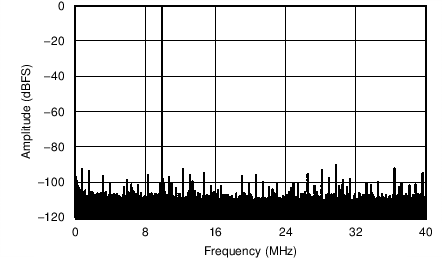

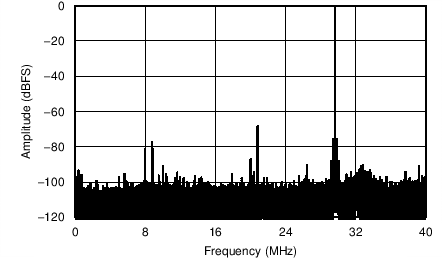

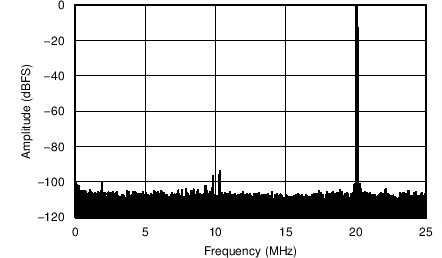

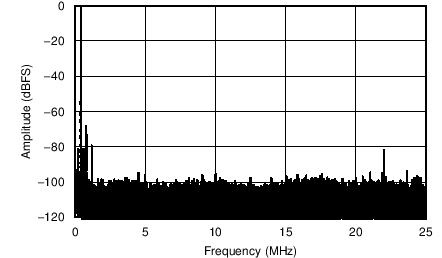

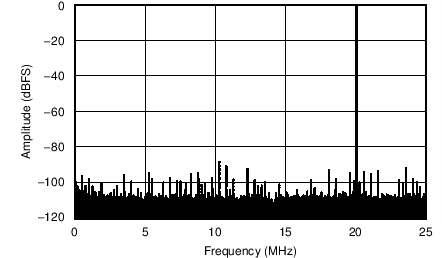

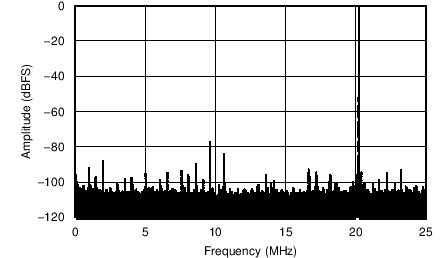

| fS = 160 MSPS, SNR = 72.7 dBFS, fIN = 10 MHz, SFDR = 85 dBc |

Figure 2. FFT for 10-MHz Input signal, Dither Off

| fS = 160 MSPS, SNR = 71.8 dBFS, fIN = 70 MHz, SFDR = 85 dBc |

Figure 4. FFT for 70-MHz Input Signal, Dither Off

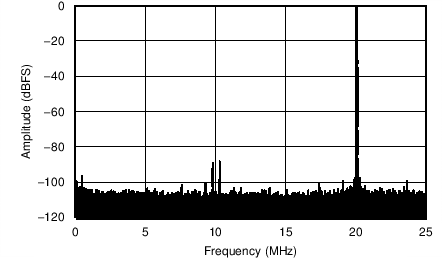

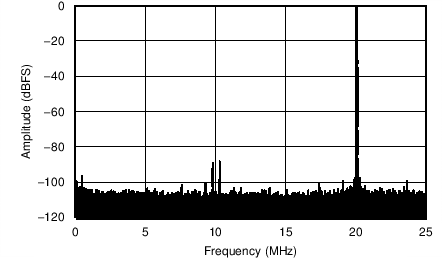

| fS = 160 MSPS, SNR = 70.4 dBFS, fIN = 70 MHz, SFDR = 81 dBc |

|

Figure 6. FFT for 170-MHz Input Signal, Dither Off

fS = 160 MSPS, SNR = 68.8 dBFS, fIN = 270 MHz,

SFDR = 75 dBc |

Figure 8. FFT for 270-MHz Input Signal, Dither Off

fS = 160 MSPS, SNR = 63.4 dBFS, fIN = 450 MHz,

SFDR = 63 dBc |

Figure 10. FFT for 450-MHz Input Signal, Dither Off

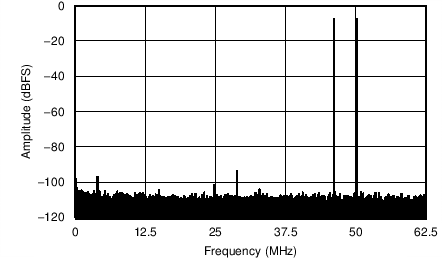

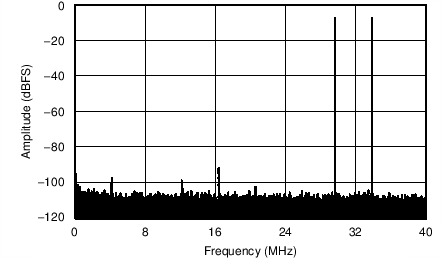

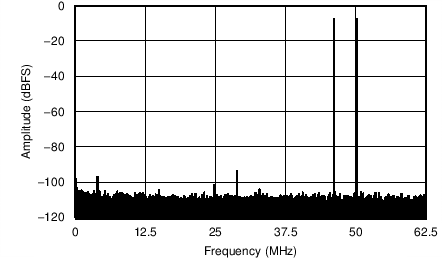

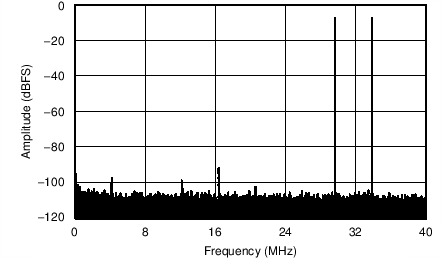

| fS = 160 MSPS, IMD = 99 dBFS, fIN1 = 46 MHz, fIN2 = 50 MHz, SFDR = 102 dBFS |

Figure 12. FFT for Two-Tone Input Signal

(–36 dBFS at 46 MHz and 50 MHz)

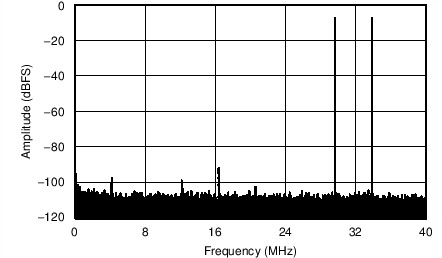

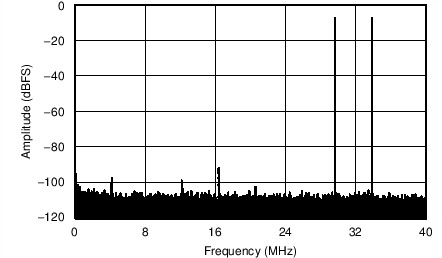

| fS = 160 MSPS, IMD = 100 dBFS, fIN1 = 185 MHz, fIN2 = 190 MHz, SFDR = 102 dBFS |

Figure 14. FFT for Two-Tone Input Signal

(–36 dBFS at 185 MHz and 190 MHz)

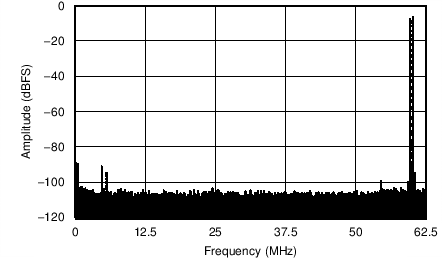

| fS = 160 MSPS, fIN1 = 185 MHz, fIN2 = 190 MHz |

Figure 16. IMD vs Input Amplitude (185 MHz and 190 MHz)

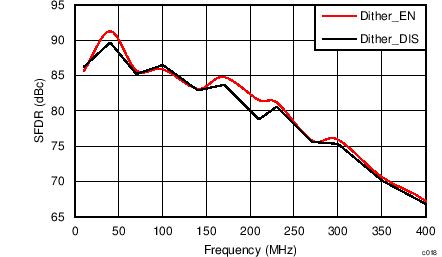

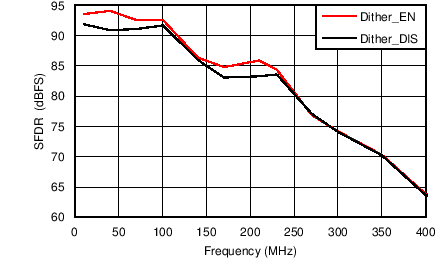

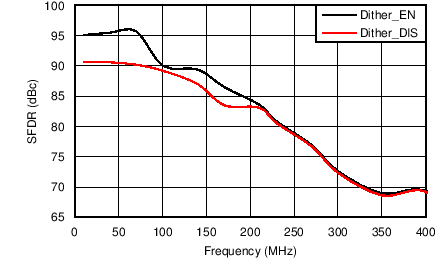

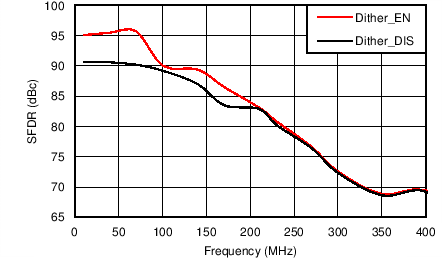

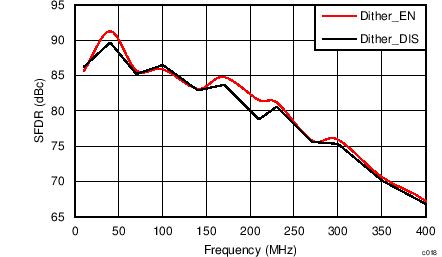

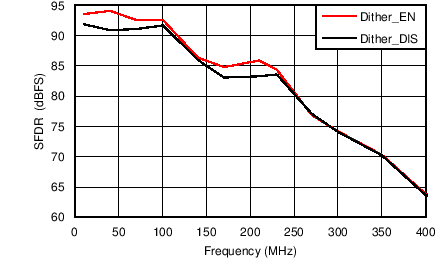

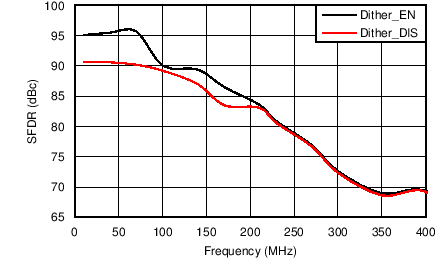

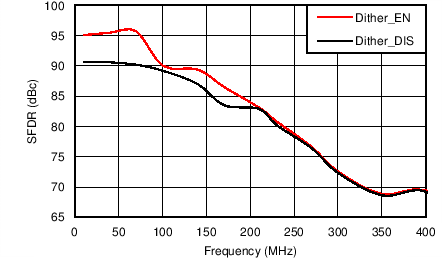

Figure 18. SFDR vs Input Frequency

Figure 18. SFDR vs Input Frequency

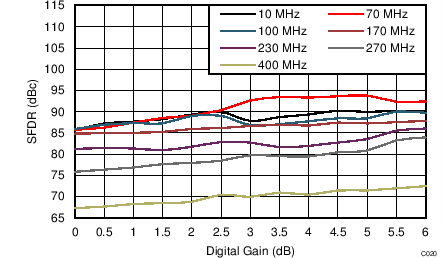

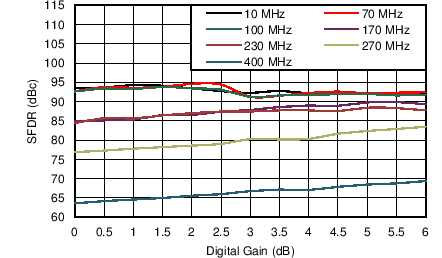

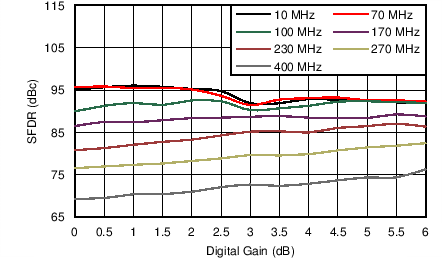

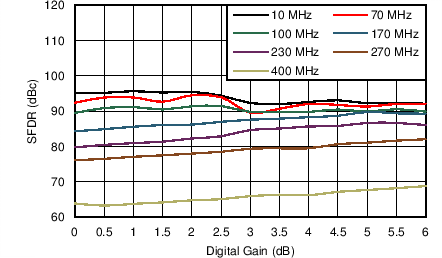

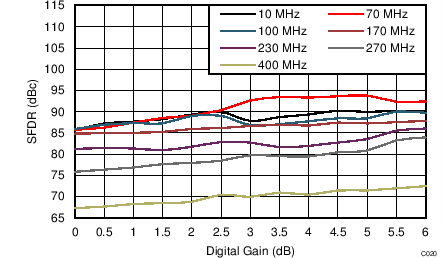

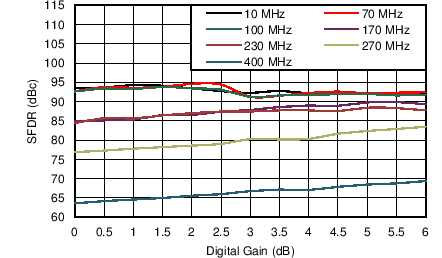

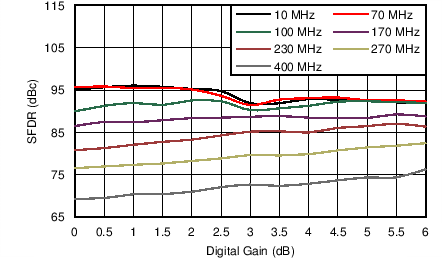

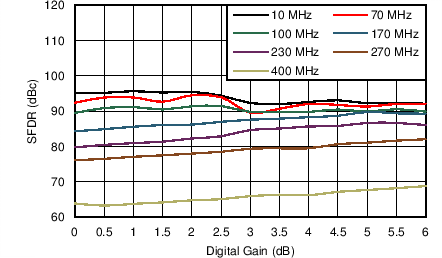

Figure 20. SFDR vs Digital Gain and Input Frequency

Figure 20. SFDR vs Digital Gain and Input Frequency

Figure 22. Performance Across Input Amplitude (170 MHz)

Figure 22. Performance Across Input Amplitude (170 MHz)

Figure 24. Performance vs Input Common-Mode Voltage (170 MHz)

Figure 24. Performance vs Input Common-Mode Voltage (170 MHz)

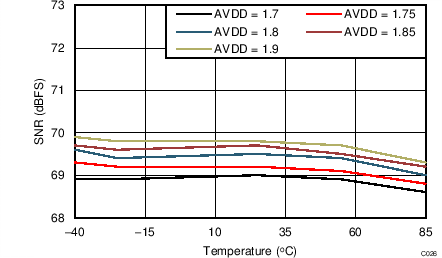

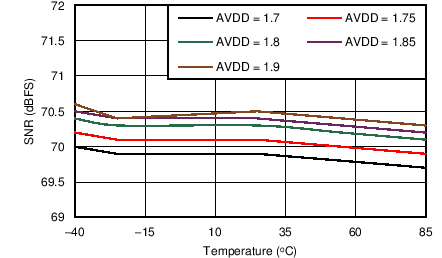

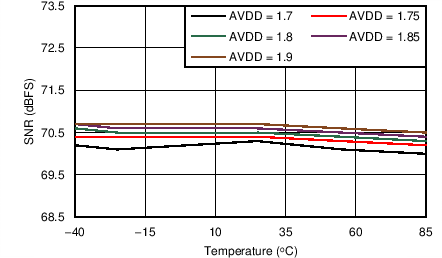

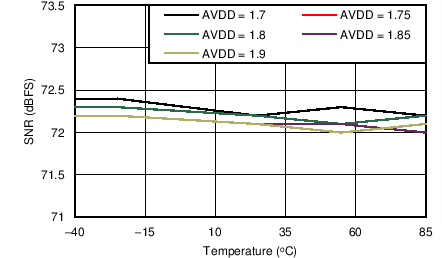

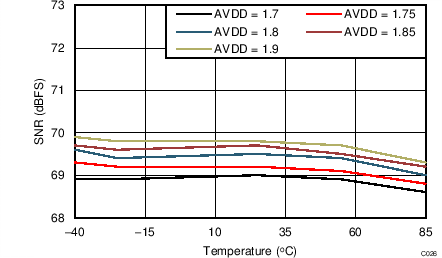

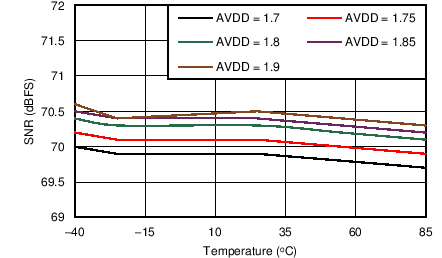

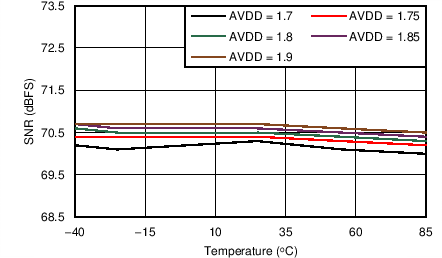

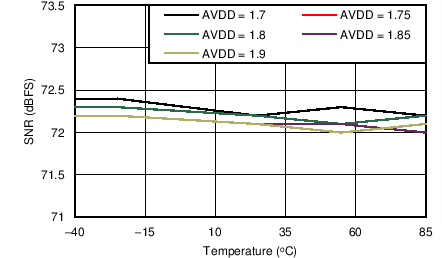

Figure 26. SNR vs AVDD Supply and Temperature

Figure 26. SNR vs AVDD Supply and Temperature

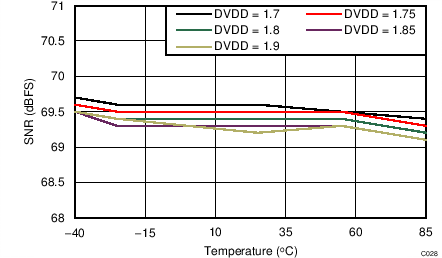

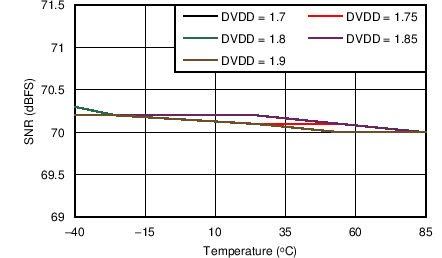

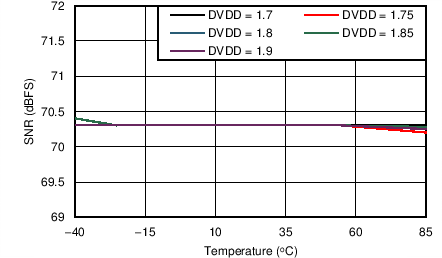

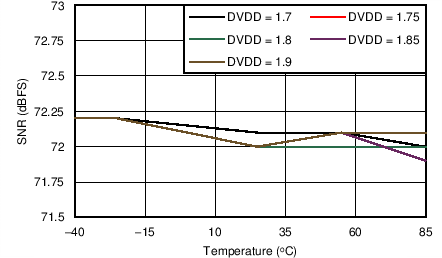

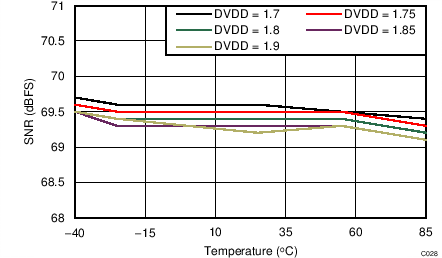

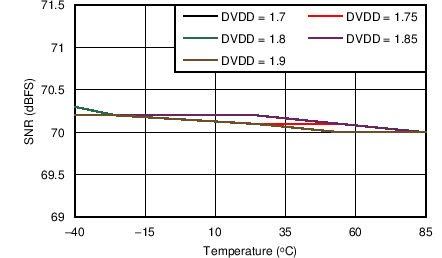

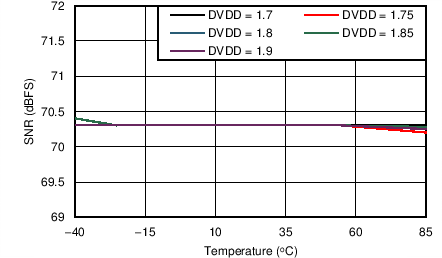

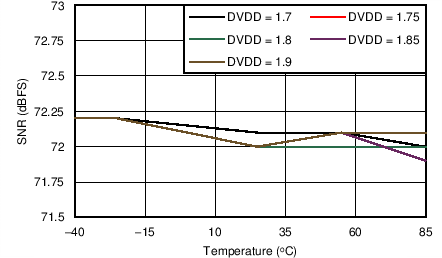

Figure 28. SNR vs DVDD Supply and Temperature

Figure 28. SNR vs DVDD Supply and Temperature

Figure 30. Performance vs Clock Amplitude (150 MHz)

Figure 30. Performance vs Clock Amplitude (150 MHz)

Figure 32. Performance vs Clock Duty Cycle (150 MHz)

Figure 32. Performance vs Clock Duty Cycle (150 MHz)

7.16 Typical Characteristics: ADC34J44

Typical values are at TA= 25°C, ADC sampling rate = 125 MSPS, 50% clock duty cycle, AVDD = DVDD = 1.8 V, –1-dBFS differential input, 2-VPP full-scale, and 32k-point FFT, unless otherwise noted.

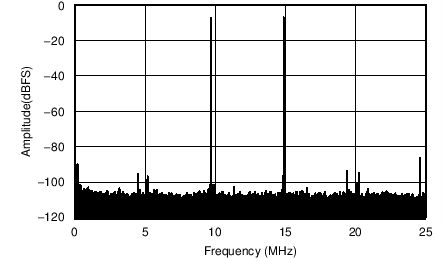

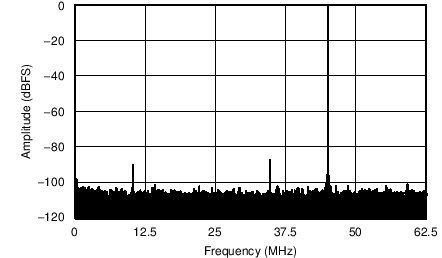

| fS = 125 MSPS, SNR = 72.6 dBFS, fIN = 10 MHz, SFDR = 94 dBc |

Figure 34. FFT for 10-MHz Input Signal, Dither On

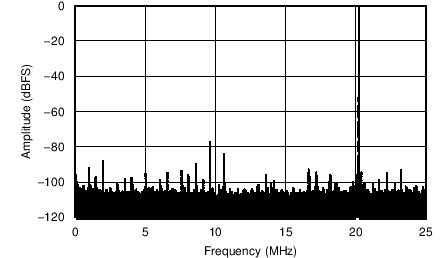

| fS = 125 MSPS, SNR = 72.2 dBFS, fIN = 70 MHz, SFDR = 95 dBc |

Figure 36. FFT for 70-MHz Input Signal, Dither On

fS = 125 MSPS, SNR = 70.5 dBFS, fIN = 170 MHz,

SFDR = 87 dBc |

Figure 38. FFT for 170-MHz Input Signal, Dither On

fS = 125 MSPS, SNR = 69.6 dBFS, fIN = 270 MHz,

SFDR = 80 dBc |

Figure 40. FFT for 270-MHz Input Signal, Dither On

fS = 125 MSPS, SNR = 65.8 dBFS, fIN = 450 MHz,

SFDR = 68 dBc |

Figure 42. FFT for 450-MHz Input Signal, Dither On

| fS = 125 MSPS, IMD = 93 dBFS, fIN1 = 46 MHz, fIN2 = 50 MHz, SFDR = 97 dBFS |

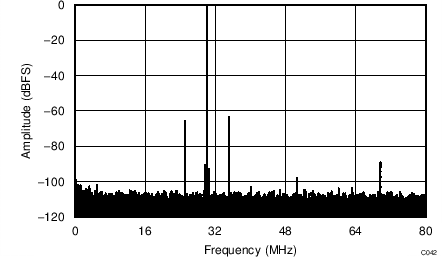

Figure 44. FFT for Two-Tone Input Signal

(–7dBFS at 46 MHz and 50 MHz)

| fS = 125 MSPS, IMD = 88 dBFS, fIN1 = 185 MHz, fIN2 = 190 MHz, SFDR = 190 dBFS |

Figure 46. FFT for Two-Tone Input Signal

(–7 dBFS at 185 MHz and 190 MHz)

Figure 48. IMD vs Input Amplitude (46 MHz and 50 MHz)

Figure 48. IMD vs Input Amplitude (46 MHz and 50 MHz)

Figure 50. SNR vs Input Frequency

Figure 50. SNR vs Input Frequency

Figure 52. SNR vs Digital Gain and Input Frequency

Figure 52. SNR vs Digital Gain and Input Frequency

Figure 54. Performance Across Input Amplitude (30 MHz)

Figure 54. Performance Across Input Amplitude (30 MHz)

Figure 56. Performance vs Input Common-Mode Voltage

Figure 56. Performance vs Input Common-Mode Voltage

(30 MHz)

Figure 58. SFDR vs AVDD Supply and Temperature

Figure 58. SFDR vs AVDD Supply and Temperature

Figure 60. SFDR vs DVDD Supply and Temperature

Figure 60. SFDR vs DVDD Supply and Temperature

Figure 62. Performance vs Clock Amplitude (40 MHz)

Figure 62. Performance vs Clock Amplitude (40 MHz)

Figure 64. Performance vs Clock Duty Cycle (40 MHz)

Figure 64. Performance vs Clock Duty Cycle (40 MHz)

Figure 66. Idle Channel Histogram

Figure 66. Idle Channel Histogram

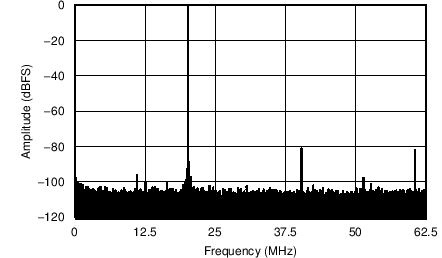

| fS = 125 MSPS, SNR = 73.1 dBFS, fIN = 10 MHz, SFDR = 88 dBc |

Figure 35. FFT for 10-MHz Input Signal, Dither Off

| fS = 125 MSPS, SNR = 72.7 dBFS, fIN = 70 MHz, SFDR = 89 dBc |

Figure 37. FFT for 70-MHz Input Signal, Dither Off

fS = 125 MSPS, SNR = 71.4 dBFS, fIN = 70 MHz,

SFDR = 86 dBc |

Figure 39. FFT for 170-MHz Input Signal, Dither Off

fS = 125 MSPS, SNR = 70.3 dBFS, fIN = 270 MHz,

SFDR = 79 dBc |

Figure 41. FFT for 270-MHz Input Signal, Dither Off

fS = 125 MSPS, SNR = 66.5 dBFS, fIN = 450 MHz,

SFDR = 67 dBc |

Figure 43. FFT for 450-MHz Input Signal, Dither Off

| fS = 125 MSPS, IMD = 101 dBFS, fIN1 = 46 MHz, fIN2 = 50 MHz, SFDR = 106 dBFS |

Figure 45. FFT for Two-Tone Input Signal

(–36 dBFS at 46 MHz and 50 MHz)

| fS = 125 MSPS, IMD = 99 dBFS, fIN1 = 46 MHz, fIN2 = 50 MHz, SFDR = 104 dBFS |

Figure 47. FFT for Two-Tone Input Signal

(–36 dBFS at 185 MHz and 190 MHz)

Figure 49. IMD vs Input Amplitude (185 MHz and 190 MHz)

Figure 49. IMD vs Input Amplitude (185 MHz and 190 MHz)

Figure 51. SFDR vs Input Frequency

Figure 51. SFDR vs Input Frequency

Figure 53. SFDR vs Digital Gain and Input Frequency

Figure 53. SFDR vs Digital Gain and Input Frequency

Figure 55. Performance Across Input Amplitude (170 MHz)

Figure 55. Performance Across Input Amplitude (170 MHz)

Figure 57. Performance vs Input Common-Mode Voltage (170 MHz)

Figure 57. Performance vs Input Common-Mode Voltage (170 MHz)

Figure 59. SNR vs AVDD Supply and Temperature

Figure 59. SNR vs AVDD Supply and Temperature

Figure 61. SNR vs DVDD Supply and Temperature

Figure 61. SNR vs DVDD Supply and Temperature

Figure 63. Performance vs Clock Amplitude (150 MHz)

Figure 63. Performance vs Clock Amplitude (150 MHz)

Figure 65. Performance vs Clock Duty Cycle (150 MHz)

Figure 65. Performance vs Clock Duty Cycle (150 MHz)

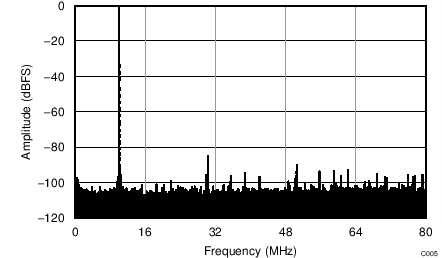

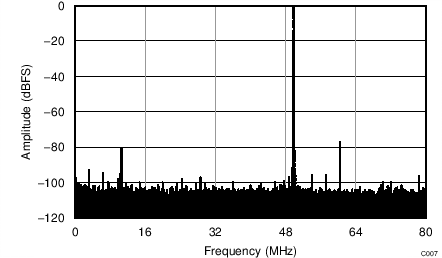

7.17 Typical Characteristics: ADC34J43

Typical values are at TA= 25°C, ADC sampling rate = 80 MSPS, 50% clock duty cycle, AVDD = DVDD = 1.8 V, –1-dBFS differential input, 2-VPP full-scale, and 32k-point FFT, unless otherwise noted.

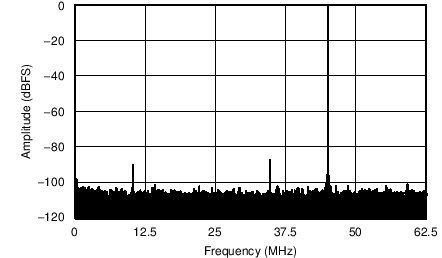

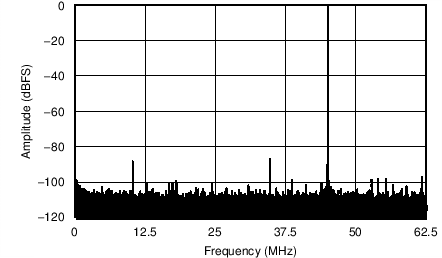

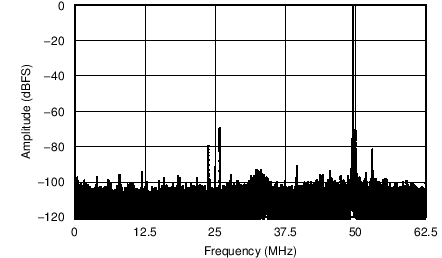

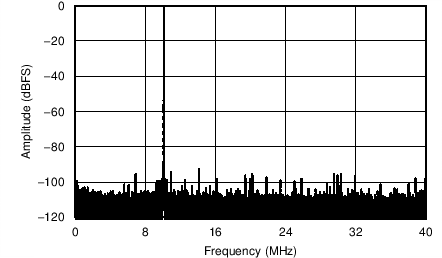

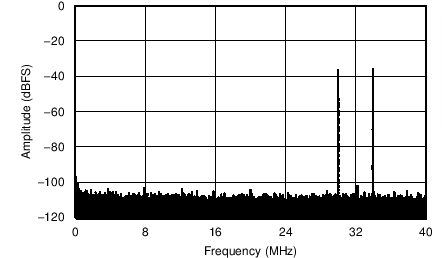

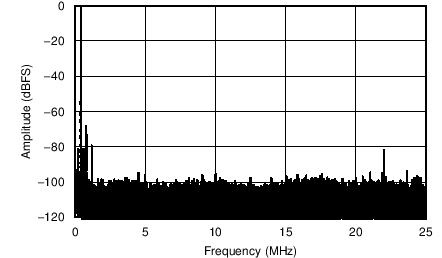

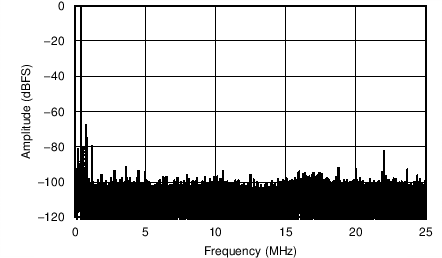

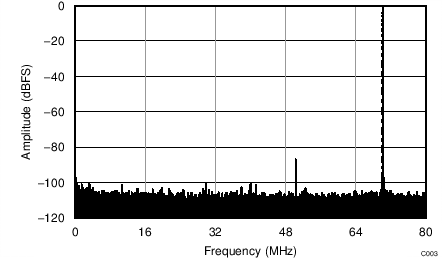

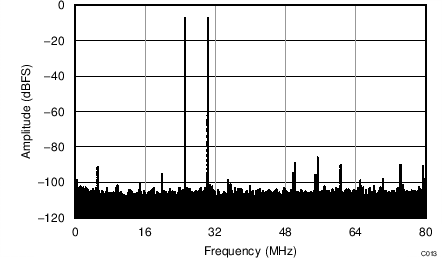

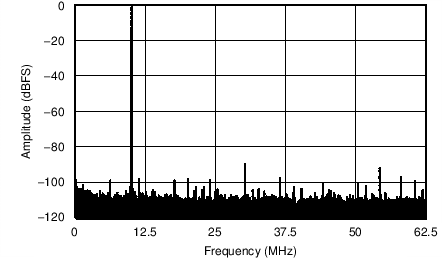

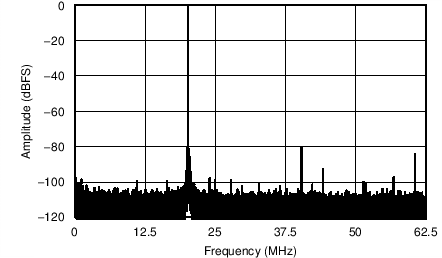

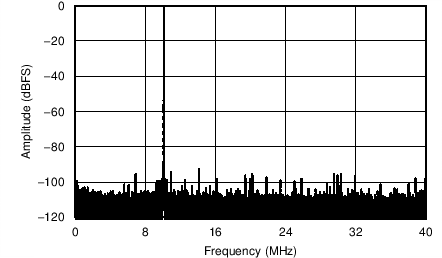

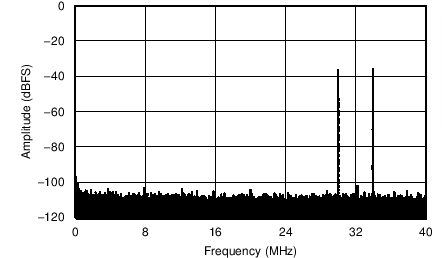

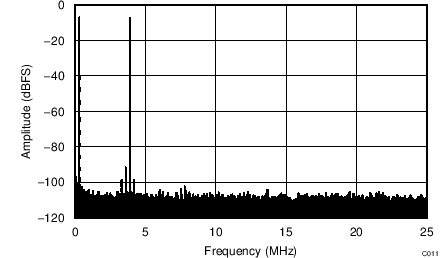

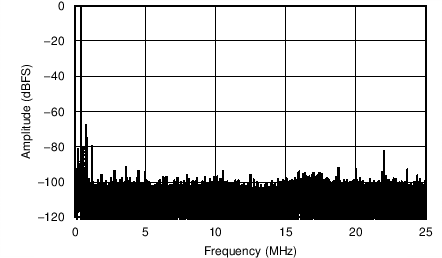

| fS = 80 MSPS, SNR = 72.4 dBFS, fIN = 10 MHz, SFDR = 96 dBc |

Figure 67. FFT for 10-MHz Input Signal, Dither On

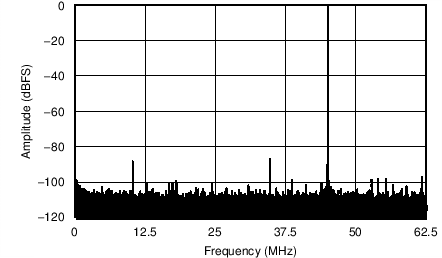

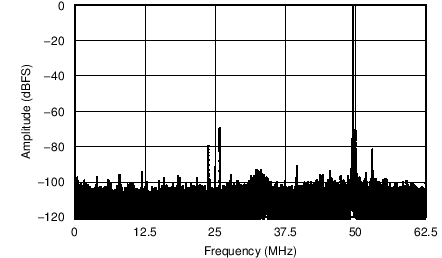

| fS = 80 MSPS, SNR = 72 dBFS, fIN = 70 MHz, SFDR = 95 dBc |

Figure 69. FFT for 70-MHz Input Signal, Dither On

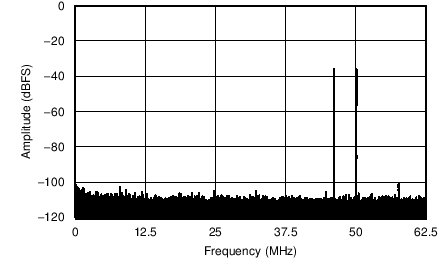

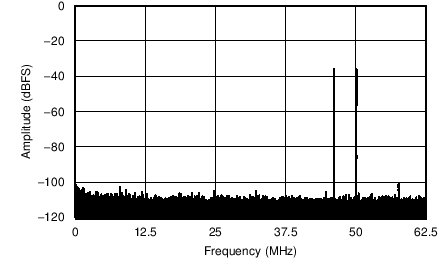

| fS = 80 MSPS, SNR = 70.7 dBFS, fIN = 170 MHz, SFDR = 93 dBc |

Figure 71. FFT for 170-MHz Input Signal, Dither On

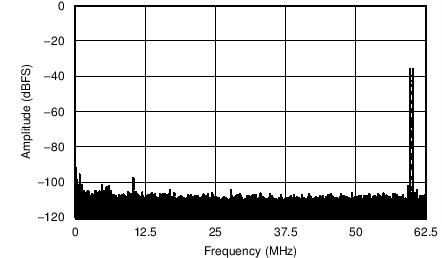

| fS = 80 MSPS, SNR = 69.5 dBFS, fIN = 270 MHz, SFDR = 76 dBc |

Figure 73. FFT for 270-MHz Input Signal, Dither On

| fS = 80 MSPS, SNR = 63.2 dBFS, fIN = 450 MHz, SFDR = 67 dBc |

Figure 75. FFT for 450-MHz Input Signal, Dither On

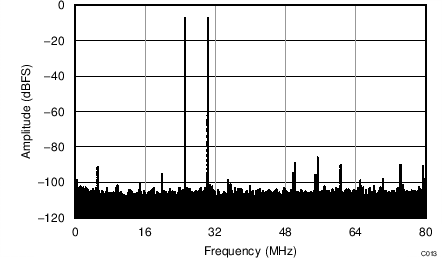

| fS = 80 MSPS, IMD = 93 dBFS, fIN1 = 46 MHz, fIN2 = 50 MHz, SFDR = 98 dBFS |

Figure 77. FFT for Two-Tone Input Signal

(–7 dBFS at 46 MHz and 50 MHz)

| fS = 80 MSPS, IMD = 88 dBFS, fIN1 = 185 MHz, fIN2 = 190 MHz, SFDR = 94 dBFS |

Figure 79. FFT for Two-Tone Input Signal

(–7 dBFS at 185 MHz and 190 MHz)

Figure 81. IMD vs Input Amplitude (46 MHz and 50 MHz)

Figure 81. IMD vs Input Amplitude (46 MHz and 50 MHz)

Figure 83. SNR vs Input Frequency

Figure 83. SNR vs Input Frequency

Figure 85. SNR vs Digital Gain and Input Frequency

Figure 85. SNR vs Digital Gain and Input Frequency

Figure 87. Performance Across Input Amplitude (30 MHz)

Figure 87. Performance Across Input Amplitude (30 MHz)

Figure 89. Performance vs Input Common-Mode Voltage

Figure 89. Performance vs Input Common-Mode Voltage

(30 MHz)

Figure 91. SFDR vs AVDD Supply and Temperature

Figure 91. SFDR vs AVDD Supply and Temperature

Figure 93. SFDR vs DVDD Supply and Temperature

Figure 93. SFDR vs DVDD Supply and Temperature

Figure 95. Performance vs Clock Amplitude (40 MHz)

Figure 95. Performance vs Clock Amplitude (40 MHz)

Figure 97. Performance vs Clock Duty Cycle (40 MHz)

Figure 97. Performance vs Clock Duty Cycle (40 MHz)

Figure 99. Idle Channel Histogram

Figure 99. Idle Channel Histogram

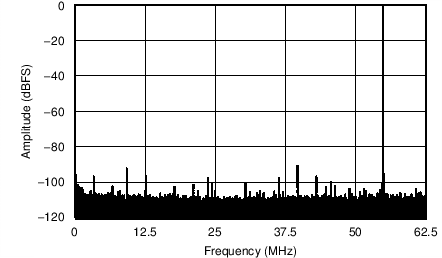

| fS = 80 MSPS, SNR = 73 dBFS, fIN = 10 MHz, SFDR = 90 dBc |

Figure 68. FFT for 10-MHz Input Signal, Dither Off

| fS = 80 MSPS, SNR = 72.5 dBFS, fIN = 70 MHz, SFDR = 89 dBc |

Figure 70. FFT for 70-MHz Input Signal, Dither Off

| fS = 80 MSPS, SNR = 71.4 dBFS, fIN = 10 MHz, SFDR = 90 dBc |

Figure 72. FFT for 170-MHz Input Signal, Dither Off

| fS = 80 MSPS, SNR = 69.8 dBFS, fIN = 270 MHz, SFDR = 75 dBc |

Figure 74. FFT for 270-MHz Input Signal, Dither Off

| fS = 80 MSPS, SNR = 64.1 dBFS, fIN = 450 MHz, SFDR = 67 dBc |

Figure 76. FFT for 450-MHz Input Signal, Dither Off

| fS = 80 MSPS, IMD = 101 dBFS, fIN1 = 46 MHz, fIN2 = 50 MHz, SFDR = 106 dBFS |

Figure 78. FFT for Two-Tone Input Signal

(–36 dBFS at 46 MHz and 50 MHz)

| fS = 80 MSPS, IMD = 99 dBFS, fIN1 = 185 MHz, fIN2 = 190 MHz, SFDR = 102 dBFS |

Figure 80. FFT for Two-Tone Input Signal

(–36 dBFS at 185 MHz and 190 MHz)

Figure 82. IMD vs Input Amplitude (185 MHz and 190 MHz)

Figure 82. IMD vs Input Amplitude (185 MHz and 190 MHz)

Figure 84. SFDR vs Input Frequency

Figure 84. SFDR vs Input Frequency

Figure 86. SFDR vs Digital Gain and Input Frequency

Figure 86. SFDR vs Digital Gain and Input Frequency

Figure 88. Performance Across Input Amplitude (170 MHz)

Figure 88. Performance Across Input Amplitude (170 MHz)

Figure 90. Performance vs Input Common-Mode Voltage (170 MHz)

Figure 90. Performance vs Input Common-Mode Voltage (170 MHz)

Figure 92. SNR vs AVDD Supply and Temperature

Figure 92. SNR vs AVDD Supply and Temperature

Figure 94. SNR vs DVDD Supply and Temperature

Figure 94. SNR vs DVDD Supply and Temperature

Figure 96. Performance vs Clock Amplitude (150 MHz)

Figure 96. Performance vs Clock Amplitude (150 MHz)

Figure 98. Performance vs Clock Duty Cycle (150 MHz)

Figure 98. Performance vs Clock Duty Cycle (150 MHz)

7.18 Typical Characteristics: ADC34J42

Typical values are at TA= 25°C, ADC sampling rate = 50 MSPS, 50% clock duty cycle, AVDD = DVDD = 1.8 V, –1-dBFS differential input, 2-VPP full-scale, and 32k-point FFT, unless otherwise noted.

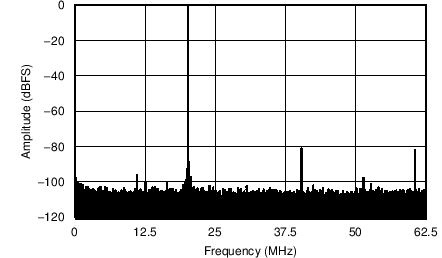

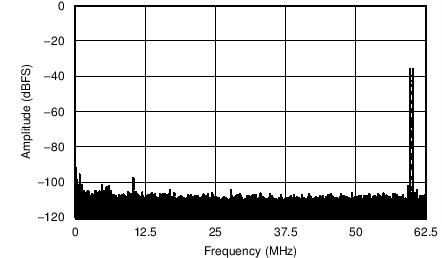

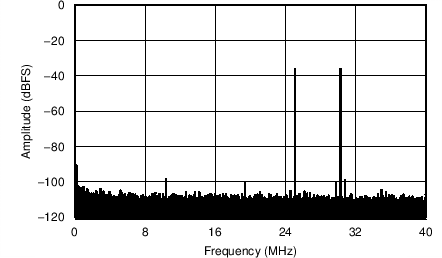

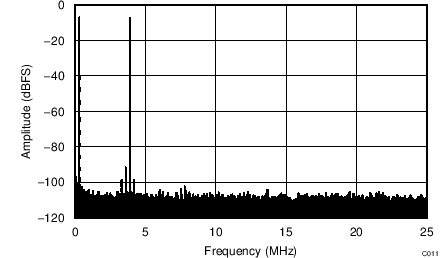

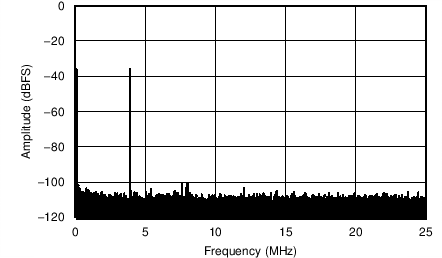

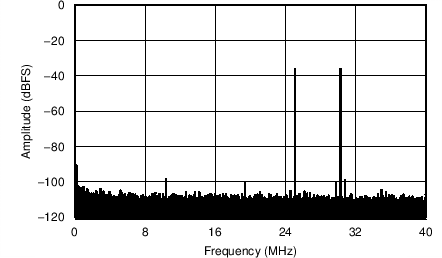

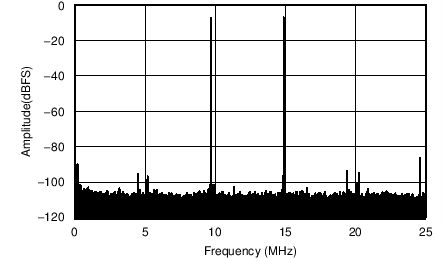

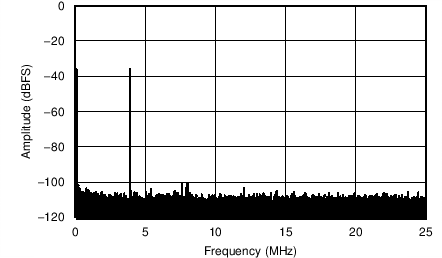

| fS = 50 MSPS, SNR = 72.3 dBFS, fIN = 10 MHz, SFDR = 95 dBc |

Figure 100. FFT for 10-MHz Input Signal, Dither On

| fS = 50 MSPS, SNR = 71.8 dBFS, fIN = 70 MHz, SFDR = 93 dBc |

Figure 102. FFT for 70-MHz Input Signal, Dither On

| fS = 50 MSPS, SNR = 70.8 dBFS, fIN = 170 MHz, SFDR = 87 dBc |

Figure 104. FFT for 170-MHz Input Signal, Dither On

| fS = 50 MSPS, SNR = 69.5 dBFS, fIN = 270 MHz, SFDR = 76 dBc |

Figure 106. FFT for 270-MHz Input Signal, Dither On

| fS = 50 MSPS, SNR = 66.3 dBFS, fIN = 450 MHz, SFDR = 63 dBc |

Figure 108. FFT for 450-MHz Input Signal, Dither On

| fS = 50 MSPS, IMD = 93 dBFS, fIN1 = 46 MHz, fIN2 = 50 MHz, SFDR = 96 dBFS |

Figure 110. FFT for Two-Tone Input Signal

(–7dBFS at 46 MHz and 50 MHz)

| fS = 50 MSPS, IMD = 86 dBFS, fIN1 = 185 MHz, fIN2 = 190 MHz, SFDR = 92 dBFS |

Figure 112. FFT for Two-Tone Input Signal

(–7 dBFS at 185 MHz and 190 MHz)

Figure 114. IMD vs Input Amplitude (46 MHz and 50 MHz)

Figure 114. IMD vs Input Amplitude (46 MHz and 50 MHz)

Figure 116. SNR vs Input Frequency

Figure 116. SNR vs Input Frequency

Figure 118. SNR vs Digital Gain and Input Frequency

Figure 118. SNR vs Digital Gain and Input Frequency

Figure 120. Performance Across Input Amplitude (30 MHz)

Figure 120. Performance Across Input Amplitude (30 MHz)

Figure 122. Performance vs Input Common-Mode Voltage (30 MHz)

Figure 122. Performance vs Input Common-Mode Voltage (30 MHz)

Figure 124. SFDR vs AVDD Supply and Temperature

Figure 124. SFDR vs AVDD Supply and Temperature

Figure 126. SFDR vs DVDD Supply and Temperature

Figure 126. SFDR vs DVDD Supply and Temperature

Figure 128. Performance vs Clock Amplitude (40 MHz)

Figure 128. Performance vs Clock Amplitude (40 MHz)

Figure 130. Performance vs Clock Duty Cycle (40 MHz)

Figure 130. Performance vs Clock Duty Cycle (40 MHz)

Figure 132. Idle Channel Histogram

Figure 132. Idle Channel Histogram

| fS = 50 MSPS, SNR = 72.9 dBFS, fIN = 10 MHz, SFDR = 89 dBc |

Figure 101. FFT for 10-MHz Input Signal, Dither Off

| fS = 50 MSPS, SNR = 72.3 dBFS, fIN = 70 MHz, SFDR = 87 dBc |

Figure 103. FFT for 70-MHz Input Signal, Dither Off

| fS = 50 MSPS, SNR = 71.2 dBFS, fIN = 170 MHz, SFDR = 86 dBc |

Figure 105. FFT for 170-MHz Input Signal, Dither Off

| fS = 50 MSPS, SNR = 69.6 dBFS, fIN = 270 MHz, SFDR = 76 dBc |

Figure 107. FFT for 270-MHz Input Signal, Dither Off

| fS = 50 MSPS, SNR = 66.9 dBFS, fIN = 450 MHz, SFDR = 63 dBc |

Figure 109. FFT for 450-MHz Input Signal, Dither Off

| fS = 50 MSPS, IMD = 101 dBFS, fIN1 = 46 MHz, fIN2 = 50 MHz, SFDR = 106 dBFs |

Figure 111. FFT for Two-Tone Input Signal

(–36 dBFS at 46 MHz and 50 MHz)

| fS = 50 MSPS, IMD = 99 dBFS, fIN1 = 185 MHz, fIN2 = 190 MHz, SFDR = 102 dBFs |

Figure 113. FFT for Two-Tone Input Signal

(–36 dBFS at 185 MHz and 190 MHz)

Figure 115. IMD vs Input Amplitude (185 MHz and 190 MHz)

Figure 115. IMD vs Input Amplitude (185 MHz and 190 MHz)

Figure 117. SFDR vs Input Frequency

Figure 117. SFDR vs Input Frequency

Figure 119. SFDR vs Digital Gain and Input Frequency

Figure 119. SFDR vs Digital Gain and Input Frequency

Figure 121. Performance Across Input amplitude (170 MHz)

Figure 121. Performance Across Input amplitude (170 MHz)

Figure 123. Performance vs Input Common-Mode Voltage (170 MHz)

Figure 123. Performance vs Input Common-Mode Voltage (170 MHz)

Figure 125. SNR vs AVDD Supply and Temperature

Figure 125. SNR vs AVDD Supply and Temperature

Figure 127. SNR vs DVDD Supply and Temperature

Figure 127. SNR vs DVDD Supply and Temperature

Figure 129. Performance vs Clock Amplitude (150 MHz)

Figure 129. Performance vs Clock Amplitude (150 MHz)

Figure 131. Performance vs Clock Duty Cycle (150 MHz)

Figure 131. Performance vs Clock Duty Cycle (150 MHz)

7.19 Typical Characteristics: Common Plots

Typical values are at TA= 25°C, ADC sampling rate = 160 MSPS, 50% clock duty cycle, AVDD = DVDD = 1.8 V, –1-dBFS differential input, 2-VPP full-scale, and 32k-point FFT, unless otherwise noted.

| fS = 160 MSPS, fCM = 10 MHz, 50 mVPP, fIN = 30 MHz, Amplitude (fIN + fCM ) = –98 dBFS, Amplitude (fIN – fCM ) = –91 dBFS |

Figure 133. CMRR FFT

| fS = 160 MSPS, fPSRR = 5 MHz, 50 mVPP, fIN = 30 MHz, Amplitude (fIN + fPSRR ) = –65 dBFS, Amplitude (fIN – fPSRR ) = –67 dBFS |

Figure 135. PSRR FFT for AVDD Supply

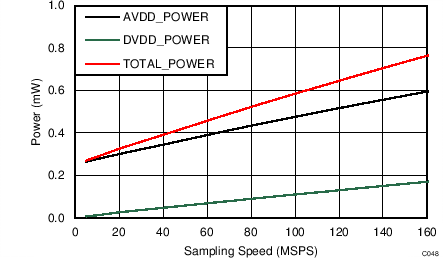

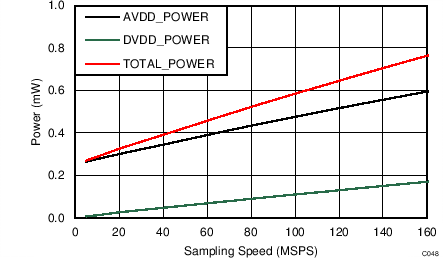

Figure 137. Power vs Sampling Frequency 20x Mode

Figure 137. Power vs Sampling Frequency 20x Mode

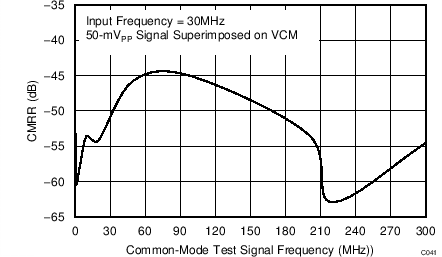

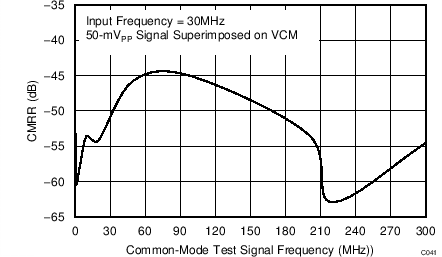

Figure 134. CMRR vs Test Signal Frequency

Figure 134. CMRR vs Test Signal Frequency

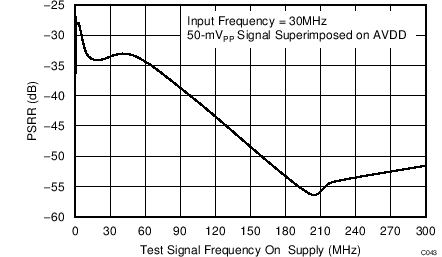

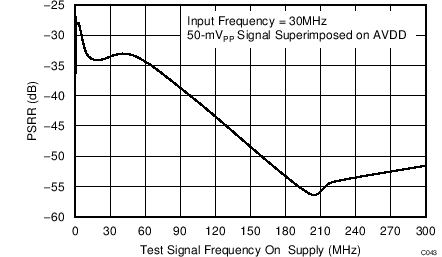

Figure 136. PSRR vs Test Signal Frequency

Figure 136. PSRR vs Test Signal Frequency

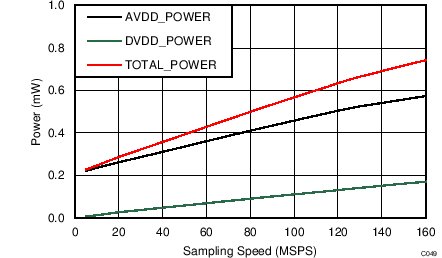

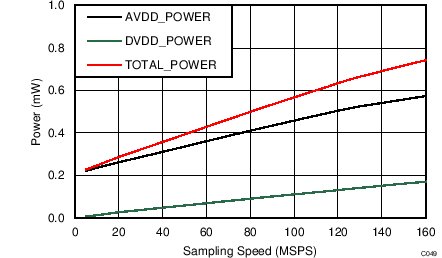

Figure 138. Power vs Sampling Frequency 40x Mode

Figure 138. Power vs Sampling Frequency 40x Mode

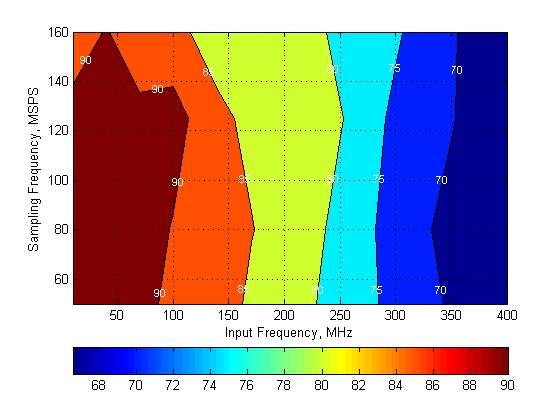

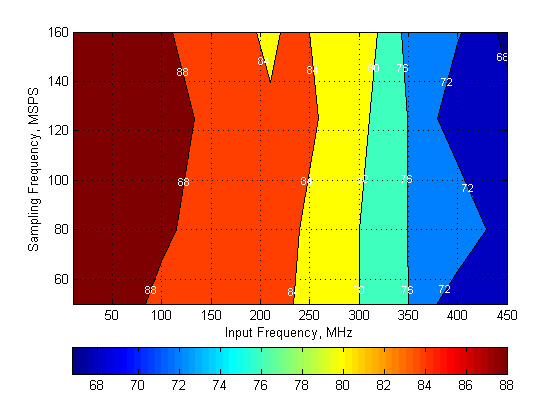

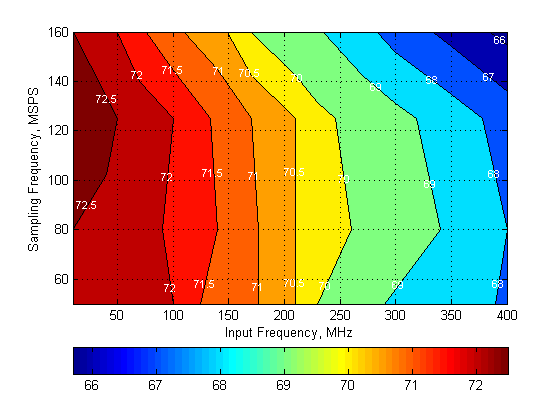

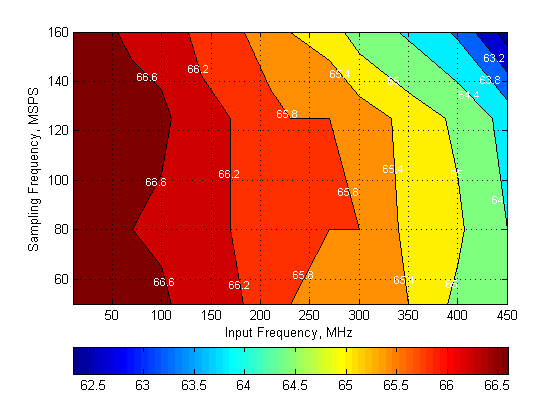

7.20 Typical Characteristics: Contour Plots

Typical values are at TA= 25°C, 50% clock duty cycle, AVDD = DVDD = 1.8 V, –1-dBFS differential input, 2-VPP full-scale, and 32k-point FFT, unless otherwise noted.