SBAS650C May 2014 – April 2021 AFE4403

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Family Options

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

- 9 Application Information Disclaimer

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- YZP|36

Thermal pad, mechanical data (Package|Pins)

Orderable Information

9.2.2 Detailed Design Procedure

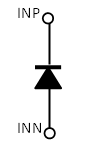

Refer to LED Configurations for different ways to connect the LEDs to the TXP, TXN, and TX3 pins. The photodiode (shown in Figure 9-2) receives light from both the Red and IR phases and usually has good sensitivities at both these wavelengths.

Figure 9-2 Photodiode

Figure 9-2 PhotodiodeThe photodiode connected as shown in Figure 9-2 operates in zero bias because of the negative feedback from the transimpedance amplifier. The signal current generated by the photodiode is converted into a voltage by the transimpedance amplifier, which has a programmable transimpedance gain. The rest of the signal chain then presents a voltage to the ADC. The full-scale output of the transimpedance amplifier is ±1 V and the full-scale input to the ADC is ±1.2 V. An automatic gain control (AGC) loop can be used to set the target dc voltage at the ADC input to approximately 50% of its full-scale. Such an AGC loop can control a combination of the LED current and TIA gain to achieve this target value.