SBAS602H December 2012 – October 2014 AFE4490

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

- 9 Applications and Implementation

- 10Power-Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RHA|40

Thermal pad, mechanical data (Package|Pins)

Orderable Information

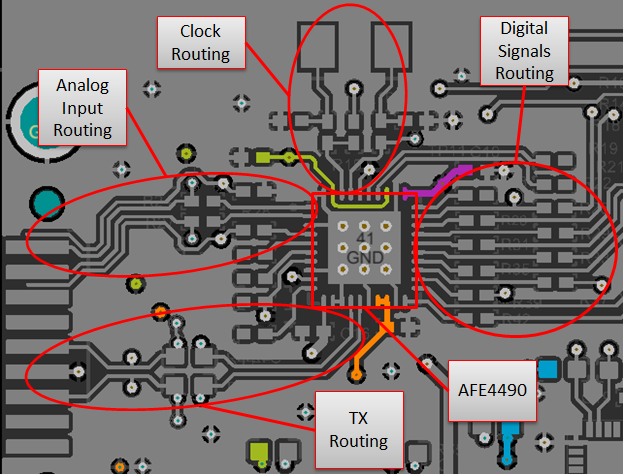

11 Layout

11.1 Layout Guidelines

Some key layout guidelines are:

- TXP, TXN are fast switching lines and must be routed away from sensitive reference lines as well as from the INP, INN inputs.

- If required to route long, TI recommends that the VCM be used as a shield for the INP, INN lines.

- The device can draw high switching currents from the LED_DRV_SUP pin. Therefore, having a decoupling capacitor electrically close to the pin is recommended.

11.2 Layout Example

Figure 139. Typical Layout of the AFE4490 Board

Figure 139. Typical Layout of the AFE4490 Board