SLPS350A February 2014 – January 2017 CSD87333Q3D

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Specifications

- 6 Applications

- 7 Recommended PCB Design Overview

- 8 Thermal Performance

- 9 Device and Documentation Support

- 10Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- DPB|8

Thermal pad, mechanical data (Package|Pins)

Orderable Information

10 Mechanical, Packaging, and Orderable Information

The following pages include mechanical packaging and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

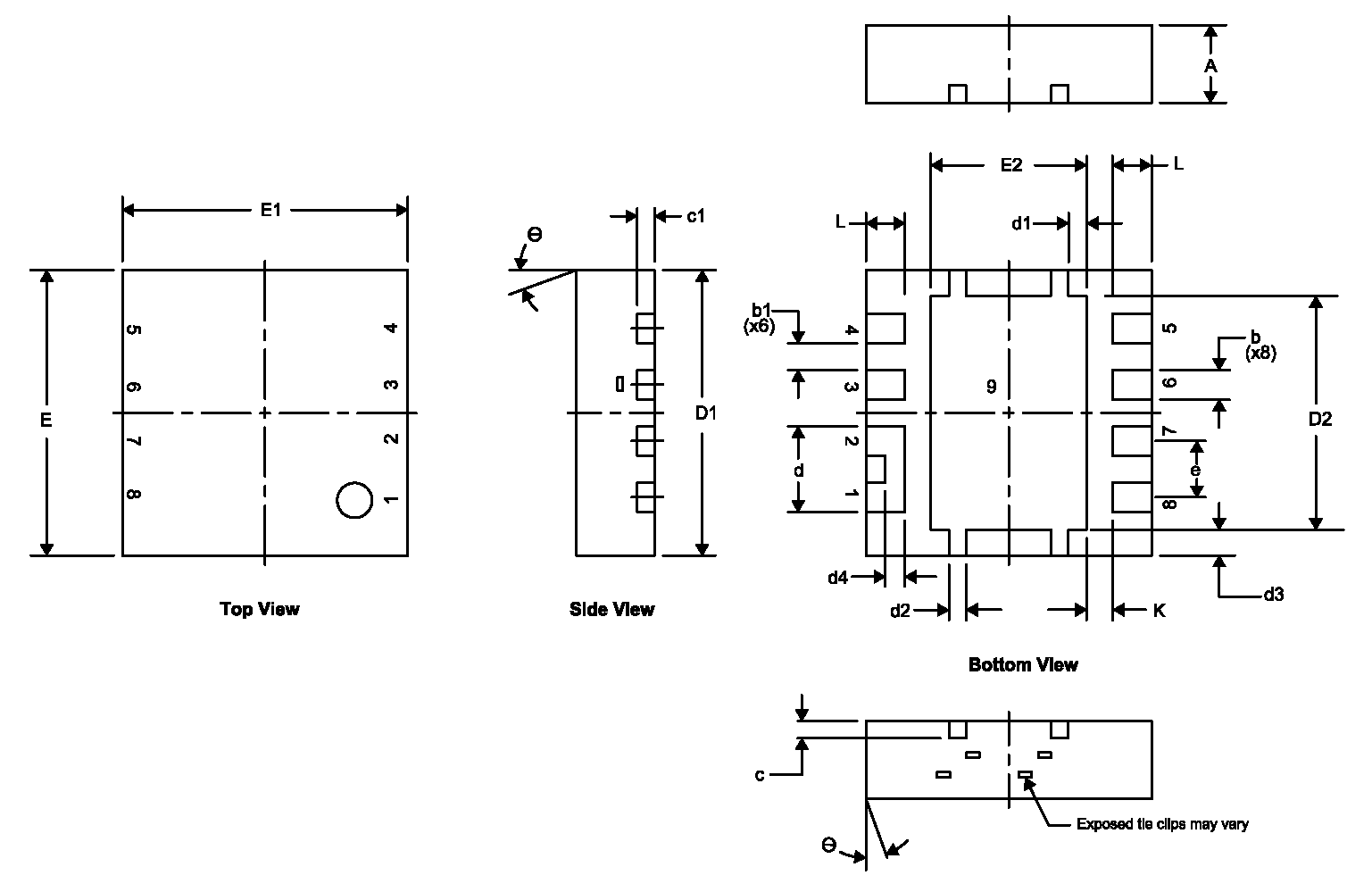

10.1 Q3D Package Dimensions

| DIM | MILLIMETERS | INCHES | ||

|---|---|---|---|---|

| MIN | MAX | MIN | MAX | |

| A | 0.850 | 1.050 | 0.033 | 0.041 |

| b | 0.280 | 0.400 | 0.011 | 0.016 |

| b1 | 0.310 NOM | 0.012 NOM | ||

| c | 0.150 | 0.250 | 0.006 | 0.010 |

| c1 | 0.150 | 0.250 | 0.006 | 0.010 |

| d | 0.940 | 1.040 | 0.037 | 0.041 |

| d1 | 0.160 | 0.260 | 0.006 | 0.010 |

| d2 | 0.150 | 0.250 | 0.006 | 0.010 |

| d3 | 0.250 | 0.350 | 0.010 | 0.014 |

| d4 | 0.175 | 0.275 | 0.007 | 0.011 |

| D1 | 3.200 | 3.400 | 0.126 | 0.134 |

| D2 | 2.650 | 2.750 | 0.104 | 0.108 |

| E | 3.200 | 3.400 | 0.126 | 0.134 |

| E1 | 3.200 | 3.400 | 0.126 | 0.134 |

| E2 | 1.750 | 1.850 | 0.069 | 0.073 |

| e | 0.650 TYP | 0.026 TYP | ||

| L | 0.400 | 0.500 | 0.016 | 0.020 |

| θ | 0.000 | — | — | — |

| K | 0.300 TYP | 0.012 TYP | ||

10.2 Pinout Configuration

Table 1. Pinout Configuration

| POSITION | DESIGNATION |

|---|---|

| Pin 1 | VIN |

| Pin 2 | VIN |

| Pin 3 | TG |

| Pin 4 | TGR |

| Pin 5 | BG |

| Pin 6 | VSW |

| Pin 7 | VSW |

| Pin 8 | VSW |

| Pin 9 | PGND |

10.3 Land Pattern Recommendation

NOTE:

Dimensions are in mm (in).10.4 Stencil Recommendation

NOTE:

Dimensions are in mm (in).For recommended circuit layout for PCB designs, see Reducing Ringing Through PCB Layout Techniques (SLPA005).

10.5 Q3D Tape and Reel Information

NOTES:

1. 10-sprocket hole-pitch cumulative tolerance ± 0.2. 2. Camber not to exceed 1 mm in 100 mm, noncumulative over 250 mm.

3. Material: black static-dissipative polystyrene.

4. All dimensions are in mm, unless otherwise specified.

5. Thickness: 0.3 ± 0.05 mm.

6. MSL1 260°C (IR and convection) PbF reflow compatible.