SNOSDB8A June 2021 – December 2021 LM74701-Q1

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- DDF|8

Thermal pad, mechanical data (Package|Pins)

Orderable Information

9.4 OR-ing Application Configuration

Basic redundant power architecture comprises of two or more voltage or power supply sources driving a single load. In its simplest form, the OR-ing solution for redundant power supplies consists of Schottky OR-ing diodes that protect the system against an input power supply fault condition. A diode OR-ing device provides effective and low cost solution with few components. However, the diodes forward voltage drops affects the efficiency of the system permanently, because each diode in an OR-ing application spends most of its time in forward conduction mode. These power losses increase the requirements for thermal management and allocated board space.

The LM74701-Q1 ICs combined with external N-Channel MOSFETs can be used in OR-ing Solution as shown in Figure 9-12. The forward diode drop is reduced as the external N-Channel MOSFET is turned ON during normal operation. LM74701-Q1 quickly detects the reverse current, pulls down the MOSFET gate fast, leaving the body diode of the MOSFET to block the reverse current flow. An effective OR-ing solution must be extremely fast to limit the reverse current amount and duration. The LM74701-Q1 devices in OR-ing configuration constantly sense the voltage difference between Anode and Cathode pins, which are the voltage levels at the power sources (VIN1, VIN2) and the common load point respectively. The source to drain voltage VDS for each MOSFET is monitored by the Anode and Cathode pins of the LM74701-Q1. A fast comparator shuts down the gate drive through a fast pulldown within 0.45 μs (typical) as soon as V(IN) – V(OUT) falls below –11 mV. The fast comparator turns on the Gate with 11 mA gate charge current after the differential forward voltage V(IN) – V(OUT) exceeds 50 mV.

Figure 9-12 Typical OR-ing Application

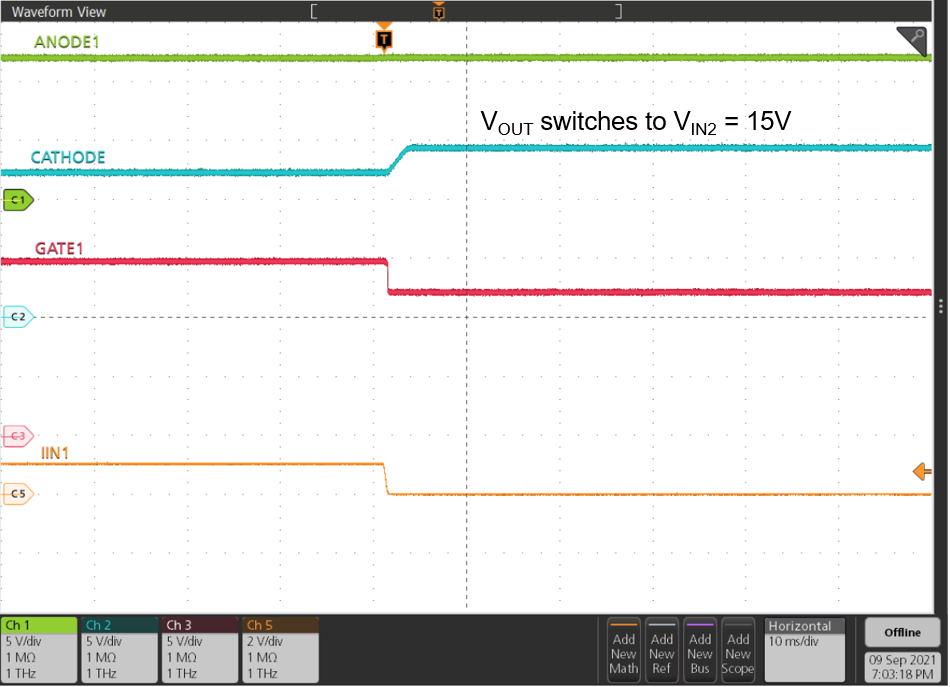

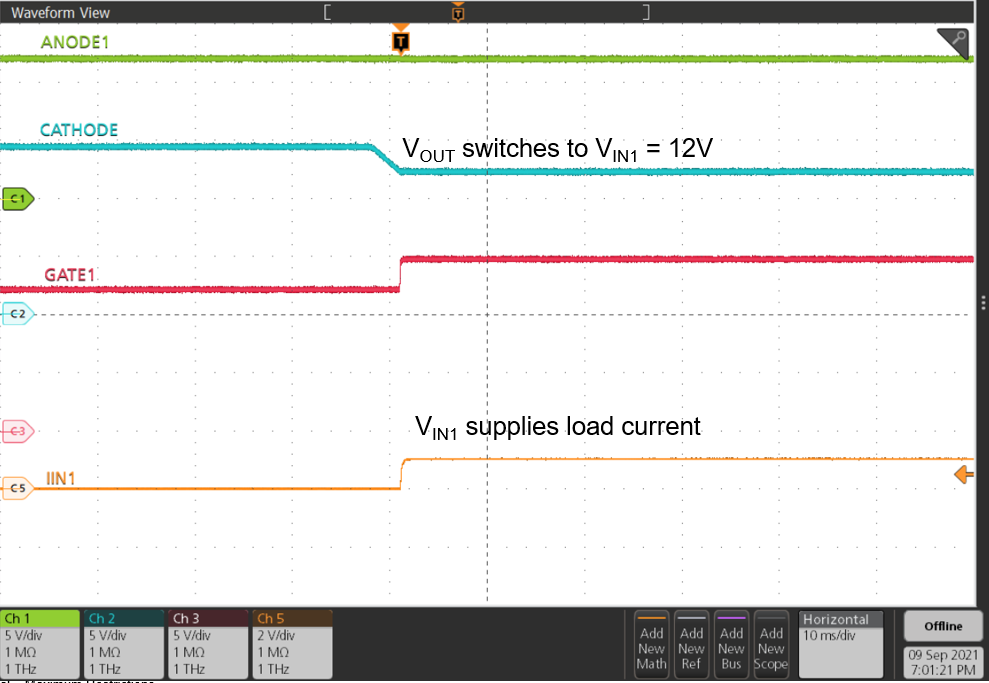

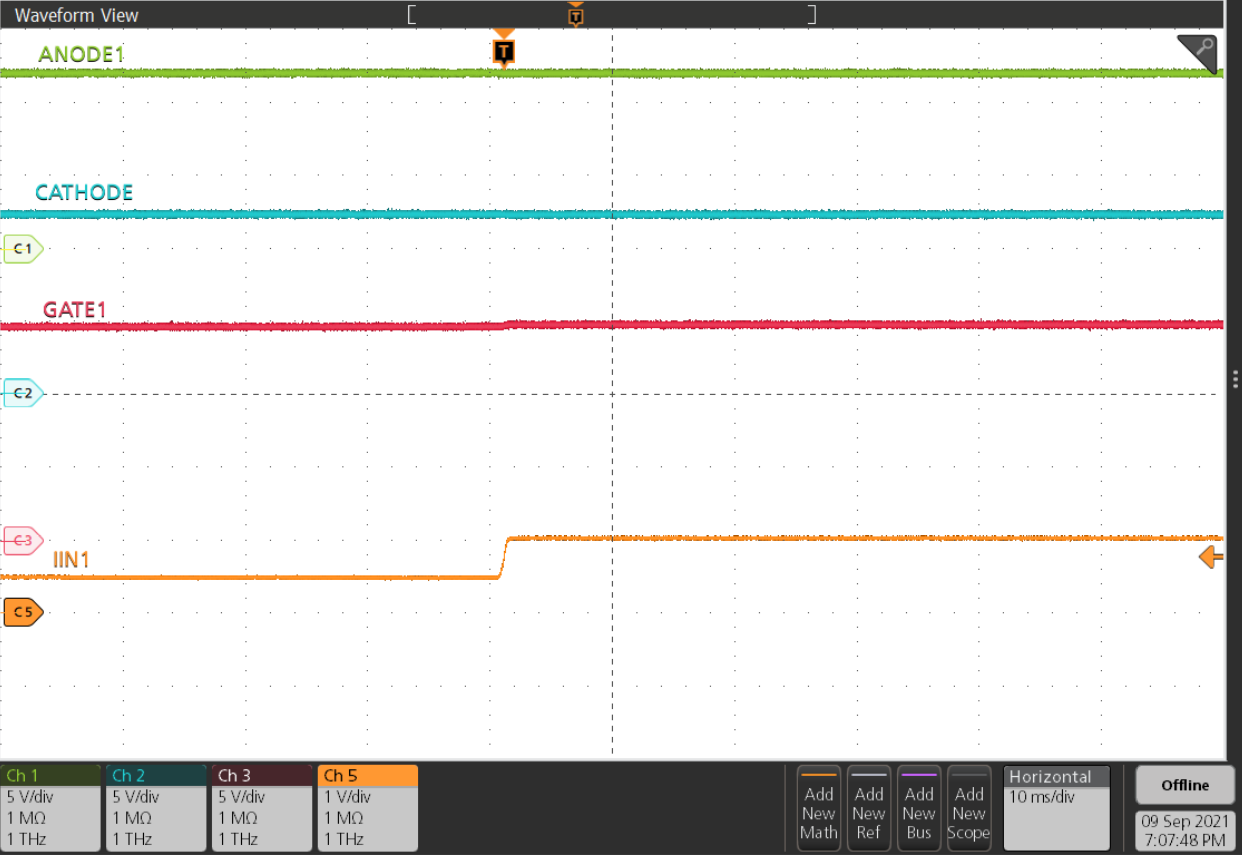

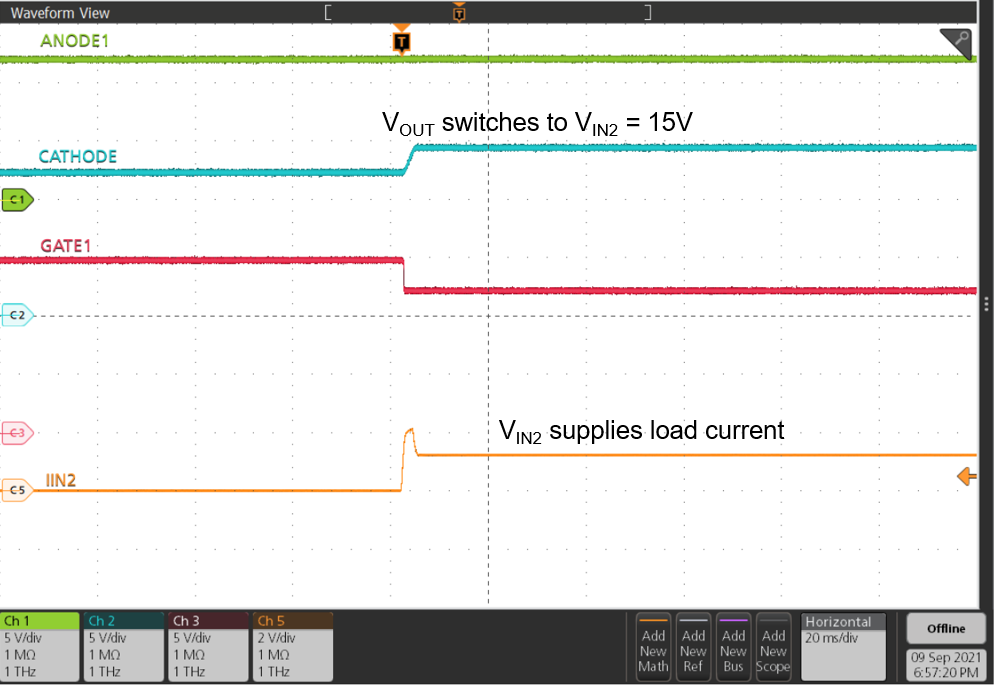

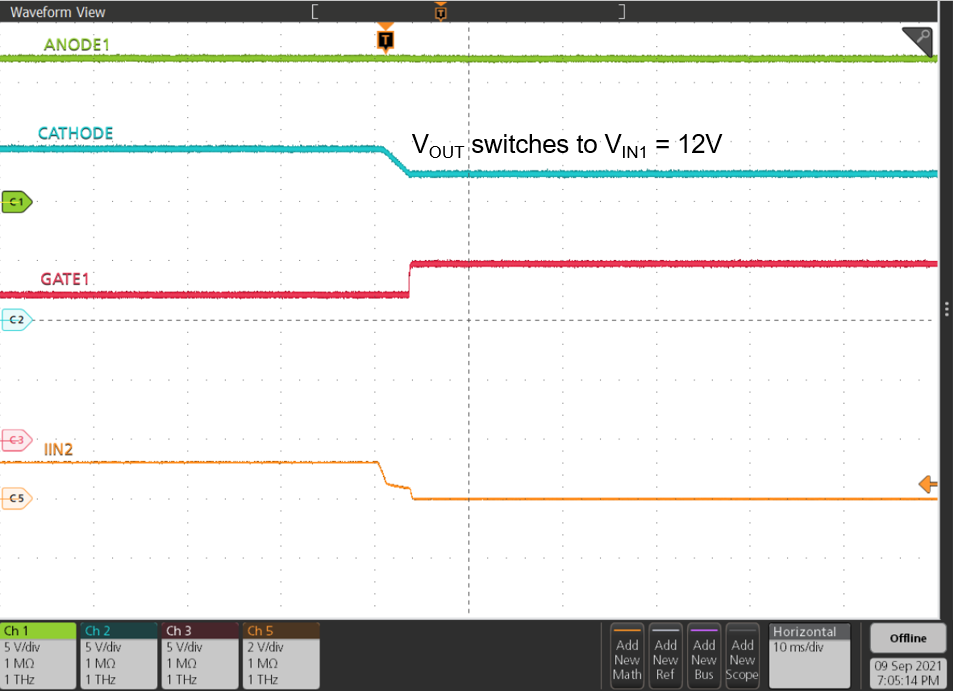

Figure 9-12 Typical OR-ing ApplicationFigure 9-13 to Figure 9-16 show the smooth switch over between two power supply rails VIN1 at 12 V and VIN2 at 15 V. Figure 9-17 and Figure 9-18 illustrate the performance when VIN2 fails. LM74701-Q1 controlling VIN2 power rail turns off quickly, so that the output remains uninterrupted and VIN1 is protected from VIN2 failure.

| Time (10 ms/DIV) |

| Time (10 ms/DIV) |

| Time (10 ms/DIV) |

| Time (20 ms/DIV) |

| Time (10 ms/DIV) |

| Time (20 ms/DIV) |

LM74701-Q1 has VDS clamp mode of operation where device detects the voltage difference between CATHODE and ANODE and turns on the external FET in active clamp region when the V(OUT) – V(IN) crosses the VDSCLAMP threshold. So LM74701-Q1 can be used in ORing applications where worst case V(OUT) – V(IN) is less than device VDSCLAMP minimum specification as mentioned in the Electrical Characteristics table.