SNVS716H March 2011 – February 2016 LMZ12008

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specification

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- NDY|11

Thermal pad, mechanical data (Package|Pins)

Orderable Information

7 Detailed Description

7.1 Overview

The architecture used is an internally compensated emulated peak current mode control, based on a monolithic synchronous SIMPLE SWITCHER core capable of supporting high load currents. The output voltage is maintained through feedback compared with an internal 0.8-V reference. For emulated peak current-mode, the valley current is sampled on the down-slope of the inductor current. This is used as the DC value of current to start the next cycle.

The primary application for emulated peak current-mode is high input voltage to low output voltage operating at a narrow duty cycle. By sampling the inductor current at the end of the switching cycle and adding an external ramp, the minimum ON-time can be significantly reduced, without the need for blanking or filtering which is normally required for peak current-mode control.

7.2 Functional Block Diagram

7.3 Feature Description

7.3.1 Output Overvoltage Protection

If the voltage at FB is greater than a 0.86-V internal reference, the output of the error amplifier is pulled toward ground, causing VOUT to fall.

7.3.2 Current Limit

The LMZ12008 is protected by both low-side (LS) and high-side (HS) current limit circuitry. The LS current limit detection is carried out during the OFF-time by monitoring the current through the LS synchronous MOSFET. Referring to the Functional Block Diagram, when the top MOSFET is turned off, the inductor current flows through the load, the PGND pin and the internal synchronous MOSFET. If this current exceeds 13 A (typical) the current limit comparator disables the start of the next switching period. Switching cycles are prohibited until current drops below the limit.

NOTE

DC current limit is dependent on duty cycle as illustrated in the graph in the Typical Characteristics section.

The HS current limit monitors the current of top side MOSFET. Once HS current limit is detected (16 A typical) , the HS MOSFET is shutoff immediately, until the next cycle. Exceeding HS current limit causes VOUT to fall. Typical behavior of exceeding LS current limit is that fSW drops to 1/2 of the operating frequency.

7.3.3 Thermal Protection

The junction temperature of the LMZ12008 must not be allowed to exceed its maximum ratings. Thermal protection is implemented by an internal Thermal Shutdown circuit which activates at 165°C (typical) causing the device to enter a low power standby state. In this state the main MOSFET remains off causing VOUT to fall, and additionally the CSS capacitor is discharged to ground. Thermal protection helps prevent catastrophic failures for accidental device overheating. When the junction temperature falls back below 150°C (typical hysteresis = 15°C) the SS pin is released, VOUT rises smoothly, and normal operation resumes.

Applications requiring maximum output current especially those at high input voltage may require additional derating at elevated temperatures.

7.3.4 Prebiased Start-Up

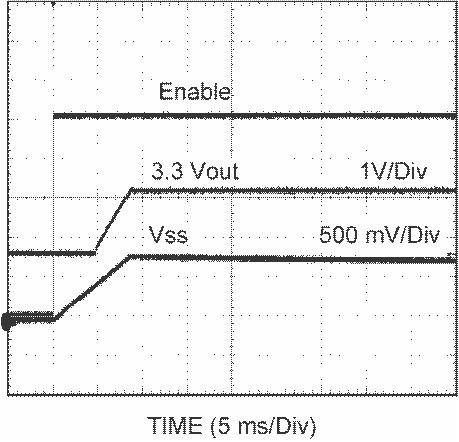

The LMZ12008 will properly start up into a prebiased output. This start-up situation is common in multiple rail logic applications where current paths may exist between different power rails during the start-up sequence. Figure 45 shows proper behavior in this mode. Trace one is Enable going high. Trace two is 1.8-V prebias rising to 3.3 V. Trace three is the SS voltage with a CSS= 0.47 µF. Rise-time determined by CSS.

Figure 45. Prebiased Start-Up

Figure 45. Prebiased Start-Up

7.4 Device Functional Modes

7.4.1 Discontinuous Conduction and Continuous Conduction Modes

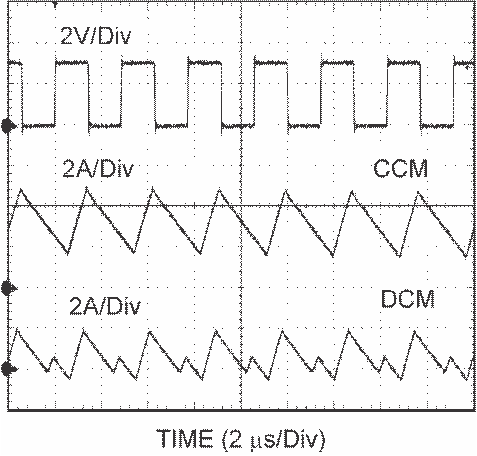

At light load the regulator will operate in discontinuous conduction mode (DCM). With load currents above the critical conduction point, it will operate in continuous conduction mode (CCM). When operating in DCM, inductor current is maintained to an average value equaling IOUT. In DCM the low-side switch will turn off when the inductor current falls to zero, this causes the inductor current to resonate. Although it is in DCM, the current is allowed to go slightly negative to charge the bootstrap capacitor.

In CCM, current flows through the inductor through the entire switching cycle and never falls to zero during the OFF-time.

Figure 46 is a comparison pair of waveforms showing both the CCM (upper) and DCM operating modes.

The approximate formula for determining the DCM/CCM boundary is as follows:

The inductor internal to the module is 2.2 μH. This value was chosen as a good balance between low and high input voltage applications. The main parameter affected by the inductor is the amplitude of the inductor ripple current (ΔiL). ΔiL can be calculated with:

where

- VIN is the maximum input voltage

- and fSW is typically 359 kHz.

If the output current IOUT is determined by assuming that IOUT = IL, the higher and lower peak of ΔiL can be determined.