JAJSJR7B August 2022 – October 2023 DRV8462

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 ピン構成および機能

- 6 仕様

-

7 詳細説明

- 7.1 概要

- 7.2 機能ブロック図

- 7.3

機能説明

- 7.3.1 動作インターフェイス

- 7.3.2 ステッパ・モーター・ドライバの電流定格

- 7.3.3 PWM モーター・ドライバ

- 7.3.4 マイクロステッピング・インデクサ

- 7.3.5 インデクサ出力

- 7.3.6 自動マイクロステッピング・モード

- 7.3.7 カスタム・マイクロステッピング表

- 7.3.8 電流レギュレーション

- 7.3.9 内部リファレンス電圧

- 7.3.10 静止電力節約モード

- 7.3.11 電流レギュレーション減衰モード

- 7.3.12 外付け抵抗による電流検出

- 7.3.13 サイレント・ステップ減衰モード

- 7.3.14 自動トルクの動的電流調整

- 7.3.15 チャージ・ポンプ

- 7.3.16 リニア電圧レギュレータ

- 7.3.17 VCC 電圧電源

- 7.3.18 ロジック・レベル、トライレベル、クワッドレベルのピン構造図

- 7.3.19 スペクトラム拡散

- 7.3.20 保護回路

- 7.3.21 デバイスの機能モード

- 7.4 プログラミング

- 7.5

レジスタ・マップ

- 7.5.1 ステータス・レジスタ

- 7.5.2

制御レジスタ

- 7.5.2.1 CTRL1 (アドレス = 0x04) [デフォルト = 0Fh]

- 7.5.2.2 CTRL2 (アドレス=0x05) [デフォルト=06h]

- 7.5.2.3 CTRL3 (アドレス=0x06) [デフォルト=38h]

- 7.5.2.4 CTRL4 (アドレス=0x07) [デフォルト=49h]

- 7.5.2.5 CTRL5 (アドレス=0x08) [デフォルト=03h]

- 7.5.2.6 CTRL6 (アドレス=0x09) [デフォルト=20h]

- 7.5.2.7 CTRL7 (アドレス=0x0A) [デフォルト=FFh]

- 7.5.2.8 CTRL8 (アドレス=0x0B) [デフォルト=0Fh]

- 7.5.2.9 CTRL9 (アドレス=0x0C) [デフォルト=10h]

- 7.5.2.10 CTRL10 (アドレス=0x0D) [デフォルト=80h]

- 7.5.2.11 CTRL11 (アドレス=0x0E) [デフォルト=FFh]

- 7.5.2.12 CTRL12 (アドレス=0x0F) [デフォルト=20h]

- 7.5.2.13 CTRL13 (アドレス=0x10) [デフォルト=10h]

- 7.5.2.14 CTRL14 (アドレス = 0x3C) [デフォルト = 58h]

- 7.5.3 インデクサ・レジスタ

- 7.5.4

カスタム・マイクロステッピング・レジスタ

- 7.5.4.1 CUSTOM_CTRL1 (アドレス=0x16) [デフォルト=00h]

- 7.5.4.2 CUSTOM_CTRL2 (アドレス=0x17) [デフォルト=00h]

- 7.5.4.3 CUSTOM_CTRL3 (アドレス=0x18) [デフォルト=00h]

- 7.5.4.4 CUSTOM_CTRL4 (アドレス=0x19) [デフォルト=00h]

- 7.5.4.5 CUSTOM_CTRL5 (アドレス=0x1A) [デフォルト=00h]

- 7.5.4.6 CUSTOM_CTRL6 (アドレス=0x1B) [デフォルト=00h]

- 7.5.4.7 CUSTOM_CTRL7 (アドレス=0x1C) [デフォルト=00h]

- 7.5.4.8 CUSTOM_CTRL8 (アドレス=0x1D) [デフォルト=00h]

- 7.5.4.9 CUSTOM_CTRL9 (アドレス=0x1E) [デフォルト=00h]

- 7.5.5

自動トルク・レジスタ

- 7.5.5.1 ATQ_CTRL1 (アドレス=0x1F) [デフォルト=00h]

- 7.5.5.2 ATQ_CTRL2 (アドレス=0x20) [デフォルト=00h]

- 7.5.5.3 ATQ_CTRL3 (アドレス=0x21) [デフォルト=00h]

- 7.5.5.4 ATQ_CTRL4 (アドレス=0x22) [デフォルト=20h]

- 7.5.5.5 ATQ_CTRL5 (アドレス=0x23) [デフォルト=00h]

- 7.5.5.6 ATQ_CTRL6 (アドレス=0x24) [デフォルト=00h]

- 7.5.5.7 ATQ_CTRL7 (アドレス=0x25) [デフォルト=00h]

- 7.5.5.8 ATQ_CTRL8 (アドレス=0x26) [デフォルト=00h]

- 7.5.5.9 ATQ_CTRL9 (アドレス=0x27) [デフォルト=00h]

- 7.5.5.10 ATQ_CTRL10 (アドレス=0x28) [デフォルト=08h]

- 7.5.5.11 ATQ_CTRL11 (アドレス=0x29) [デフォルト=0Ah]

- 7.5.5.12 ATQ_CTRL12 (アドレス=0x2A) [デフォルト=FFh]

- 7.5.5.13 ATQ_CTRL13 (アドレス=0x2B) [デフォルト=05h]

- 7.5.5.14 ATQ_CTRL14 (アドレス=0x2C) [デフォルト=0Fh]

- 7.5.5.15 ATQ_CTRL15 (アドレス=0x2D) [デフォルト=00h]

- 7.5.5.16 ATQ_CTRL16 (アドレス=0x2E) [デフォルト=FFh]

- 7.5.5.17 ATQ_CTRL17 (アドレス=0x2F) [デフォルト=00h]

- 7.5.5.18 ATQ_CTRL18 (アドレス=0x30) [デフォルト=00h]

- 7.5.6 サイレント・ステップ・レジスタ

- 8 アプリケーションと実装

- 9 熱に関する注意事項

- 10電源に関する推奨事項

- 11レイアウト

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

- DDW|44

発注情報

7.3.4 マイクロステッピング・インデクサ

本デバイスの内蔵インデクサ・ ロジックを使用すると、各種マイクロステップ・モードに対応できます。表 7-5 に示すとおり、SPI レジスタの MICROSTEP_MODE ビット、または M0 ピンと M1 ピンを使用してステップ・モードを設定します。

SPI インターフェイス | ハードウェア・インターフェイス | ||

|---|---|---|---|

MICROSTEP_MODE | M0 | M1 | ステップ・モード |

0000b | 0 | 0 | 100% 電流によるフルステップ (2 相励磁) |

0001b | 0 | 330kΩを GND に接続 | 71% 電流によるフルステップ (2 相励磁) |

0010b | 1 | 0 | 非循環 1/2 ステップ |

0011b | ハイ・インピーダンス | 0 | 1/2 ステップ |

0100b | 0 | 1 | 1/4 ステップ |

0101b | 1 | 1 | 1/8 ステップ |

0110b (デフォルト) | ハイ・インピーダンス | 1 | 1/16 ステップ |

0111b | 0 | ハイ・インピーダンス | 1/32 ステップ |

1000b | ハイ・インピーダンス | 330kΩを GND に接続 | 1/64 ステップ |

1001b | ハイ・インピーダンス | ハイ・インピーダンス | 1/128 ステップ |

1010b | 1 | ハイ・インピーダンス | 1/256 ステップ |

SPI インターフェイスで動作している場合、表 7-6 に示すように、このデバイスでは SPI インターフェイス経由でステッピングと方向の変更を行うこともできます。この目的のために、4 つのビットが使用されます。

ビット | 0b (デフォルト) | 1b |

SPI_DIR | ドライバは、DIR ピン入力に基づいて方向を変更します | 方向の変更は、DIR ビットによって異なります |

SPI_STEP | ステッピングは STEP ピンの入力に依存します | ステップの変更は、STEP ビットによって異なります |

DIR | モーターは逆方向に動きます | モーターは順方向に動きます |

STEP | X | インデクサが 1 ステップ進みます。STEP ビットは自己クリアなので、「1」が書き込まれた後で自動的に「0」になります。 |

表 7-7 に、DIR ピンがロジック High または DIR ビットが「1」の場合のフルステップ (71% 電流)、1/2 ステップ、1/4 ステップ、1/8 ステップ動作の相対電流とステップ方向を示します。マイクロステッピングの分解能がより高い場合も同じパターンに従います。AOUT 電流は電気角の正弦、BOUT 電流は電気角の余弦です。正電流は、駆動時に xOUT1 ピンから xOUT2 ピンに流れる電流と定義します。

| 1/8 ステップ | 1/4 ステップ | 1/2 ステップ | フルステップ 71% | AOUT 電流 (フルスケールに対する %) | BOUT 電流 (フルスケールに対する %) | 電気角 (度) |

|---|---|---|---|---|---|---|

| 1 | 1 | 1 | 0% | 100% | 0.00 | |

| 2 | 20% | 98% | 11.25 | |||

| 3 | 2 | 38% | 92% | 22.50 | ||

| 4 | 56% | 83% | 33.75 | |||

| 5 | 3 | 2 | 1 | 71% | 71% | 45.00 |

| 6 | 83% | 56% | 56.25 | |||

| 7 | 4 | 92% | 38% | 67.50 | ||

| 8 | 98% | 20% | 78.75 | |||

| 9 | 5 | 3 | 100% | 0% | 90.00 | |

| 10 | 98% | -20% | 101.25 | |||

| 11 | 6 | 92% | -38% | 112.50 | ||

| 12 | 83% | -56% | 123.75 | |||

| 13 | 7 | 4 | 2 | 71% | -71% | 135.00 |

| 14 | 56% | -83% | 146.25 | |||

| 15 | 8 | 38% | -92% | 157.50 | ||

| 16 | 20% | -98% | 168.75 | |||

| 17 | 9 | 5 | 0% | -100% | 180.00 | |

| 18 | -20% | -98% | 191.25 | |||

| 19 | 10 | -38% | -92% | 202.50 | ||

| 20 | -56% | -83% | 213.75 | |||

| 21 | 11 | 6 | 3 | -71% | -71% | 225.00 |

| 22 | -83% | -56% | 236.25 | |||

| 23 | 12 | -92% | -38% | 247.50 | ||

| 24 | -98% | -20% | 258.75 | |||

| 25 | 13 | 7 | -100% | 0% | 270.00 | |

| 26 | -98% | 20% | 281.25 | |||

| 27 | 14 | -92% | 38% | 292.50 | ||

| 28 | -83% | 56% | 303.75 | |||

| 29 | 15 | 8 | 4 | -71% | 71% | 315.00 |

| 30 | -56% | 83% | 326.25 | |||

| 31 | 16 | -38% | 92% | 337.50 | ||

| 32 | -20% | 98% | 348.75 |

表 7-8 に、DIR = 1 の場合のフルスケール電流 100% でのフルステップ動作を示します。このステッピング・モードは、71% の電流によるフルステップ・モードよりも多くの電力を消費しますが、高いモーター RPM で高トルクを実現できます。

| フルステップ 100% | AOUT 電流 (フルスケールに対する %) | BOUT 電流 (フルスケールに対する %) | 電気角 (度) |

|---|---|---|---|

| 1 | 100 | 100 | 45 |

| 2 | 100 | -100 | 135 |

| 3 | -100 | -100 | 225 |

| 4 | -100 | 100 | 315 |

表 7-9 に、DIR = 1の場合の非循環 1/2 ステップ動作を示します。このステッピング・モードは循環 1/2 ステップ動作よりも多くの電力を消費しますが、高いモーター RPM で高トルクを実現できます。

| 非循環 1/2 ステップ | AOUT 電流 (フルスケールに対する %) | BOUT 電流 (フルスケールに対する %) | 電気角 (度) |

|---|---|---|---|

| 1 | 0 | 100 | 0 |

| 2 | 100 | 100 | 45 |

| 3 | 100 | 0 | 90 |

| 4 | 100 | -100 | 135 |

| 5 | 0 | -100 | 180 |

| 6 | -100 | -100 | 225 |

| 7 | -100 | 0 | 270 |

| 8 | -100 | 100 | 315 |

表 7-10 に示すように、SPI インターフェイスで動作している場合、STEP_EDGE ビットに応じて、STEP アクティブ・エッジを立ち上がりエッジにするか、または立ち上がりエッジと立ち下がりエッジの両方にすることができます。ハードウェア・インターフェイスを使用して構成した場合、STEP アクティブ・エッジは立ち上がりエッジのみになります。高い入力 STEP レートで実行する必要のあるアプリケーションでは、両方のエッジをアクティブ・エッジとして構成すると、入力 STEP レートは実質的に 2 倍になるため、コントローラのオーバーヘッドが半分に減少します。

|

インターフェイス |

STEP_EDGE |

STEP アクティブ・エッジ |

|---|---|---|

|

SPI |

0b (デフォルト) |

立ち上がりエッジ |

|

1b |

立ち上がりエッジと立ち下がりエッジ |

|

|

H/W |

X |

立ち上がりエッジ |

STEP 入力の各アクティブ・エッジのタイミングで、インデクサは表の次の状態に進みます。この方向は、DIR ピンがロジック High の場合です。DIR ピンがロジック Low の場合、表のシーケンスは反転します。ステップ中にステップ・モードが動的に変更された場合、STEP のアクティブ・エッジで、インデクサは次の有効な状態に進み、新しいステップ・モード設定になります。

電源投入後、ロジック低電圧誤動作防止が終了した後、またはスリープ・モードを終了した後で、インデクサは初期励起状態 (ホーム位置) である 45° の電気角に移動します。これは、両方のコイルのフルスケール電流の 71% に対応します。このような場合、すべてのレジスタが各デフォルト値に復元されます。

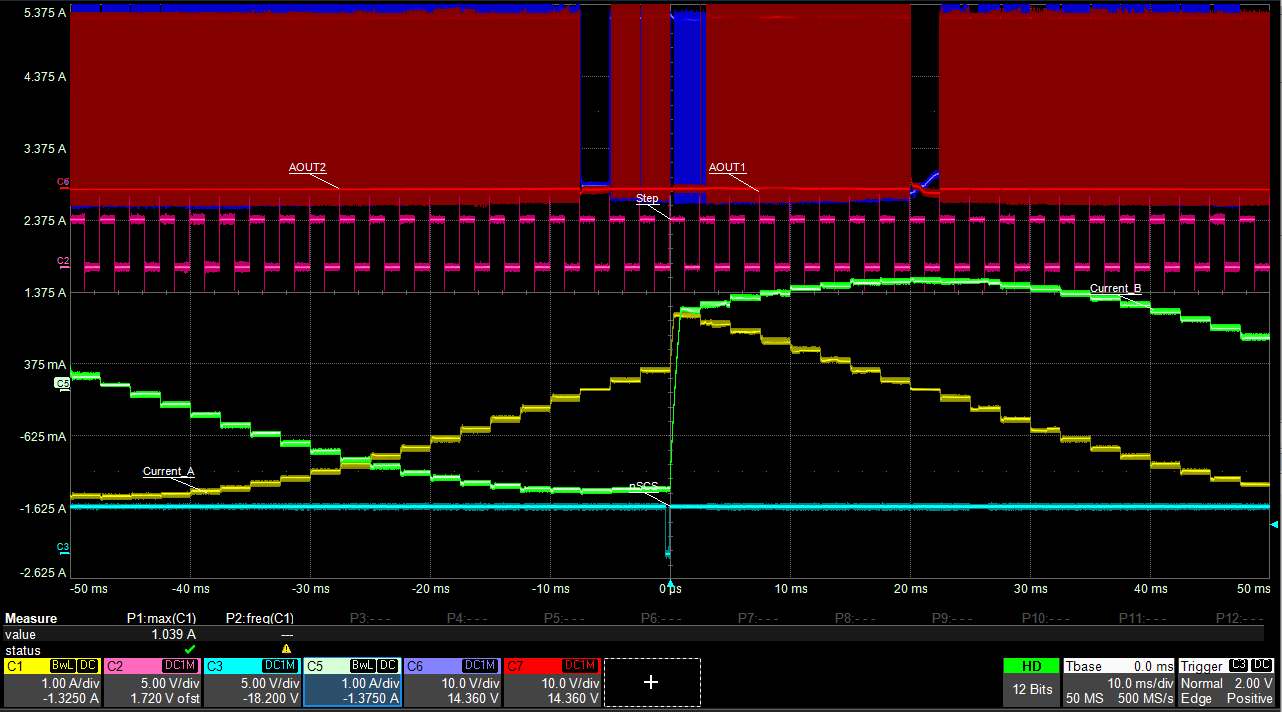

SPI インターフェイスで動作しているとき、IDX_RST ビットが 1b の場合、図 7-5 に示すようにインデクサは 45° の電気角にリセットされますが、メモリ・マップ・レジスタの内容は変更されません。

図 7-5 インデクサのリセット. 上から下へのパターン:AOUT2、AOUT1、STEP、コイル B 電流、コイル A 電流、nSCS

図 7-5 インデクサのリセット. 上から下へのパターン:AOUT2、AOUT1、STEP、コイル B 電流、コイル A 電流、nSCSSTEP 入力周波数がジッタすると、ストール検出の目的でデバイスの信号はフィルタリングされます。表 7-11 に示すように、FRQ_CHG ビットと STEP_FRQ_TOL ビットでフィルタ設定をプログラムします。2% のフィルタリングは、中心周波数付近で最大 2% のジッタがフィルタリングされ、内部回路がモーターのストールを検出するためのクリーンな STEP 信号を生成することを意味します。

|

FRQ_CHG |

STEP_FRQ_TOL |

フィルタリング |

|---|---|---|

|

0b (デフォルト) |

00b |

1% |

|

01b (デフォルト) |

2% |

|

|

10b |

4% |

|

|

11b |

6% |

|

|

1b |

X |

フィルタリングなし |