JAJSBA6N January 2000 – March 2024 LMC555

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 ピン構成および機能

- 5 仕様

- 6 パラメータ測定情報

- 7 詳細説明

- 8 アプリケーションと実装

- 9 デバイスおよびドキュメントのサポート

- 10改訂履歴

- 11メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

発注情報

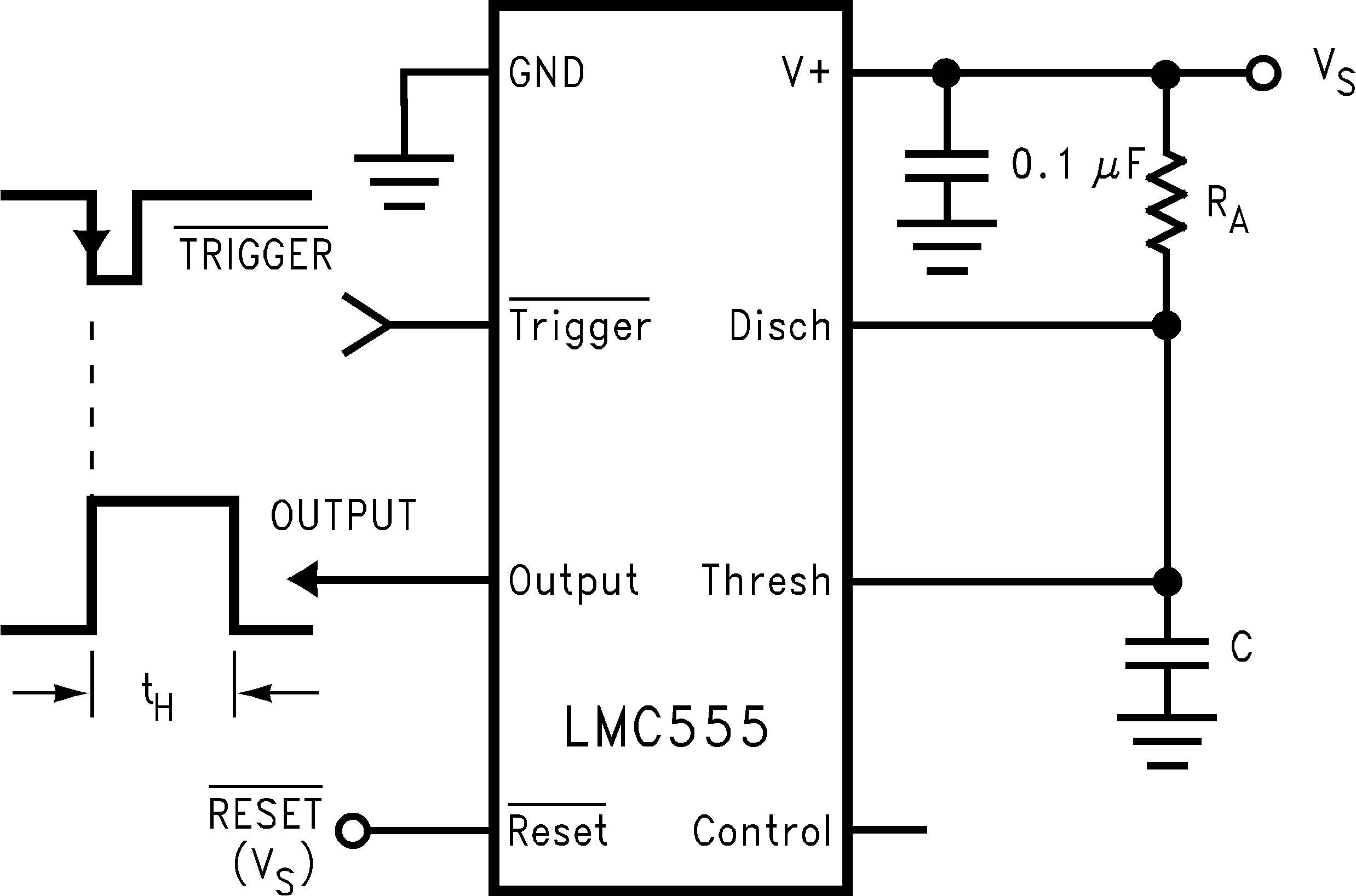

7.4.1 単安定動作

この動作モードでは、タイマはワンショットとして機能します (図 7-2)。外付けコンデンサは、最初は内部回路によって放電された状態に保持されます。1/3 VS より低い負のトリガ パルスをTRIGGER ピンに印加すると、フリップフロップがセットされ、コンデンサの短絡が解放され、出力が HIGH に駆動されます。

図 7-2 単安定 (ワンショット)

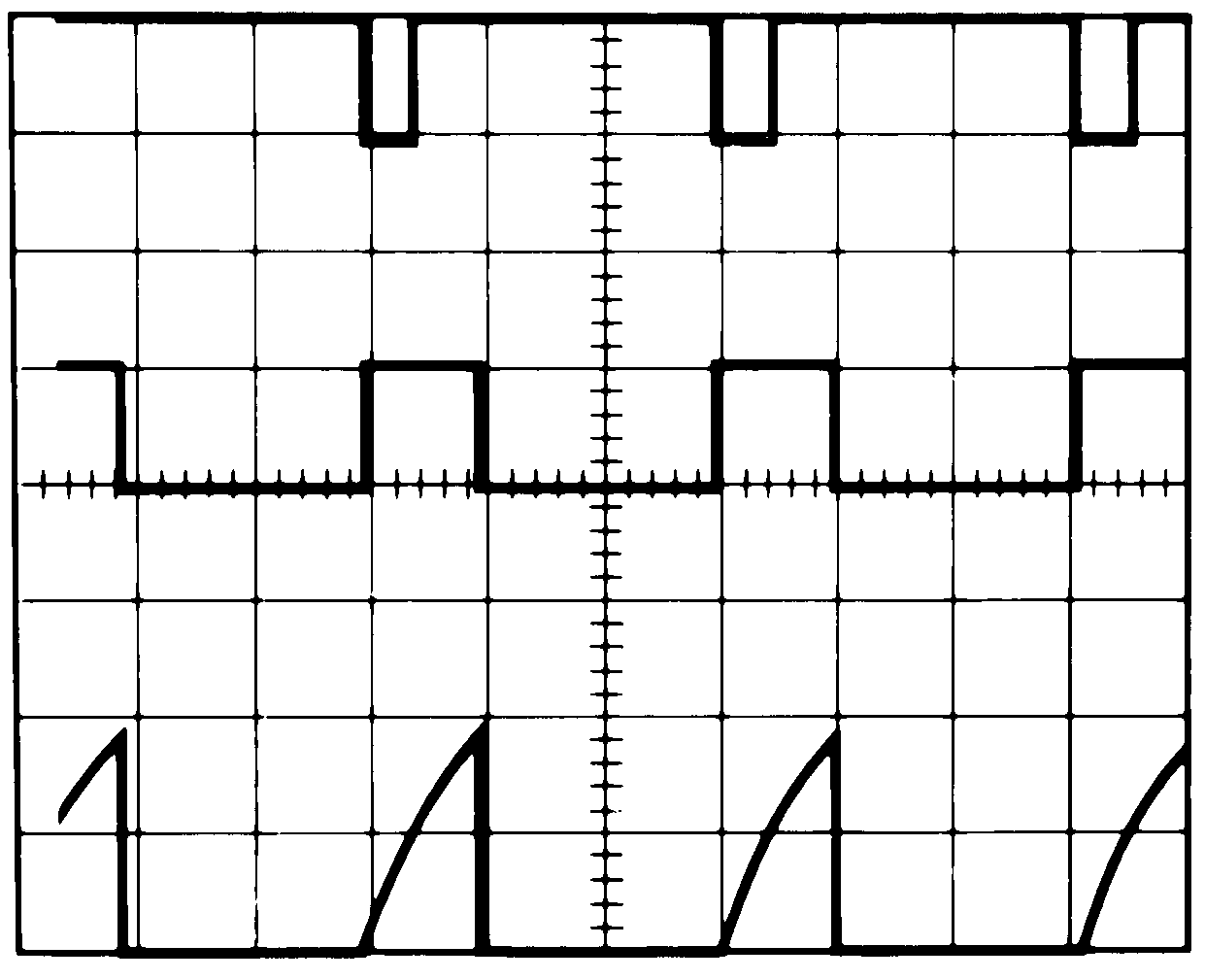

図 7-2 単安定 (ワンショット)このとき、コンデンサの両端の電圧は、tH = 1.1 RAC の間、指数関数的に増加します。この期間は出力が HIGH に維持される時間でもあり、この期間の終了時には電圧は 2/3 VS に等しくなります。その後、コンパレータはフリップ フロップをリセットします。これによりコンデンサが放電され、出力が LOW 状態に駆動されます。 この動作モードで生成される波形を 図 7-3 に示します。コンパレータの充電レベルとスレッショルドレベルはどちらも電源電圧に正比例するため、内部タイミングは電源に依存しません。

| VS = 5 V | 上のトレース:入力 5V/div | RA = 9.1 kΩ |

| 時間 = 0.1ms/div | 中央のトレース:出力 5V/div | C = 0.01µF |

| 下のトレース:コンデンサ電圧 2V/div |

RESET は、TRIGGER をオーバーライドします。トリガは、THRESHOLD をオーバーライドできます。したがって、トリガ パルスは、目的の tH よりも短くなるようにしてください。TRIGGER の最小パルス幅は 20ns、RESETの最小パルス幅は 400ns です 。出力が HIGH のタイミング サイクル中に、さらにトリガ パルスを印加しても、タイミング期間終了の少なくとも 10µs 前にトリガ入力が HIGH に復帰していれば、回路に影響しません。ただし、この期間中に RESET ピンに負のパルスを印加すると、回路をリセットできます 。トリガ パルスが再度印加されるまで、出力は LOW 状態のままです。

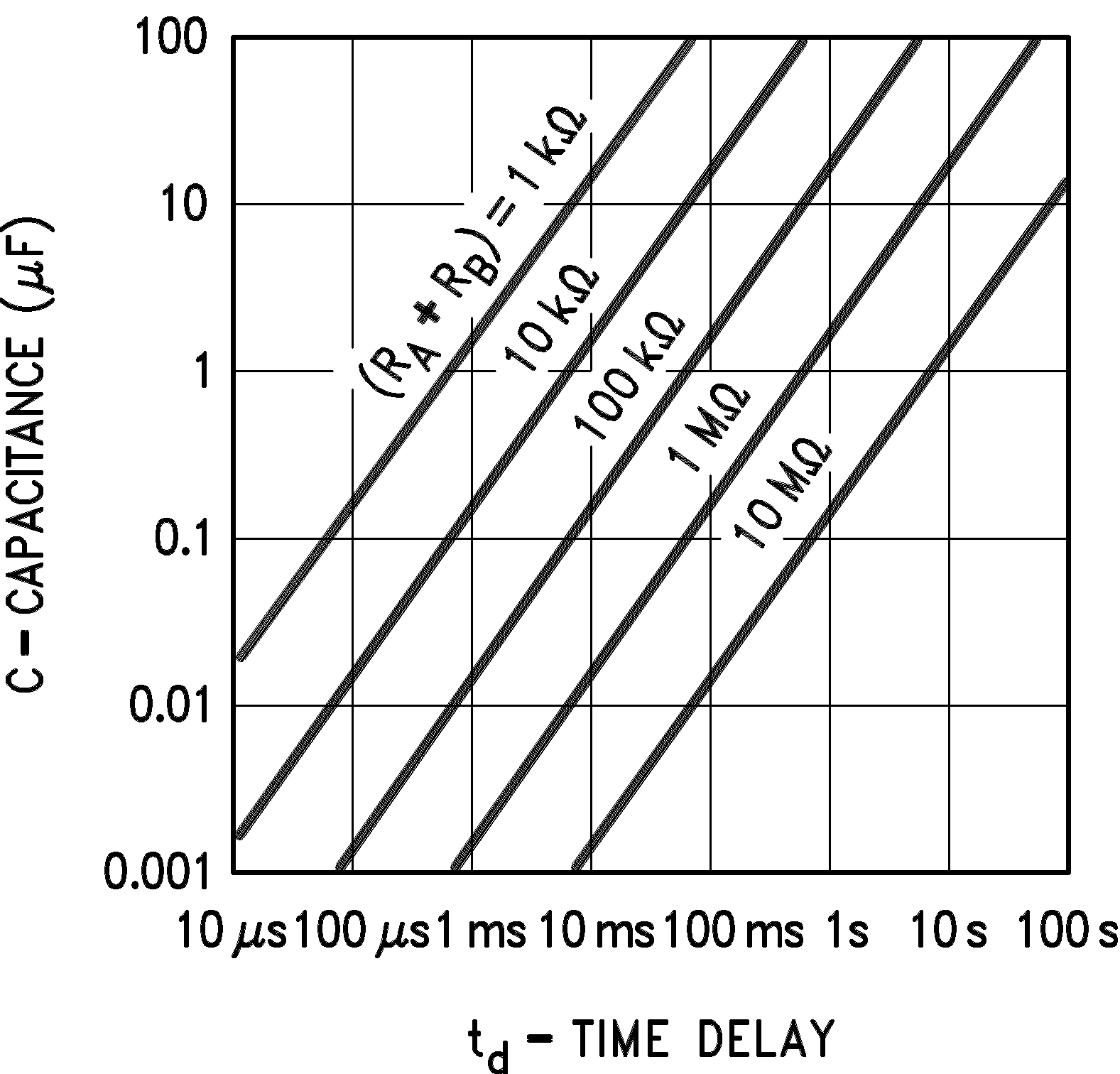

リセット機能を使用しないときは、誤トリガの可能性を避けるため、RESET ピンを V+ に接続します。図 7-4 は、さまざまな時間遅延に対する RC 値を簡単に決定するための計算図表です。

単安定動作では、タイミング サイクルが終了する前にトリガを HIGH に駆動します。

図 7-4 時間遅延

図 7-4 時間遅延