JAJSLW3B October 2021 – May 2022 SN74LXC2T45

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 ピン構成と機能

- 6 仕様

- 7 パラメータ測定情報

- 8 詳細説明

- 9 部分的パワーダウン (Ioff)

- 10VCC の絶縁および VCC の接続解除 (Ioff-float)

- 11過電圧許容入力

- 12グリッチの発生しない電源シーケンシング

- 13負のクランプ・ダイオード

- 14フル構成可能なデュアル・レール設計

- 15高速変換をサポート

- 16デバイスの機能モード

- 17アプリケーションと実装

- 18電源に関する推奨事項

- 19レイアウト

- 20デバイスおよびドキュメントのサポート

- 21メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

発注情報

3 概要

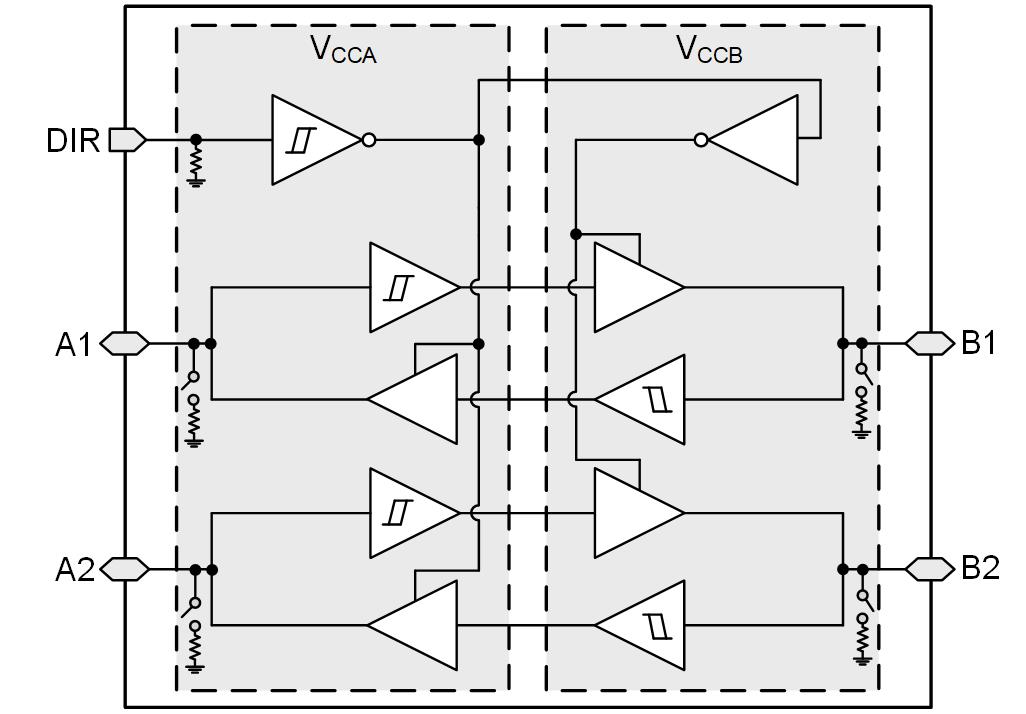

SN74LXC2T45 は、デュアル・ビット、デュアル電源、非反転双方向電圧レベル変換デバイスです。Ax ピンおよび制御ピン (DIR) は VCCA ロジック・レベルを基準とし、Bx ピンは VCCB ロジック・レベルを基準としています。A ポートは 1.1V~5.5V の範囲の I/O 電圧を受け入れ、B ポートは 1.1V~5.5V の I/O 電圧を受け入れます。DIR が HIGH のときは A から B へ、DIR が LOW のときは B から A へデータが転送されます。制御ロジックの概要についてはデバイス機能モードを参照してください。

製品情報(1)

| 部品番号 | パッケージ | 本体サイズ (公称) |

|---|---|---|

| SN74LXC2T45 | SM8 (DCT) (8)(2) | 2.95mm × 2.80mm |

| VSSOP (DCU) (8) | 2.30mm × 2.00mm | |

| SON (DTT) (8) | 1.95mm × 1.00mm | |

| X2SON (DTM) (8) | 1.35mm × 0.80mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

(2) プレビュー版パッケージです。

機能ブロック図

機能ブロック図