JAJSKD3 november 2020 TAS6424MS-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Device Options

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3

Feature Description

- 9.3.1 Serial Audio Port

- 9.3.2 High-Pass Filter

- 9.3.3 Volume Control and Gain

- 9.3.4 High-Frequency Pulse-Width Modulator (PWM)

- 9.3.5 Channel-to-Channel Phase Control

- 9.3.6 Gate Drive

- 9.3.7 Power FETs

- 9.3.8 Load Diagnostics

- 9.3.9

Protection and Monitoring

- 9.3.9.1 Overcurrent Limit (ILIMIT)

- 9.3.9.2 Overcurrent Shutdown (ISD)

- 9.3.9.3 DC Detect

- 9.3.9.4 Clip Detect

- 9.3.9.5 Global Overtemperature Warning (OTW), Overtemperature Shutdown (OTSD)

- 9.3.9.6 Channel Overtemperature Warning [OTW(i)] and Shutdown [OTSD(i)]

- 9.3.9.7 Undervoltage (UV) and Power-On-Reset (POR)

- 9.3.9.8 Overvoltage (OV) and Load Dump

- 9.3.10 Power Supply

- 9.3.11 Hardware Control Pins

- 9.4 Device Functional Modes

- 9.5 Programming

- 9.6

Register Maps

- 9.6.1 Mode Control Register (address = 0x00) [default = 0x00]

- 9.6.2 Miscellaneous Control 1 Register (address = 0x01) [default = 0x32]

- 9.6.3 Miscellaneous Control 2 Register (address = 0x02) [default = 0x62]

- 9.6.4 SAP Control (Serial Audio-Port Control) Register (address = 0x03) [default = 0x04]

- 9.6.5 Channel State Control Register (address = 0x04) [default = 0x55]

- 9.6.6 Channel 1 Through 4 Volume Control Registers (address = 0x05–0x08) [default = 0xCF]

- 9.6.7 DC Load Diagnostic Control 1 Register (address = 0x09) [default = 0x00]

- 9.6.8 DC Load Diagnostic Control 2 Register (address = 0x0A) [default = 0x11]

- 9.6.9 DC Load Diagnostic Control 3 Register (address = 0x0B) [default = 0x11]

- 9.6.10 DC Load Diagnostic Report 1 Register (address = 0x0C) [default = 0x00]

- 9.6.11 DC Load Diagnostic Report 2 Register (address = 0x0D) [default = 0x00]

- 9.6.12 DC Load Diagnostics Report 3 Line Output Register (address = 0x0E) [default = 0x00]

- 9.6.13 Channel State Reporting Register (address = 0x0F) [default = 0x55]

- 9.6.14 Channel Faults (Overcurrent, DC Detection) Register (address = 0x10) [default = 0x00]

- 9.6.15 Global Faults 1 Register (address = 0x11) [default = 0x00]

- 9.6.16 Global Faults 2 Register (address = 0x12) [default = 0x00]

- 9.6.17 Warnings Register (address = 0x13) [default = 0x20]

- 9.6.18 Pin Control Register (address = 0x14) [default = 0x00]

- 9.6.19 AC Load Diagnostic Control 1 Register (address = 0x15) [default = 0x00]

- 9.6.20 AC Load Diagnostic Control 2 Register (address = 0x16) [default = 0x00]

- 9.6.21 AC Load Diagnostic Impedance Report Ch1 through Ch4 Registers (address = 0x17–0x1A) [default = 0x00]

- 9.6.22 AC Load Diagnostic Phase Report High Register (address = 0x1B) [default = 0x00]

- 9.6.23 AC Load Diagnostic Phase Report Low Register (address = 0x1C) [default = 0x00]

- 9.6.24 AC Load Diagnostic STI Report High Register (address = 0x1D) [default = 0x00]

- 9.6.25 AC Load Diagnostic STI Report Low Register (address = 0x1E) [default = 0x00]

- 9.6.26 Miscellaneous Control 3 Register (address = 0x21) [default = 0x00]

- 9.6.27 Clip Control Register (address = 0x22) [default = 0x01]

- 9.6.28 Clip Window Register (address = 0x23) [default = 0x14]

- 9.6.29 Clip Warning Register (address = 0x24) [default = 0x00]

- 9.6.30 ILIMIT Status Register (address = 0x25) [default = 0x00]

- 9.6.31 Miscellaneous Control 4 Register (address = 0x26) [default = 0x40]

- 10Application Information Disclaimer

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- DKQ|56

サーマルパッド・メカニカル・データ

- DKQ|56

発注情報

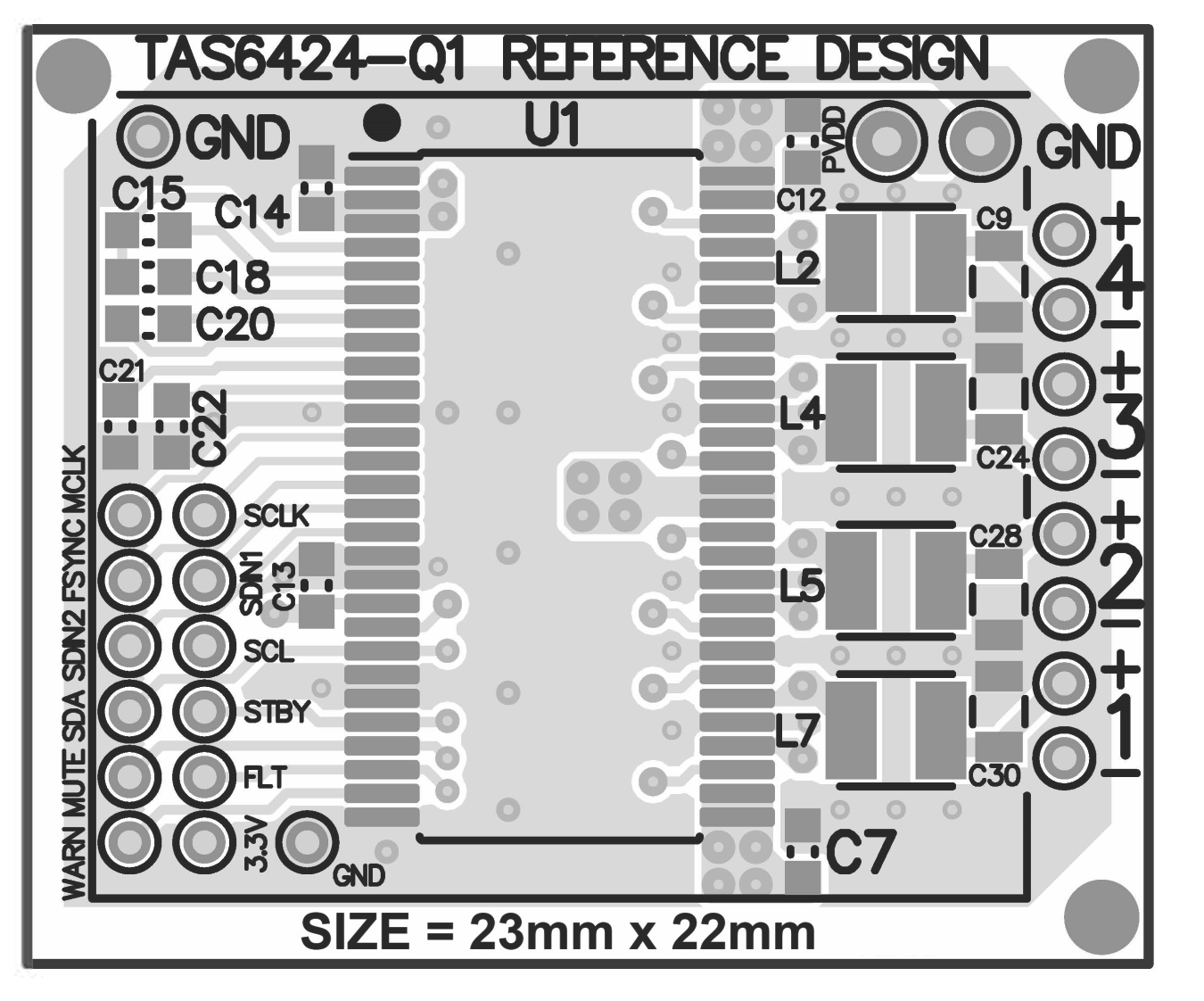

3 概要

TAS6424MS-Q1 デバイスは 4 チャネルのデジタル入力 Class-D オーディオ・アンプで、2.1MHz の PWM スイッチング周波数を実装しているため、非常に小さなサイズの PCB でコスト最適化されたソリューションを実現可能です。開始 / 停止イベントについて最低 4.5V で完全な動作を行い、最高 40kHz のオーディオ帯域幅で非常に優れた音質を提供します。

出力スイッチング周波数は、AM ラジオ帯域より高く設定することも、低く設定することもできます。AM 帯域よりも高く設定すると、AM 帯域への干渉をなくすと同時に、出力フィルタを小さくしてコストを低減できます。AM 帯域よりも低く設定すると、効率を最適化できます。

デバイスには負荷診断機能が組み込まれており、出力の誤接続や、AC 結合されたツイータを検出して診断できるため、製造プロセスにおいてテスト時間を短縮するために役立ちます。

TAS6424MS-Q1 Class-D オーディオ・アンプは、車載用ヘッド・ユニット、および外部アンプ・モジュールで使用するよう設計されています。1、2、4 チャネルのピン互換デバイスについては、「デバイスのオプション」の表を参照してください。

製品情報

| 部品番号 | パッケージ(1) | 本体サイズ (公称) |

|---|---|---|

| TAS6424MS-Q1 | HSSOP (56) | 18.41mm × 7.49mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

PCB 領域

PCB 領域