JAJST56D October 2001 – February 2024 TFP410

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Pin Configuration and Functions

- 5 Specifications

-

6 Detailed Description

- 6.1 Overview

- 6.2 Functional Block Diagram

- 6.3 Feature Description

- 6.4 Device Functional Modes

- 6.5 Programming

- 6.6

Register Maps

- 6.6.1 VEN_ID Register (Sub-Address = 01−00 ) [reset = 0x014C]

- 6.6.2 DEV_ID Register (Sub-Address = 03–02) [reset = 0x0410]

- 6.6.3 REV_ID Register (Sub-Address = 04) [reset = 0x00]

- 6.6.4 Reserved Register (Sub-Address = 07–05) [reset = 0x641400]

- 6.6.5 CTL_1_MODE (Sub-Address = 08) [reset = 0xBE]

- 6.6.6 CTL_2_MODE Register (Sub-Address = 09) [reset = 0x00]

- 6.6.7 CTL_3_MODE Register (Sub-Address = 0A) [reset = 0x80]

- 6.6.8 CFG Register (Sub-Address = 0B)

- 6.6.9 RESERVED Register (Sub-Address = 0E–0C) [reset = 0x97D0A9]

- 6.6.10 DE_DLY Register (Sub-Address = 32) [reset = 0x00]

- 6.6.11 DE_CTL Register (Sub-Address = 33) [reset = 0x00]

- 6.6.12 DE_TOP Register (Sub-Address = 34) [reset = 0x00]

- 6.6.13 DE_CNT Register (Sub-Address = 37–36) [reset = 0x0000]

- 6.6.14 DE_LIN Register (Sub-Address = 39–38) [reset = 0x0000]

- 6.6.15 H_RES Register (Sub-Address = 3B−3A)

- 6.6.16 V_RES Register (Sub-Address = 3D−3C)

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- PAP|64

サーマルパッド・メカニカル・データ

- PAP|64

発注情報

3 概要

TFP410 デバイスは、テキサス・インスツルメンツ の PanelBus™ フラットパネル ディスプレイ製品であり、エンド ツー エンド DVI 1.0 準拠ソリューションの包括的なファミリの一部です。PC およびコンシューマ エレクトロニクス業界を対象にしています。

TFP410 デバイスにはユニバーサル インターフェイスが搭載されており、最も一般的に入手可能なグラフィックス コントローラと直接接続できます。このユニバーサル インターフェイスは、選択可能なバス幅、調節可能な信号レベル、差動/シングルエンド クロックを特長としています。1.1V~1.8V 可変のデジタル インターフェイスにより、低 EMI の高速バスを実現し、12 ビットまたは 24 ビットのインターフェイスとシームレスに接続できます。DVI インターフェイスは、24 ビット True Color ピクセル フォーマットで、165MHz、UXGA までのフラットパネル ディスプレイ解像度をサポートしています。

TFP410 デバイスは、革新的な PanelBus 回路と、TI の先進的な 0.18μm EPIC-5 CMOS プロセス テクノロジー、および TI の超低グランドインダクタンス PowerPAD パッケージを組み合わせたものです。その結果、小型の 64 ピン TQFP パッケージで、信頼性、低消費電流、低ノイズの高速デジタル インターフェイス ソリューションを実現しました。

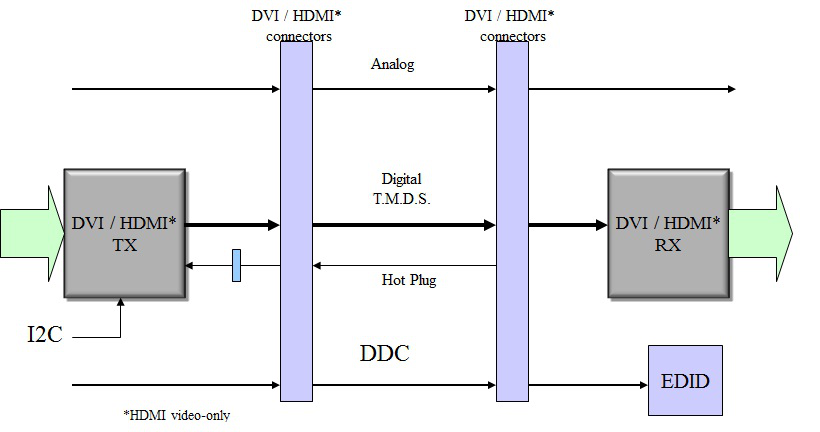

代表的な HDMI インターフェイス

代表的な HDMI インターフェイス