JAJSKM1C october 2019 – september 2021 UCC5870-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Power Supplies

- 7.3.2 Driver Stage

- 7.3.3 Integrated ADC for Front-End Analog (FEA) Signal Processing

- 7.3.4 Fault and Warning Classification

- 7.3.5

Diagnostic Features

- 7.3.5.1 Undervoltage Lockout (UVLO) and Overvoltage Lockout (OVLO)

- 7.3.5.2 CLAMP, OUTH, and OUTL Clamping Circuits

- 7.3.5.3 Active Miller Clamp

- 7.3.5.4 DESAT based Short Circuit Protection (DESAT)

- 7.3.5.5 Shunt Resistor based Overcurrent Protection (OCP) and Short Circuit Protection (SCP)

- 7.3.5.6 Temperature Monitoring and Protection for the Power Transistors

- 7.3.5.7 Active High Voltage Clamping (VCECLP)

- 7.3.5.8 Two-Level Turn-Off

- 7.3.5.9 Soft Turn-Off (STO)

- 7.3.5.10 Thermal Shutdown (TSD) and Temperature Warning (TWN) of Driver IC

- 7.3.5.11 Active Short Circuit Support (ASC)

- 7.3.5.12 Shoot-Through Protection (STP)

- 7.3.5.13 Gate Voltage Monitoring and Status Feedback

- 7.3.5.14 VGTH Monitor

- 7.3.5.15 Cyclic Redundancy Check (CRC)

- 7.3.5.16 Configuration Data CRC

- 7.3.5.17 SPI Transfer Write/Read CRC

- 7.3.5.18 TRIM CRC Check

- 7.4 Device Functional Modes

- 7.5 Programming

- 7.6 Register Maps

- 8 Applications and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

8.2.2.4 VCECLP Input

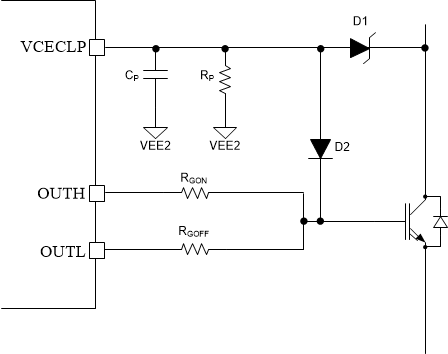

The active VCE clamp circuit is used to reduce VCE overshoot voltage during IGBT turn off. The external circuit (Figure 8-3) uses four components: A high-voltage TVS diode (D1) that turns on (avalanche breakdown) if the VCE overshoot during the IGBT turn-off is greater than the TVS diode avalanche limit, a filter capacitor (CP) that is charged when D1 conducts, a diode (D2) that conducts some of the avalanche current to the IGBT gate to increase the gate voltage (VGE) in order slow down the turn off transient and reduce the VCE overshoot, and a resistor (RC) to set the time constant to discharge the VCECLP node when D1 stops conducting. Select the D1 avalanche voltage rating to be the IGBT VCE overshoot voltage control target. During normal operation, the VCE dV/dt couples to VCECLP through junction capacitance of D1. The CP value is selected to filter this coupled ripple voltage to prevent triggering the VCE clamp function during normal operation. When a VCE over voltage occurs and D1 avalanches, CP charges to the VCECLPth by avalanche current, then VCE clamp function triggers and OUTL driver is disabled while the STO current is enabled. The RP value sets the the RC time constant when the CP voltage drops below VCECLPth. The value of RP depends on the selection of the IGBT, D1, RGON, RGOFF. Typically, the Rp value is between 10 to 100 ohm and CP value is between 10nF to 100nF. There is not a hard and fast calculation for these components. The best method is experimenting to fine tune the components for best performance in the application. See Figure 8-4 for an example of performance with the UCC5870QDWJEVM-026 (https://www.ti.com/tool/UCC5870QDWJEVM-026) EVM.

Figure 8-3 VCECLP External Components

Figure 8-3 VCECLP External Components