JAJSLN2 November 2021 TPS7H1210-SEP

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

3 概要

TPS7H1210-SEP 負電圧リニア・レギュレータは、1A の最大負荷を供給できる低ノイズ、高 PSRR のレギュレータです。

このレギュレータには、CMOS ロジックレベル互換のイネーブル・ピン (EN) が搭載されており、ユーザーがカスタマイズ可能なパワー・マネージメント方式を実現できます。その他の機能として、電流制限機能とサーマル・シャットダウン機能が内蔵されており、障害状態時にデバイスとシステムが保護されます。

TPS7H1210-SEP デバイスは、システム性能を最大限に高めるためにクリーンな電源レールが決定的に重要な、高精度、低ノイズのアプリケーションを主な対象として、バイポーラ・テクノロジで設計されています。したがって、オペアンプ、ADC、DAC、その他の高性能アナログ回路への電力供給に理想的です。

そのほか、TPS7H1210-SEP デバイスは、DC/DC コンバータのポスト・レギュレーションに適しています。DC/DC スイッチング変換に本質的に付随する出力電圧リップルをフィルタ処理し、影響を受けやすいデバイスや RF アプリケーションにおいて、最大のシステム性能が保証されます。

デバイス情報

| 部品番号 (1) | グレード | パッケージ (2) |

|---|---|---|

| TPS7H1210MRGWSEP | 20krad(Si) RLAT、30krad(Si) 特性 | VQFN (20) 5.00mm × 5.00mm 質量 = 83.6mg |

| TPS7H1210EVM | 評価ボード | EVM |

(1) 利用可能なパッケージについては、このデータシートの末尾にある注文情報を参照してください。

(2) 寸法と質量は公称値です。

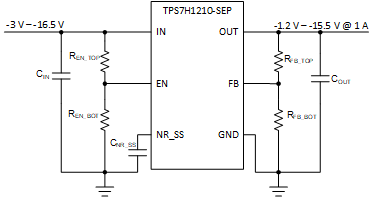

代表的なアプリケーション回路図

代表的なアプリケーション回路図