JAJU751G September 2019 – October 2023

- 1

- 概要

- リソース

- 特長

- アプリケーション

- 6

- 1システムの説明

-

2システム概要

- 2.1 ブロック図

- 2.2 設計上の考慮事項

- 2.3

主な使用製品

- 2.3.1 LMG3422R050 — ドライバと保護機能を内蔵した 600V GaN

- 2.3.2 TMCS1100 — 高精度絶縁型電流センス・モニタ

- 2.3.3 UCC27524 — デュアル、5A、高速 2 次側パワー MOSFET ドライバ

- 2.3.4 UCC27714 — 620V、1.8A、2.8A 1 次側 / 2 次側ゲート・ドライバ

- 2.3.5 ISO7721 — 高速、堅牢な EMC 特性、強化絶縁型、基本デュアル・チャネル・デジタル・アイソレータ

- 2.3.6 ISO7740 および ISO7720 — 高速、低消費電力、堅牢な EMC デジタル・アイソレータ

- 2.3.7 OPA237 — 単一電源オペアンプ

- 2.3.8 INAx180 — 2 次側および 1 次側電圧出力、電流センス・アンプ

- 2.3.9 TPS560430 — SIMPLE SWITCHER 4V~36V、600mA、同期整流降圧コンバータ

- 2.3.10 TLV713 — ポータブル機器向けフォールドバック電流制限付き 150mA 低ドロップアウト (LDO) レギュレータ

- 2.3.11 TMP61 — 温度検出向けシリコン・ベース小型リニア・サーミスタ

- 2.3.12 CSD18510Q5B — 40V、N チャネル NexFET MOSFET、シングル SON5x6、0.96mΩ

- 2.3.13 UCC28911 — 定電圧、定電流、1 次側レギュレーション付き 700V フライバック・スイッチャ

- 2.3.14 SN74LVC1G3157DRYR — 単極双投アナログ・スイッチ

- 2.4 システム設計理論

-

3ハードウェア、ソフトウェア、テスト要件、テスト結果

- 3.1

必要なハードウェアとソフトウェア

- 3.1.1 ハードウェア

- 3.1.2 PFC 段ソフトウェア

- 3.1.3 LLC 段ソフトウェア

- 3.1.4 PFC + LLC 段のデュアル・テスト

- 3.1.5 ライブ・ファームウェア・アップデートの概要

- 3.2 テストと結果

- 3.1

必要なハードウェアとソフトウェア

- 4設計ファイル

- 5ソフトウェア・ファイル

- 6関連資料

- 7著者について

- 8改訂履歴

- 132

3.1.5.5 CLA で制御ループを実行した状態での LFU デモの実行とテスト結果

デバイスの両方のフラッシュ・バンクにカスタム・ブートローダとアプリケーション・イメージがプログラムされた状態で、LFU デモはスタンドアロン・モードで実行できるようになりました。

スイッチオーバーが成功したことは、デバイス上のさまざまな信号、レジスタ、LED で確認できます。

ボードに電源を供給します。この時点で、LED2 (GPIO34 – D2) が消灯し、LED1 (GPIO31 – D1) が点灯していることを確認してください。これは、Bank0 アプリケーションが実行中のアクティブなアプリケーションであることを示しています。両方の LED (D1 と D2) が点灯している場合、Bank1 がアクティブなアプリケーションです。PWM ゲート駆動信号がオシロスコープに表示されていないことを確認してください。これは、ソフトウェアが Microsoft® Windows® PC からの SCI オートボー・ロック・コマンドを待機しているためです。

SCI オートボー・ロックを有効にするには、Microsoft Windows のコマンド・プロンプトからコマンドを実行します。このコマンドは、以前にブートローダとアプリケーションをプログラムする際に入力したコマンドと似ています。コマンドの例は以下のとおりです。

serial_flash_programmer_appln.exe -d f28003x -k f28003x_fw_upgrade_example\flash_kernel_ex3_sci_flash_kernel_bank0.txt -a f28003x_fw_upgrade_example\llc_f28003x_BANK1FLASH.txt -b 9600 -p COM5

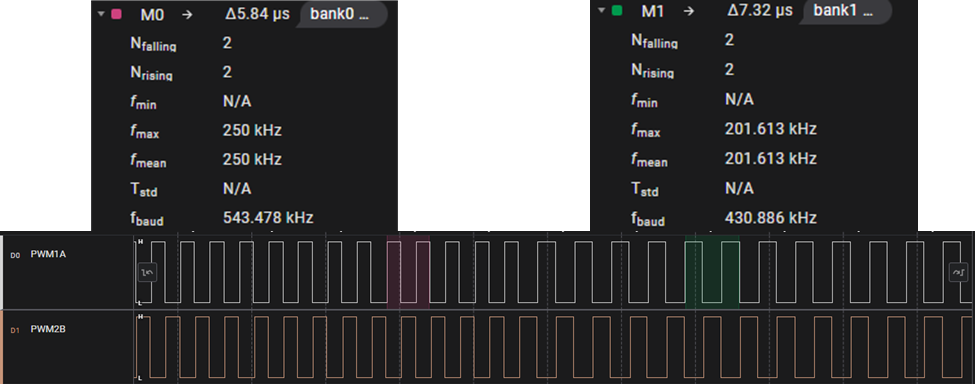

図 3-38 LFU 操作前と後のスイッチング周波数の変化

ここで、controlCARD の LED1 が点滅していることを確認します。これによって、LLC_main.c のバックグラウンド・タスク B1 で LLC_HAL_toggleLED () 関数が実行されていることが確認できます。LED2 は、BANK0 にアクティブなアプリケーションがある場合は消灯し、BANK1 にアクティブなアプリケーションがある場合は点灯します。

コマンド・プロンプト・ウィンドウには、前に示したのと同じフラッシュ・プログラミング・オプションが表示されます。これで、デバイスはもう一方のフラッシュ・バンクに切り替えることができます。もう一方のバンクに実行を切り替えるには、「8 – Live DFU」と入力します。これによって、新しいファームウェアが非アクティブなバンクにプログラムされます。完了したら、「0 – Done」と入力してプロセスを完了します。フラッシュへのダウンロード中は、バックグラウンド・タスクが停止されるために LED1 の点滅は停止します。

デバイスに新しいイメージがプログラムされると、LED2 と LED1 が点灯から消灯 (Bank1 -> Bank0)、または消灯から点灯 (Bank0 -> Bank1) に切り替わります。これによって、新しいイメージが実行されていることが分かります。

PWM 信号の波形が新しい目標スイッチング周波数 (200kHz) に更新され、緑色 (M1) で示されます。図 3-38 を参照してください。

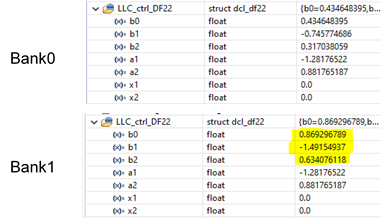

もう一つの確認方法は、DF22 コントローラの新しい係数をプログラムすることです。LFU の前に Bank0 アプリケーションのシンボルを CCS にロードし、LLC_ctrl_DF22 構造体の内容を観れば確認できます。具体的には、対象となる制御ループ・パラメータ b0、b1、b2 を観察してください。LFU が完了したら、Bank1 アプリケーションのシンボルを CCS にロードすることができ、対象となるパラメータを観察して、新しいイメージのスイッチオーバーと実行、適切な設定を確認できます。図 3-39 に、LFU の前後の係数値を示します。

図 3-39 Bank0 と Bank1 の異なるイメージ間での制御ループ・パラメータの変化