JAJU878 November 2022 ADS117L11 , ADS127L11 , ADS127L14 , ADS127L18

- 概要

- リソース

- 特長

- アプリケーション

- 5

- 1System Description

- 2System Overview

- 3System Design Theory

- 4Hardware, Software, Testing, and Test Results

- 5Design and Documentation Support

- 6About the Author

4.1.2.5.2 Parallel SDO Mode

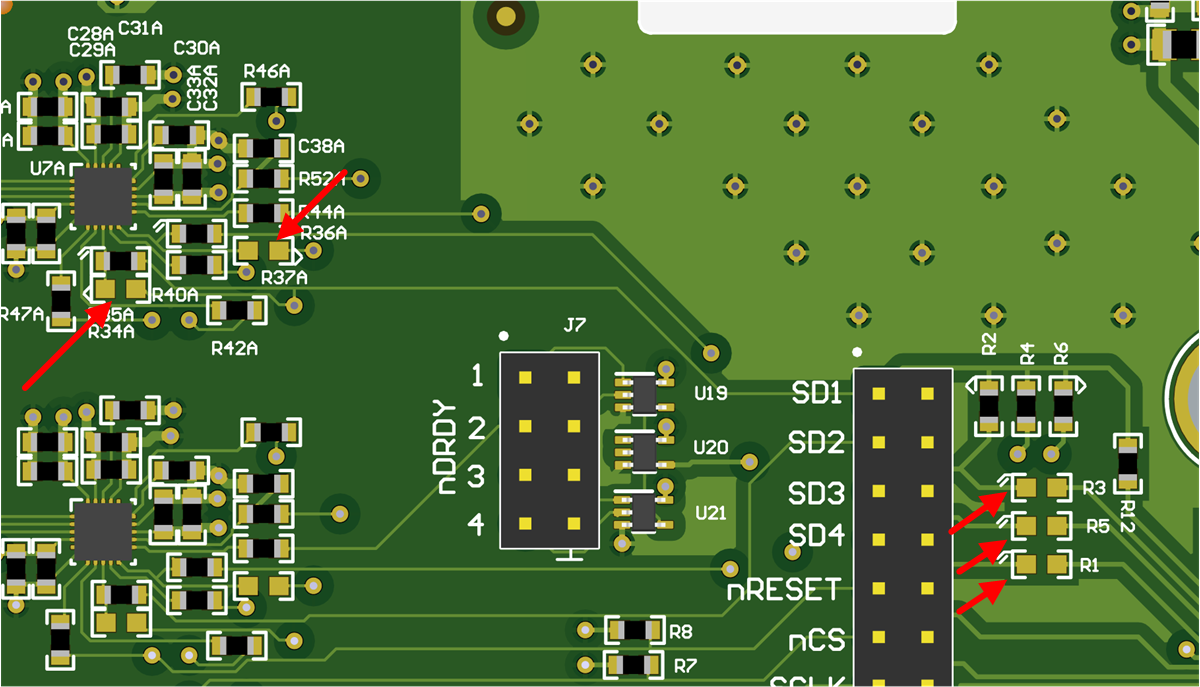

In parallel SDO mode, the four ADCs are connected in parallel, with a single shared SDI input, and four parallel SDO outputs as Figure 4-4 shows.

This mode reduces the signal lines required by the controller when high speed is needed but the ADC configuration is similar. The SPI clock can reach 25 MHz allowing data rates at 1 MSPS per channel.

The following board assembly is required to enable the parallel SDO mode:

- R35x, R37x (all channels), remove R3, R5, and R1

Note: Figure 4-4 shows that R35x and R37x are indicated by a small triangle to indicate that the

resistors are only used in daisy-chain.

Figure 4-4 Parallel SDO Variant

Figure 4-4 Parallel SDO Variant