JAJU878 November 2022 ADS117L11 , ADS127L11 , ADS127L14 , ADS127L18

- 概要

- リソース

- 特長

- アプリケーション

- 5

- 1System Description

- 2System Overview

- 3System Design Theory

- 4Hardware, Software, Testing, and Test Results

- 5Design and Documentation Support

- 6About the Author

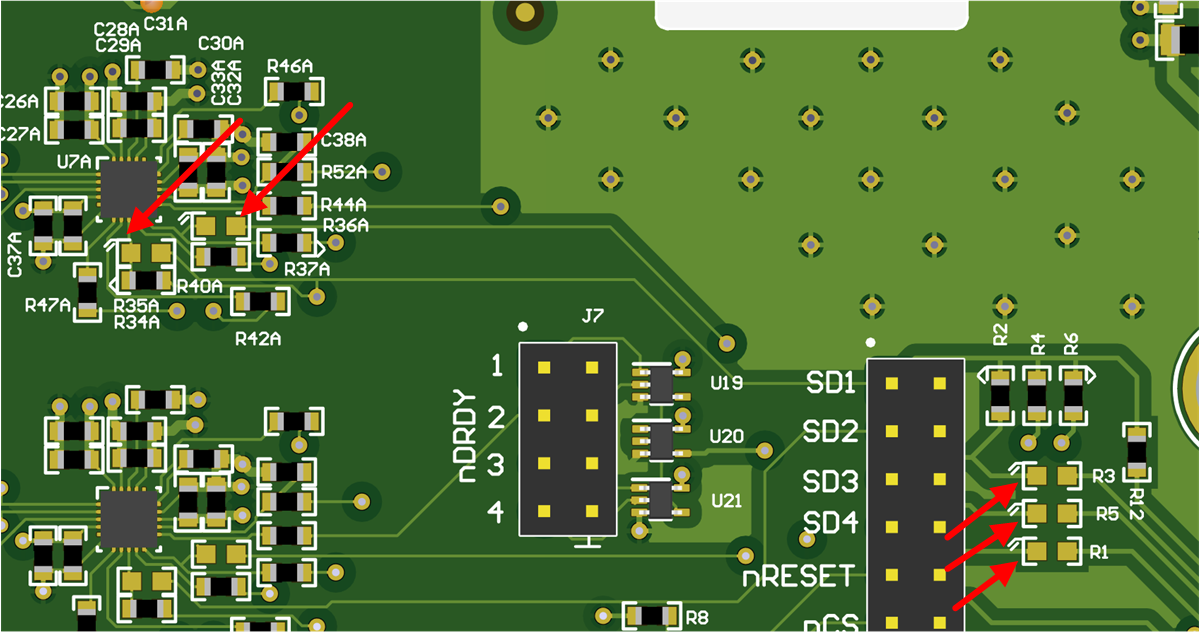

4.1.2.5.1 Daisy-Chain Mode

In this mode, the four ADCs are connected in a daisy-chain fashion Figure 4-3 shows. The maximum SPI clock rate in this mode is 16 MHz.

The following board assembly is required to enable the daisy-chain mode:

- R40x, R36x (all channels), remove R3, R5, and R1

Note: Figure 4-3 shows that all of those resistors are indicated by small parallel lines on the

top left corner of the resistor.

Figure 4-3 Daisy-Chain Variant

Figure 4-3 Daisy-Chain Variant