JAJU878 November 2022 ADS117L11 , ADS127L11 , ADS127L14 , ADS127L18

- 概要

- リソース

- 特長

- アプリケーション

- 5

- 1System Description

- 2System Overview

- 3System Design Theory

- 4Hardware, Software, Testing, and Test Results

- 5Design and Documentation Support

- 6About the Author

4.4.7 Fault Detection Circuit

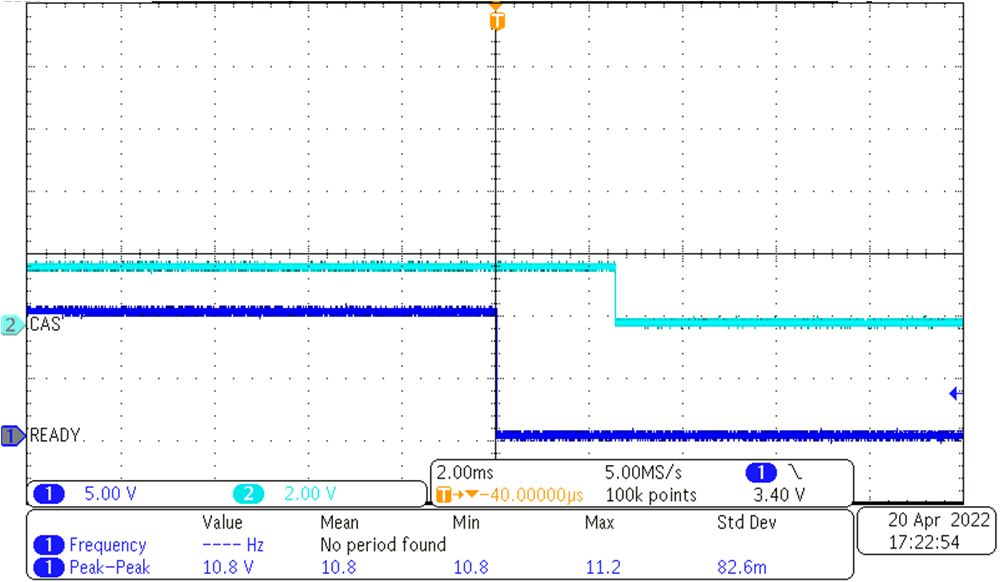

Sweeping the input voltage results in the following thresholds for a fault-detection circuit:

- 0.5 V is the short detection threshold

- 20.1 V is the open detection threshold

The input signal stepped down from 10 V to 0 V, and the output of the short detection comparator is probed. The plot in Figure 4-19 shows a delay of 1.5 ms until the comparator output goes low.

Figure 4-19 Time-Domain Plot of Fault

Detection Circuit Delay

Figure 4-19 Time-Domain Plot of Fault

Detection Circuit Delay