JAJU878 November 2022 ADS117L11 , ADS127L11 , ADS127L14 , ADS127L18

- 概要

- リソース

- 特長

- アプリケーション

- 5

- 1System Description

- 2System Overview

- 3System Design Theory

- 4Hardware, Software, Testing, and Test Results

- 5Design and Documentation Support

- 6About the Author

4.1.2.5.4 Clocking Modes

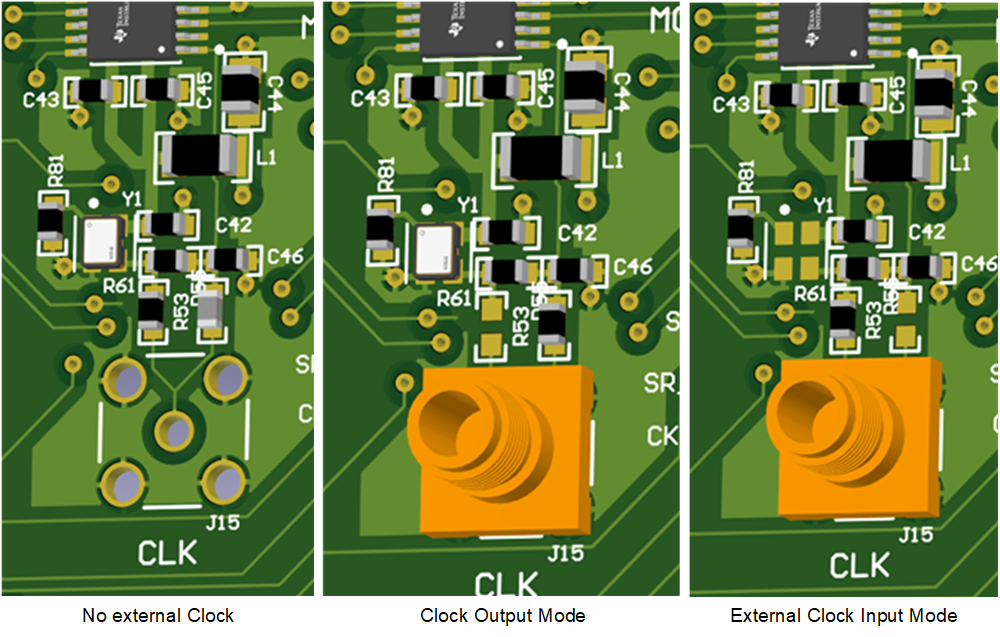

The board supports 3 clocking modes as illustrated in Figure 4-6:

- Stand-alone mode: there is no clock line connection to other boards

- Clock output mode: the onboard clock is connected to the SMA connector

- External clock input mode: there is no onboard clock, the external clock is connected to the SMA connector

Table 4-2 details the board configuration with a minor assembly variant in the clocking section.

Table 4-2 Board Clocking

Configurations

| NO EXTERNAL CLOCK CONNECTIVITY | CLOCK OUTPUT MODE | EXTERNAL CLOCK INPUT MODE |

|---|---|---|

| J15 removed | R53 removed | Y1 removed, R55 removed |

Figure 4-6 Clocking Assembly

Variants

Figure 4-6 Clocking Assembly

VariantsIf synchronizing two boards, configure the first board in clock output mode, and configure the second board in external clock input mode. A short coaxial cable connects J15 on both boards, and both boards can be connected to the same controller. Use the controller to handle the difference in nRDY signal.