SBAA461 December 2020 ADC3541 , ADC3542 , ADC3543 , ADC3544 , ADC3641 , ADC3642 , ADC3643 , ADC3644 , ADC3660 , ADC3681 , ADC3682 , ADC3683

3 Reduce Data Rates: Decimation

There many benefits to using the on-chip decimation of the ADC36xx family for both the analog and digital functions of the ADC, and the overall system requirements of the application.

When we decimate, we effectively reduce the data rate by a preset decimation factor (from 2 to 32). For example, if we choose to decimate by a factor of 8, we reduce our effective sampling rate by 8, which reduces the output data rate by 8 as well. A lower data rate can allow for a lower cost data capture device (FPGA or micro controller).

Also, every time we decimate by a factor of 2, we are also improving our SNR by ~3 dBFS. Furthermore, using decimation has the added benefit of relaxing anti-aliasing filtering requirements since harmonics (like HD2 and HD3) will be attenuated by the digital low pass decimation filters.

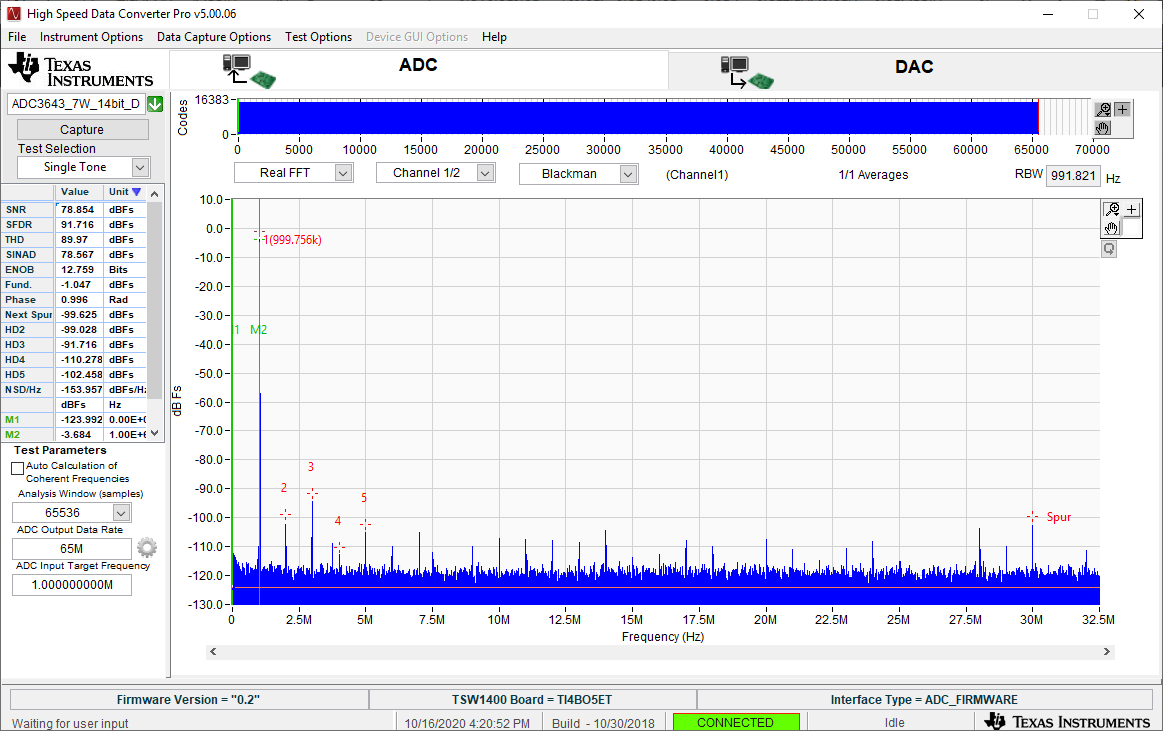

In the figure below, DDR mode is used to show ADC performance at 65 MSPS since the serial CMOS modes have max sample rate of ~35 MSPS while using bypass mode (2Wire). In bypass mode (no decimation) sampling at 65 MSPS with a 1 MHz input, we see about 79 dBFS SNR and 91 SFDR.

Figure 3-1 ADC3643EVM: 1MHz Fin @ 65 MSPS (No

Decimation)

Figure 3-1 ADC3643EVM: 1MHz Fin @ 65 MSPS (No

Decimation)| Serial Interface | Sampling Rate (MSPS) | Serialization Rate | Decimation Factor | Data Rate (Mbps) |

|---|---|---|---|---|

| 2 Wire | 35.7 | 7 | 1 | 227.5 |

| SNR (-dBFS) | SFDR (-dBFS) | THD (-dBFS) | HD2 (-dBFS) | HD3 (-dBFS) |

|---|---|---|---|---|

| 78.8 | 91.7 | 89.9 | 99 | 91 |

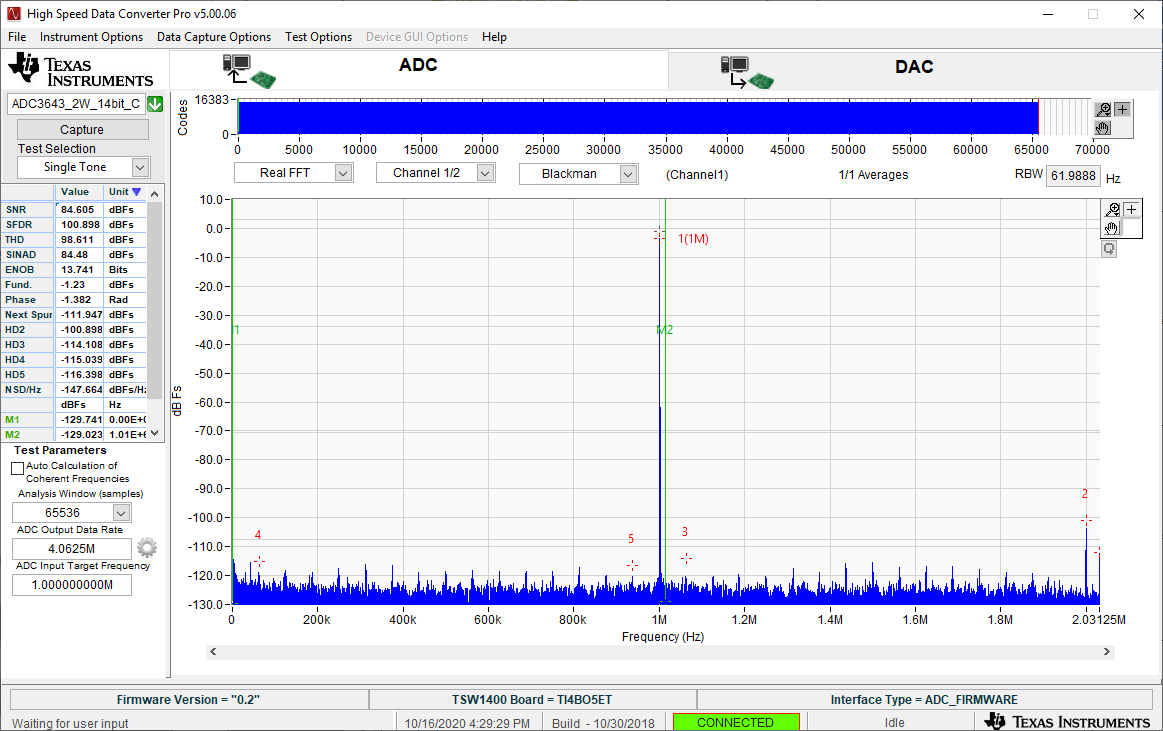

If we then apply 16x Real Decimation to the same configuration, we see some interesting things happen. First, SNR and SFDR have increased, and the Nyquist zone (sampling rate divided by 2, or Fs/2) has now become much smaller (32.5 MHz to 2.03125 MHz).

Figure 3-2 ADC3643EVM: 1MHz Fin @ 65 MSPS

(16x Real Decimation).

Figure 3-2 ADC3643EVM: 1MHz Fin @ 65 MSPS

(16x Real Decimation). | Serial Interface | Sampling Rate (MSPS) | Serialization Rate | Decimation Factor | Data Rate (Mbps) |

|---|---|---|---|---|

| 2 Wire | 65 | 7 | 16 | 28.4375 |

| SNR (-dBFS) | SFDR (-dBFS) | THD (-dBFS) | HD2 (-dBFS) | HD3 (-dBFS) |

|---|---|---|---|---|

| 84.6 | 100.8 | 98.6 | 100.9 | 114 |

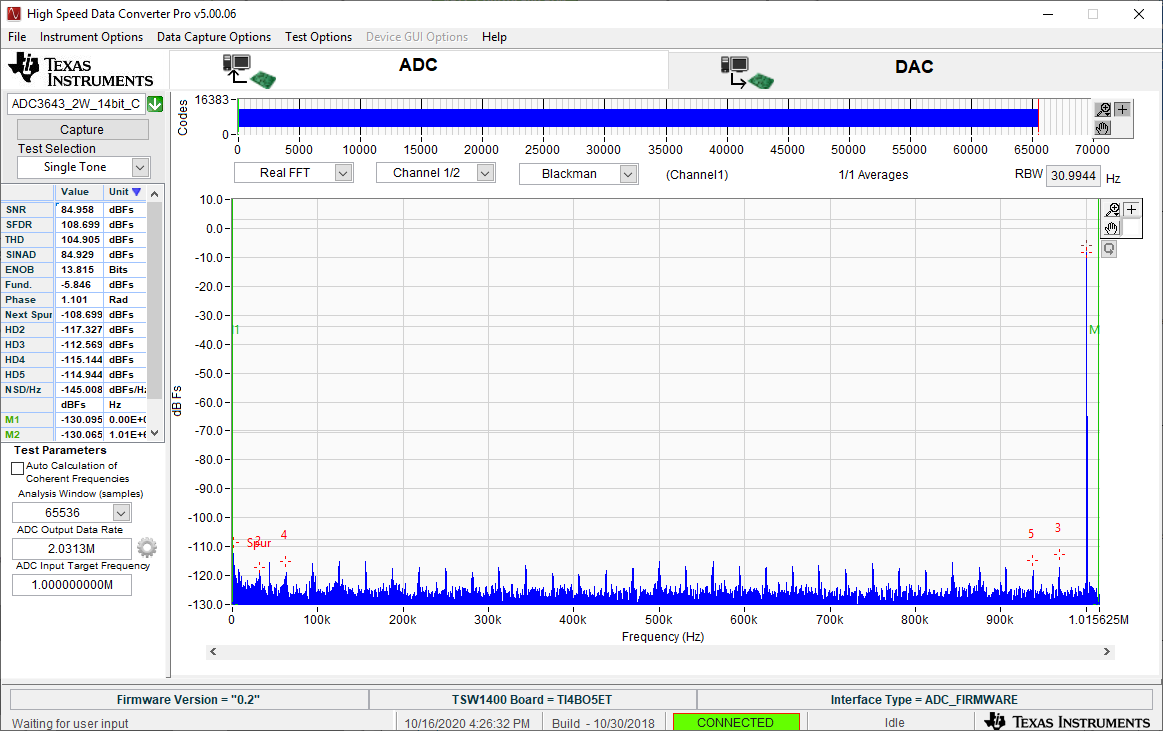

Taking a step further, applying 32x Real Decimation reduces our data rate even further to 14.21875 Mbps. In terms of AC performance, SNR doesn't improve much since we are reaching the limits of what can be represented by a 14 bit ADC (SNR: 1.76 + 6.02*14= 86 dB), but the SFDR improves from -100 to -108 dBFS since HD2 is now pushed out of the Nyquist zone, into the stop band of our low pass decimation filter.

Figure 3-3 ADC3643EVM: 1MHz Fin at 65 MSPS

(32x Real Decimation)

Figure 3-3 ADC3643EVM: 1MHz Fin at 65 MSPS

(32x Real Decimation)| Serial Interface | Sampling Rate (MSPS) | Serialization Rate | Decimation Factor | Data Rate (Mbps) |

|---|---|---|---|---|

| 2 Wire | 65 | 7 | 32 | 14.21875 |

| SNR (-dBFS) | SFDR (-dBFS) | THD (-dBFS) | HD2 (-dBFS) | HD3 (-dBFS) |

|---|---|---|---|---|

| ~85 | 108.6 | 104.9 | 117.3 | 112.5 |

If we also consider the different serial modes that were discussed earlier, our sampling rates were limited by the max output data rate (~250 Mbps). Looking at the table below, it can be seen that the max sampling rate of 65 MSPS can be used when decimation is applied, and very low data rates can be achieved.

| Serial Interface | Sampling Rate (MSPS) | Serialization Rate | Decimation Factor | Data Rate (Mbps) |

|---|---|---|---|---|

| 2 Wire | 65 | 7 | 32 | 14.21875 |

| 1 Wire | 65 | 14 | 32 | 28.4375 |

| 1/2 Wire | 65 | 28 | 32 | 56.875 |

Decimation brings along two great advantages: data rate reduction and AC performance improvement (SNR, THD, SFDR, and so on,). While decimation can be carried out in the DSP or FPGA, the ADC3643 provides this feature on-chip and removes the need for complex DSP implementation, allowing the ADC do the work for you.