SBAA528 February 2022 ADC12QJ1600-Q1 , TPS62912 , TPS62913

1.1.1 ADC12QJ1600-Q1 Noise and Ripple Requirements

The ADC12QJ1600-Q1 is a family of quad, dual and single channel, 12bit, 1.6 GSPS analog-to-digital converter (ADC). Low power consumption and high sample rate make the ADC12QJ1600-Q1 an ideal suite for light detection and ranging (LiDAR) systems. The ADC12QJ1600-Q1 uses a high-speed JESD204C output interface with up to 8 serialized lanes supporting up to 17.16 Gbps line rate. Deterministic latency and multi-device synchronization is supported through JESD204C subclass-1 and is compatible with JESD204B receivers. Innovative synchronization features, including SYSREF windowing, internal PLL with internal voltage-controlled oscillator (VCO), multi clock outputs for logic and Serdes of FPGA or ASIC, simplify system design for multi-device applications.

The original product evaluation module (EVM) implements low-noise LDOs in addition to the DC/DC buck regulators to minimize any impairments from the supply network. While the DC accuracy of the supply rail is specified for the ADC12QJ1600-Q1, there is no specification on supply voltage noise and supply voltage ripple. Any supply ripple or noise appears attenuated on the output spectrum of the ADC. This attenuation can be expressed as Power Supply Rejection Ration (PSRR) and PSRRMOD (or PSMR) as shown in Figure 1-1.

Figure 1-1 Power Supply Noise and Ripple

in the ADC Output Spectrum

Figure 1-1 Power Supply Noise and Ripple

in the ADC Output SpectrumPSRR is the attenuation of the ADC input supply ripple to the ADC output spectrum at the switching frequency fundamental of the DC-DC converter (fDCDC). PSRRMOD (or PSMR) is the attenuation from the ADC input to the modulated spur in the output spectrum (fin - fDCDC, fin + fDCDC).

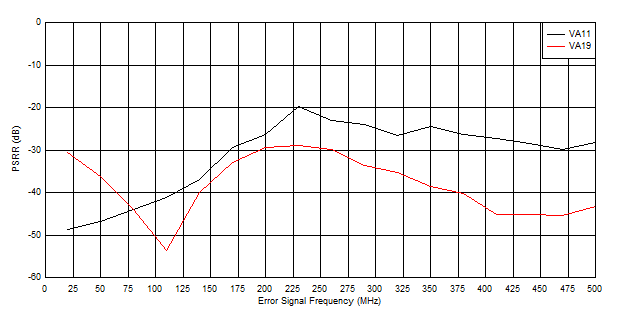

PSRR is usually less of a concern since it is typically >40 dB and outside of the frequency of interest, however some analog rails can have PSRR of <40 dB, as shown in Figure 1-2. Most sensitive supplies of the ADC12QJ1600-Q1 are the analog supply rails of VA11 and VA19. More important is PSMR, since the attenuation from the supply rail to the modulated spur can be low for sensitive analog rails such as VA11 and VA19 on the ADC12QJ1600-Q1.

Figure 1-2 ADC12QJ1600-Q1 PSRR of the

VA11 and VA19 Supplies

Figure 1-2 ADC12QJ1600-Q1 PSRR of the

VA11 and VA19 Supplies