SLAAEF9 November 2023 MSPM0L1306

- 1

- Abstract

- Trademarks

- 1MSPM0 Portfolio Overview

-

2Ecosystem And Migration

- 2.1 Ecosystem Comparison

- 2.2 Migration Process

- 2.3 Example

- 3Core Architecture Comparison

- 4Digital Peripheral Comparison

- 5Analog Peripheral Comparison

3.6.3 Event Link Controller (ELC) of RL78

Some RL78 MCUs have an event link controller (ELC) that mutually connects (links) events output from each peripheral function. By linking events, RL78 MCUs can coordinate operation between peripheral functions directly without going through the CPU.

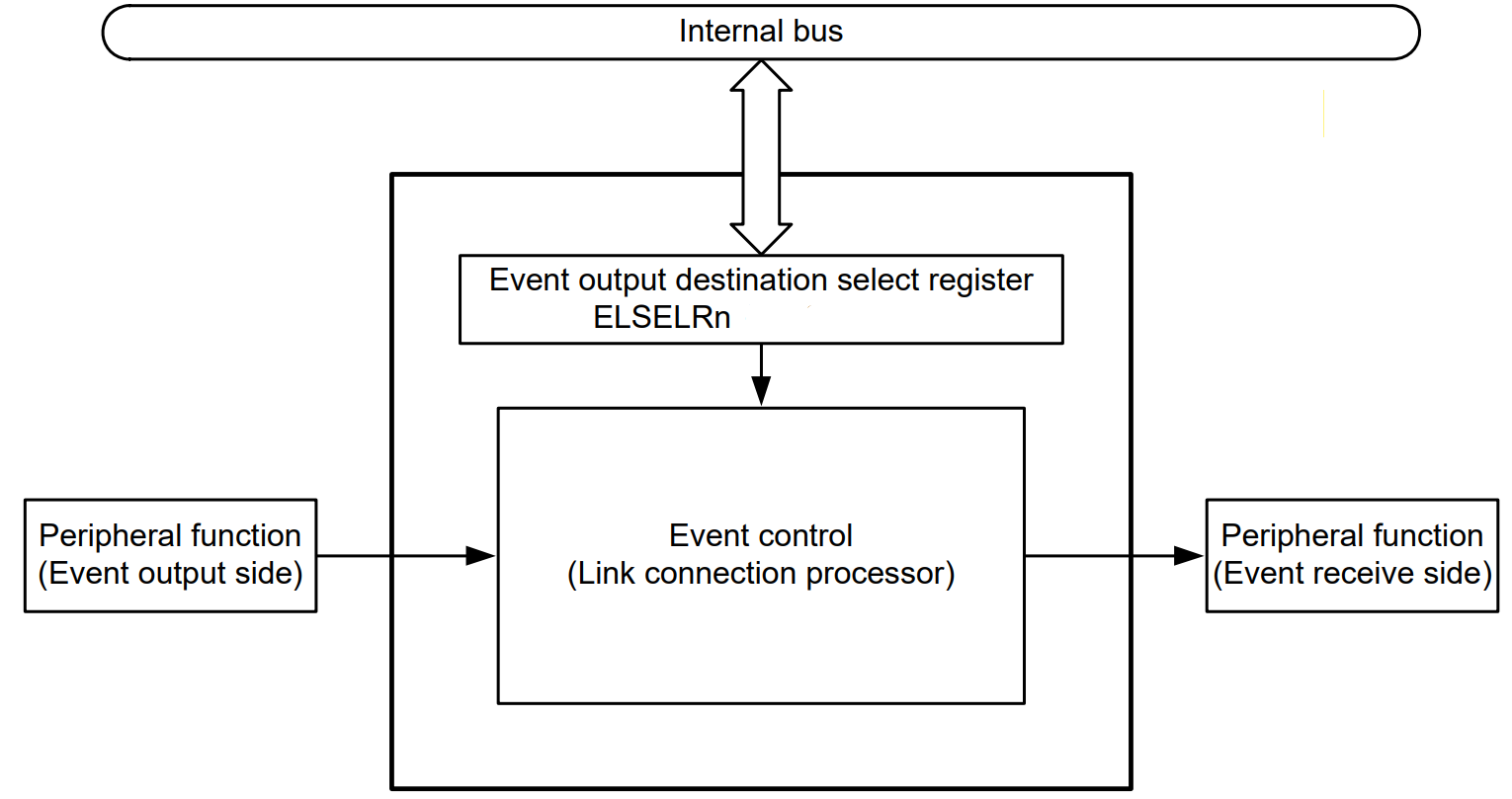

Figure 3-7 shows the ELC block diagram. The ELSELRn register (some devices use the ELISELn and ELOSELn registers) links each event signal to an operation of an event-receiving peripheral function (link destination peripheral function) after reception. Different ELSELRn registers represent different event generator and the values set to ELSELRn registers determine the operation of link destination peripheral functions.

Figure 3-7 RL78 Event Link Controller

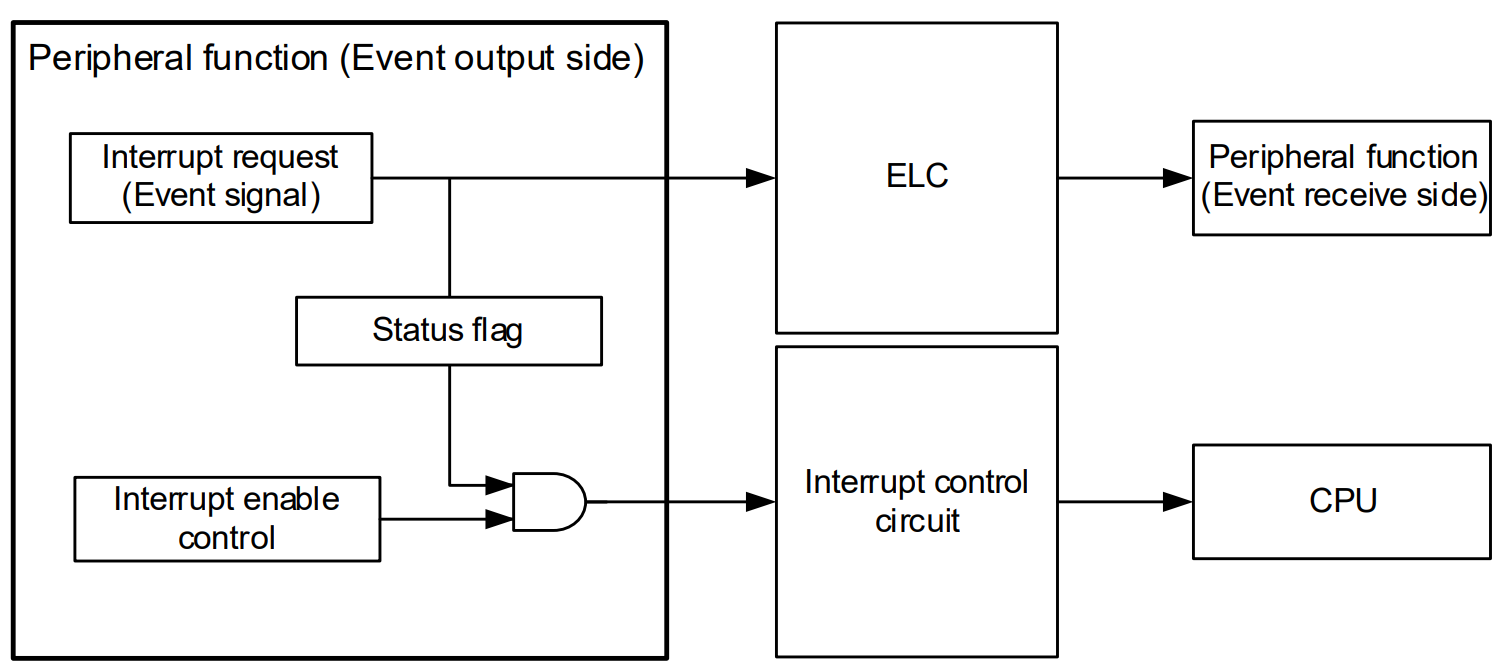

Figure 3-7 RL78 Event Link ControllerFigure 3-8 shows the relationship between interrupt handling and ELC. The path for using an event signal generated by a peripheral function as an interrupt request to the interrupt control circuit is independent from the path for using the signal as an ELC event. Therefore, each event signal can be used as an event signal for operation of an event-receiving peripheral function, regardless of interrupt control.

Figure 3-8 RL78 Event and Interrupt Handling

Figure 3-8 RL78 Event and Interrupt Handling