SNAU246A June 2020 – January 2021 LMX2820

A Using Different Reference Clock

These are the different options to provide a reference clock to LMX2820EVM.

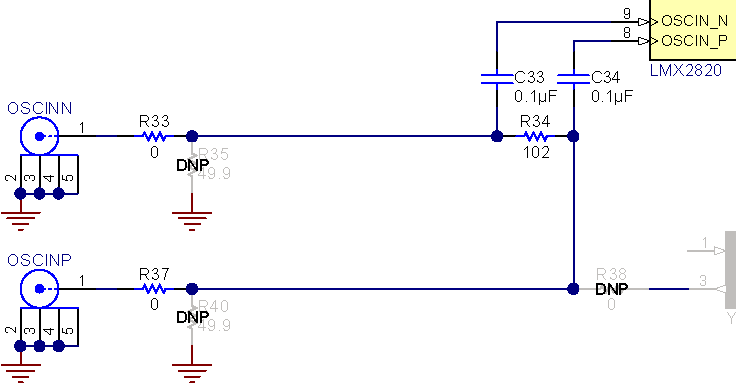

By default, the EVM is configured for an external single-ended clock.

Table A-1 Reference Clock Input

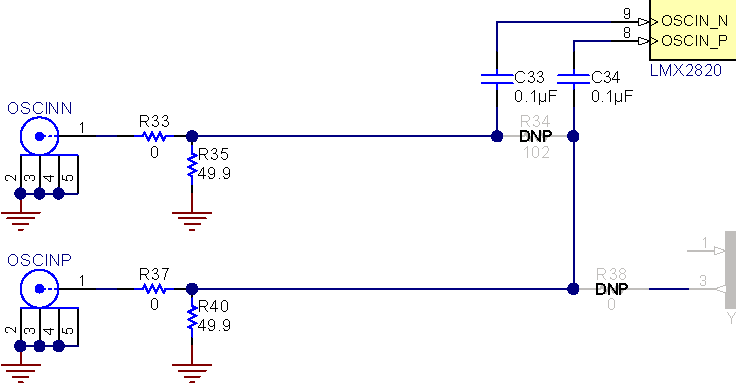

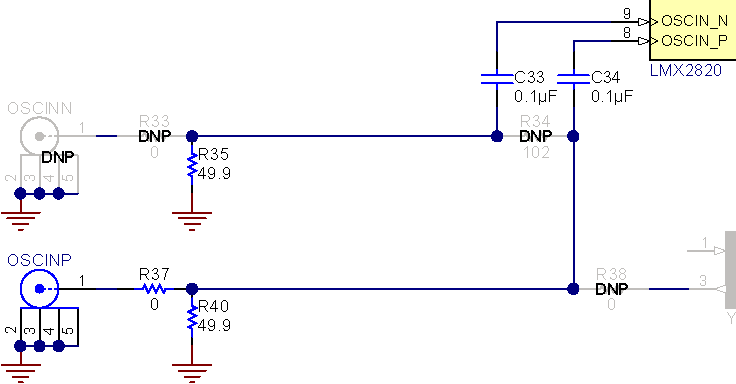

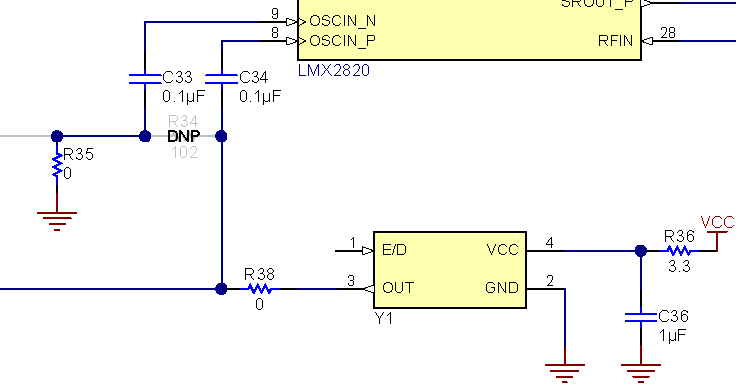

Configuration

| DIFFERENTIAL CLOCK | SINGLE-ENDED CLOCK |

|---|---|

|

|

|

|