SPRACV2 November 2020 AWR1843 , AWR2243

- Trademarks

- 1Introduction

- 2Cascade Incoherence Sources and Mitigation Strategies

-

3Enabling Cascade Coherence and Improved Phase

Performance

- 3.1 High-Level Summary

- 3.2 Saving RF INIT Calibration Results at Customer Factory

- 3.3 Corner Reflector-Based Offsets Measurement at Customer Factory

- 3.4 Restoring Customer Calibration Results In-Field

- 3.5

Host-Based Temperature Calibrations

In-Field

- 3.5.1 Disabling AWR Devices’ Autonomous Run Time Calibrations

- 3.5.2 Enabling Host-Based Temperature Calibrations of Inter-Channel Imbalances

- 3.5.3 Switching of DSP Imbalance Data

- 3.5.4

Enabling TX Phase Shifter’s Host-Based

Temperature Calibrations

- 3.5.4.1 Estimating TX Phase Shift Values at Any Temperature

- 3.5.4.2 Temperature Correction LUTs for AWR1843TX Phase Shifter

- 3.5.4.3 Temperature Correction LUTs for AWR2243 TX Phase Shifter

- 3.5.4.4 Restoring TX Phase Shift Values – Format Conversion

- 3.5.4.5 Restoring TX Phase Shift Values – Transition Timing and Constraints

- 3.5.4.6 Typical Post-Calibration TX Phase Shifter Accuracies

- 3.5.4.7 Correcting for Temperature Drift While Sweeping Across Phase Settings

- 3.5.4.8 Amplitude Stability Across Phase Shifter Settings

- 3.5.4.9 Impact of Customer PCB’s 20-GHz Sync Path Attenuation on TX Phase Shifters

- 3.5.5 Ambient and Device Temperatures

- 4Concept Illustrations

- 5Miscellaneous (Interference, Gain Variation, Sampling Jitter)

- 6Conclusion

- A Appendix

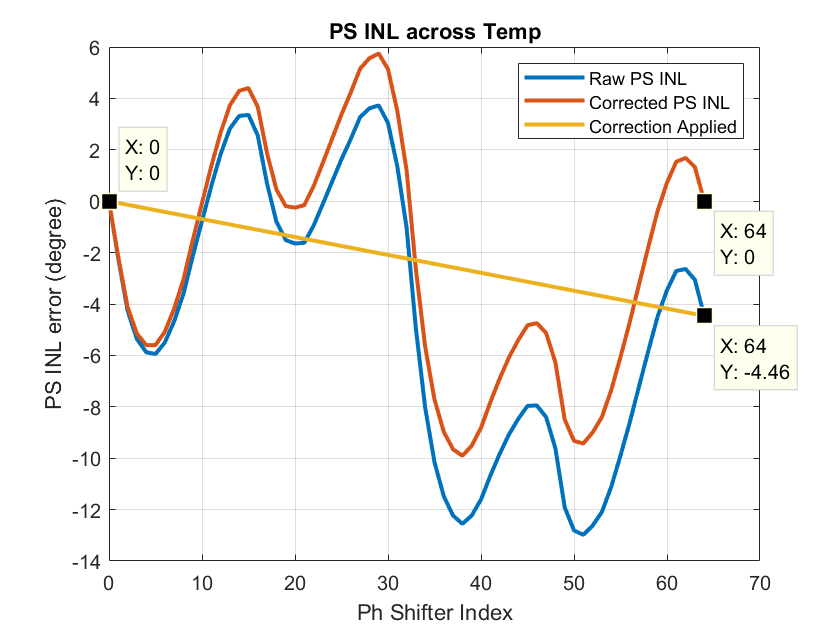

3.5.4.7 Correcting for Temperature Drift While Sweeping Across Phase Settings

This section describes a minor aspect regarding temperature drift during factory calibrations and formation of Factory Measured Phase Shift ArrayCornerReflector,TXm (0 to 63). Even if ambient temperature is stable, if there is slight drift in the device temperature while sweeping the phase shifter setting from 0 to 63 due to self-heating, it can cause a drift in PS INL measurement for the device as the experiment progresses. If there is a significant amount of drift across phase settings, then the customer can consider repeating the 0 phase shifter setting measurement at the end during the customer factory measurements, i.e. measure the phase shifter INL for the settings 0, 1, 2, 3, …., 62, 63, 0. After deriving the phase shifter INL from the measurements, the host processor can apply a linearly increasing correction as described by the following formula, so that the phase shifter INL for 0 phase setting measurement at the end becomes 0.

Here, Factory Measured Phase Array (64) refers to the measured phase shift value when 0 phase setting is repeated at the end.

This can compensate for the impact of temperature drift while sweeping the phase shifter settings. Figure 3-6 illustrates the compensation of temperature drift impact on PS INL measurements by applying a linear correction across phase settings.

Figure 3-6 Raw measured PS INL during the calibration procedure, and illustration of

linear compensation for phase changes temperature drift during calibration

measurements

Figure 3-6 Raw measured PS INL during the calibration procedure, and illustration of

linear compensation for phase changes temperature drift during calibration

measurements