SPRADD4 October 2023 AM625SIP

5 Via Sharing

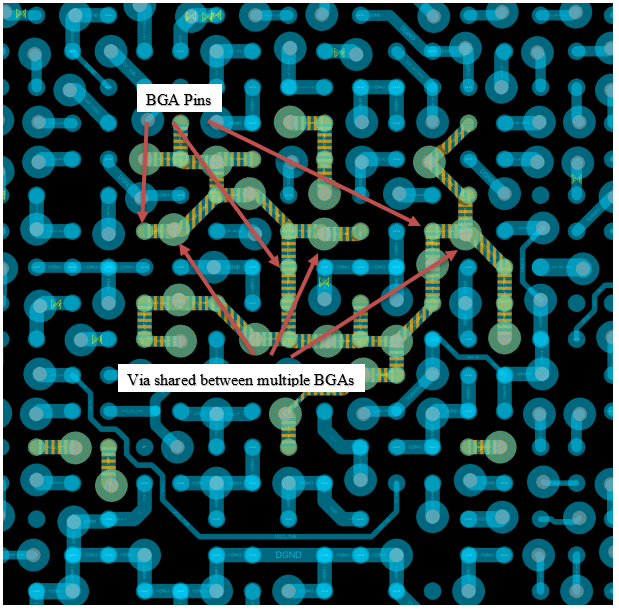

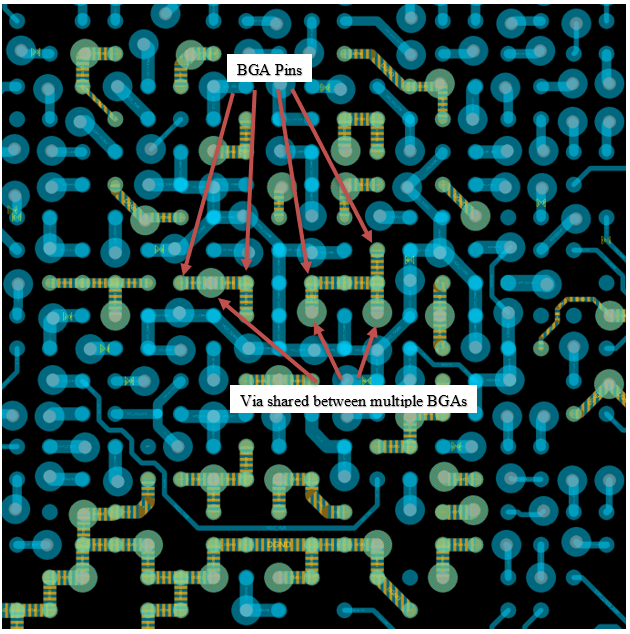

The Via Channel Array BGA pattern implemented on the AM62xSiP design offers several opportunities for via sharing. Vias are shared across BGA pins. Figure 5-1 and Figure 5-2 show the via sharing opportunities for VDD_CORE and VSS power supplies, respectively. Via sharing across BGA pins provides for easier escape routing and robust electrical connection by connecting multiple pins.

Figure 5-1 Via Sharing for VDD_CORE Domain

Figure 5-1 Via Sharing for VDD_CORE Domain Figure 5-2 Via Sharing for VSS

Figure 5-2 Via Sharing for VSS