SWRA689 February 2022 AWR6843 , AWR6843AOP , IWR6843 , IWR6843AOP

- Trademarks

- 1Introduction

- 2Radar System Overview

- 3Active Mode Optimizations

- 4Idle Mode Optimizations

- 5Power Measurement Methods and Results

- 6References

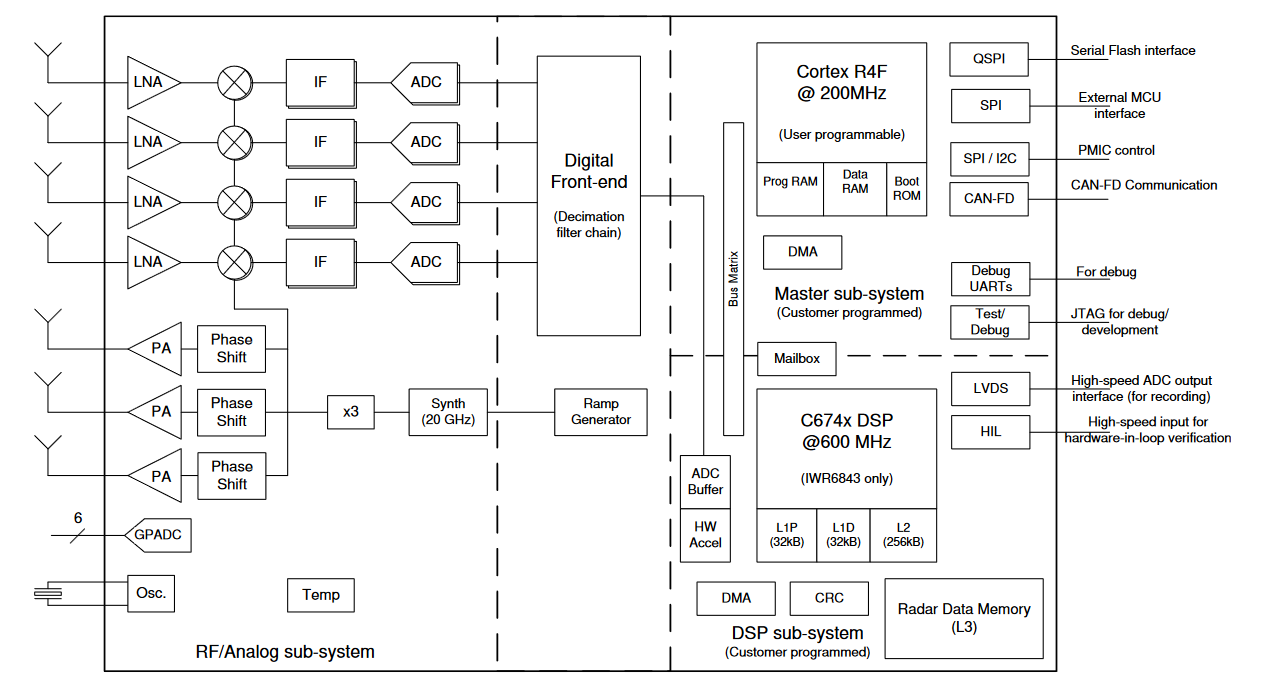

2.1 Architecture Overview

The highly integrated nature of the AWR/IWR6843 Sensor allows for varying schemes of power optimization. For example an application that makes use of only 1Tx/1Rx will see less power consumed during active chirp time than a multi-Tx/Rx application where more angular resolution is required. As such one should be aware of the various performance compromises that result from optimizing for power. However the benefit of integration allows the optimizations to be implemented through software that can even be configured at runtime.

Figure 2-1 AWR6843 Block Diagram

Figure 2-1 AWR6843 Block Diagram