SWRA760A April 2023 – April 2024 AWR2544 , AWR2944

3.3 ROM Boot

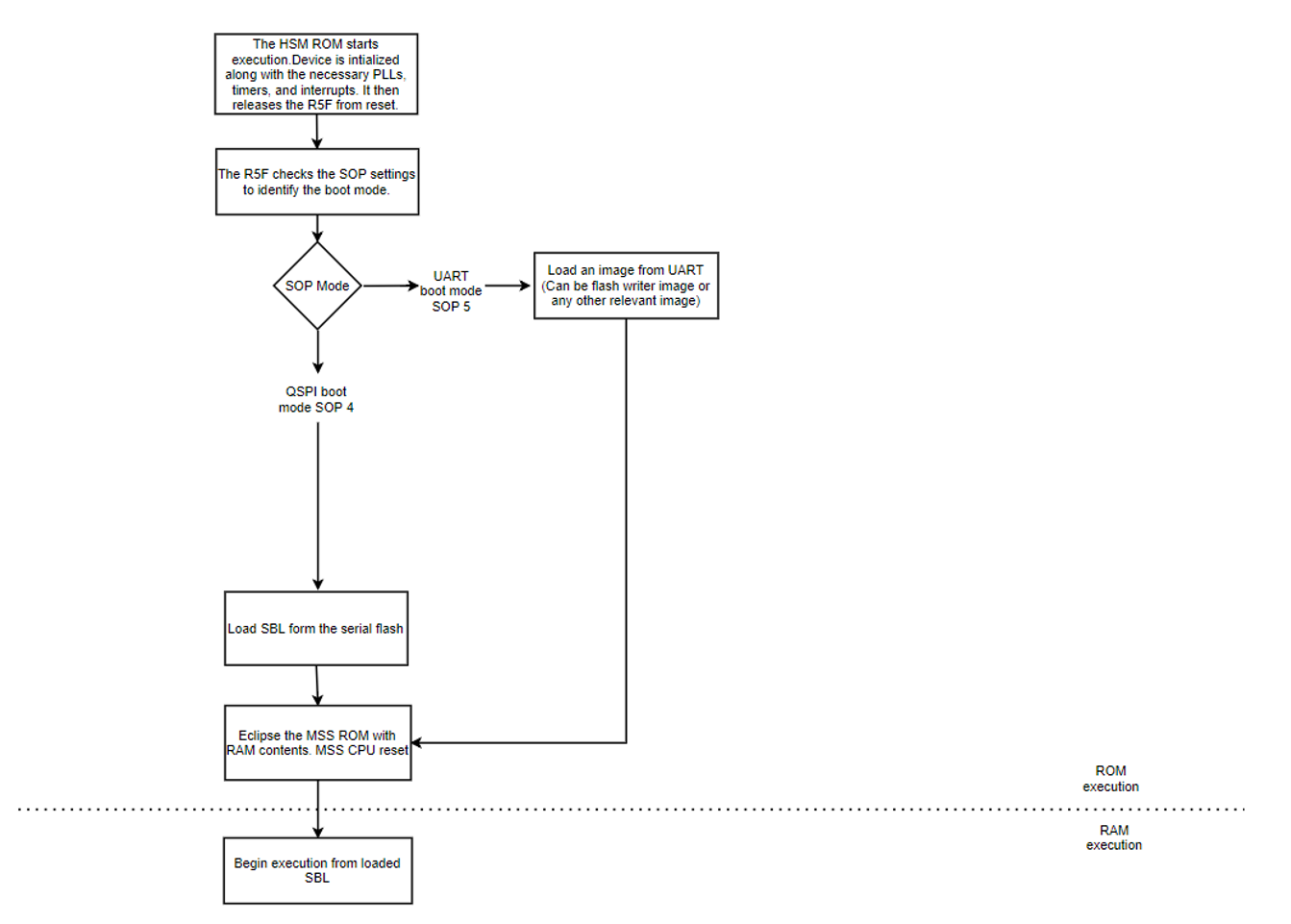

The boot process consists of two consecutive steps: primary or ROM boot loader (RBL) process, followed by the secondary boot loader (SBL) process. As soon as the EVM is powered ON, the ROM bootloader or RBL starts running. The RBL is the primary bootloader. The goal of RBL is to load, verify, optionally decrypt, and launch authentic the R5F software image that accomplishes secure boot goals (in a secure variant). The RBL process is implemented jointly by the R5F and HSM ROM as illustrated in the figure (figure 4) below. The RBL expects the image (SBL in this case) to always be signed.

Figure 3-3 Boot Process

Figure 3-3 Boot ProcessAt high level the boot flow can be explained as below.

- The HSM ROM is the first code to be executed at system reset. HSM ROM executes a set of self-tests for data SRAM, program SRAM, ROM code integrity, as part of device initialization and configures the APLL. HSM ROM also releases the R5F from reset.

- In the HSM ROM PBIST is performed on secure RAM, public RAM and ROM code integrity check is performed for the HSM sub system.

- In the R5F RBL, PBIST is performed on MSS TCMA,MSS TCMB and MSS_L2 memories.

- The R5F checks for the SOP settings and based on continued execution.

- In the UART boot mode/Flashing mode the RBL is expected to get flash programmer (or any other relevant image) from UART. The flash programmer is generally used to download and flash the SBL to the QSPI flash.

- In the QSPI boot mode/Functional mode the RBL loads the SBL from the flash memory on to the internal RAM and begins execution.

Figure 3-4 ROM Boot Flow

Figure 3-4 ROM Boot FlowKey points

- The ROM bootloader loads only one image and to R5F L2 RAM only.

- The ROM bootloader sets up the root clock by starting the APLL. The root clock is at 200MHz