SWRA760A April 2023 – April 2024 AWR2544 , AWR2944

3.2 Preparing the Application for Boot

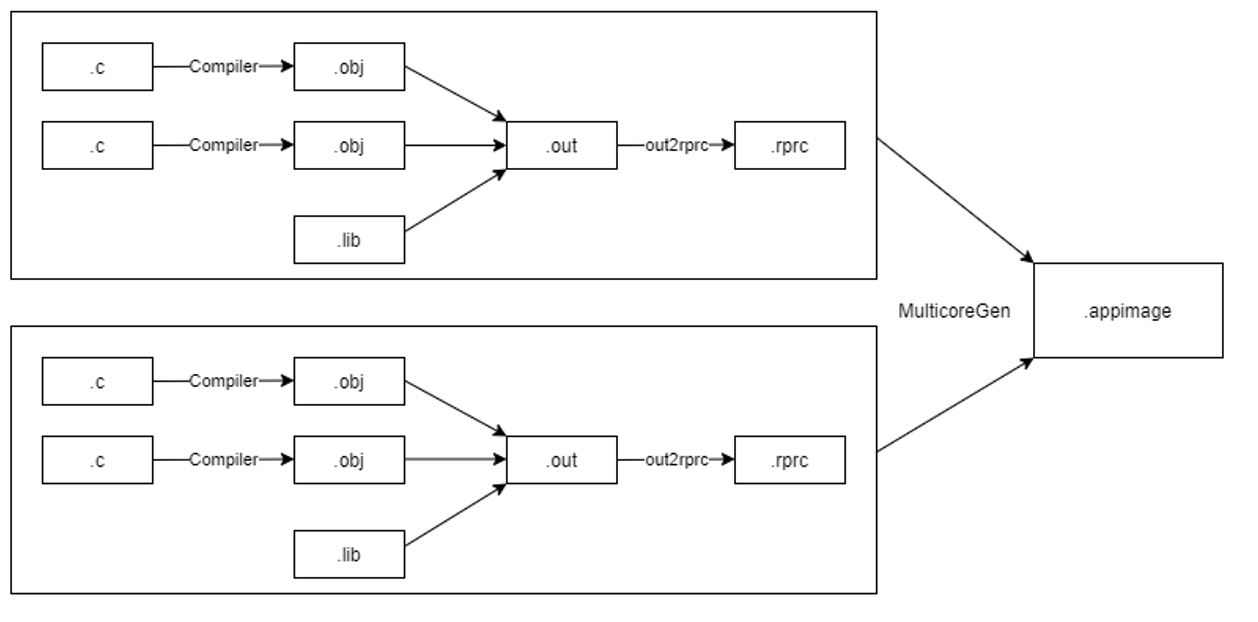

Shown below are the different steps that are done to convert the compiler+linker generated application .out into a format designed for flashing and booting.

- For each CPU, the compiler+linker toolchain is used to create the application .out "ELF" file which can be loaded and run via CCS/ JTAG IDE.

- The below "post build" steps are then used to convert the application

.out into a "flash" friendly format

- For each CPU, out2rpc converts the application executable (.out) into custom TI RPRC (.rprc) image. This tool strips out the initialized sections from the executable file (*.out) and places them in a compact format that the SBL can understand. The output RPRC file is typically much smaller than the original executable (*.out) file.

- multiCoreGen is then used to combine all the RPRC files per CPU into a single .appimage file which is a concatenation of the individual CPU specific RPRC files.

- This .appimage can then be flashed to the device.

Figure 3-1 Post Build Steps

Figure 3-1 Post Build Steps