SLIB006A February 2011 – June 2021 TPS81256 , TPS82084 , TPS82085 , TPS82130 , TPS82140 , TPS82150 , TPS82670 , TPS82671 , TPS826711 , TPS826716 , TPS82672 , TPS826721 , TPS82673 , TPS82674 , TPS826745 , TPS82675 , TPS82676 , TPS826765 , TPS82677 , TPS8268090 , TPS8268105 , TPS8268120 , TPS8268150 , TPS8268180 , TPS82692 , TPS82693 , TPS82695 , TPS826951 , TPS82697 , TPS82698 , TPS82740A , TPS82740B , TPSM82810 , TPSM82813 , TPSM82816 , TPSM82821 , TPSM82821A , TPSM82822 , TPSM82822A , TPSM82823 , TPSM82823A

6 FAQs

Q: What is a MicroSiP™?

A: MicroSiP™ is a miniaturized System-in-Package (SiP) that integrates silicon integrated circuits (ICs) with passive components in a BGA or LGA footprint format.

Q: Is this a lead-free (Pb-free) package?

A: Yes. MicroSiP packages comply with lead-free environmental policies and are RoHS compliant. The BGA bumps and the solder joints on the inductor and capacitors use SAC305 solder paste (3% Ag, 0.5% Cu, 96.5% Sn). Devices with LGA pins have either a NiAu finish (from the electroless nickel immersion gold (ENIG) process) or have a NiPdAu finish (from the electroless nickel electroless palladium immersion gold (ENEPIG) process). The related product folder states which lead finish a particular device has.

Q: Are there any special MicroSiP™ placement requirements?

A: Movement of the MicroSiP from the tape and reel (T&R) to placement on the PCB can be treated as a similar sized BGA or QFN. The nozzle should make contact with the MicroSiP device in the location noted in the package drawing in the data sheet. This is usually on the inductor. The recommended nozzle size is also stated in the package drawing in the data sheet. For MicroSiP devices with BGA pins, an approximate 1-mm diameter nozzle/rubber tip is recommended with a contact area between 0.5–1.0 mm2.

Q: Can I mount MicroSiP to the bottom of the PCB board?

A: Yes. Ideally, the first and second reflow profiles are identical. The reflow profile should follow JEDEC standards for SMT of near-eutectic SnAgCu solder.

Q: Can the MicroSiP™ withstand multiple reflows?

A: Yes. The package is qualified for 3 reflow passes to accommodate first and second side board assembly and a nearby component repair cycle.

Q: What alignment accuracy is possible?

A: TI recommends printing a lead-free solder paste, as described in the PCB layout subsection, before placement of the MicroSiP. Alignment accuracy depends on the pad tolerance of the board and the MicroSiP placement accuracy. MicroSiP packages self-align during reflow—final alignment accuracy is very likely better than the placement accuracy.

Q: Are the integrated inductors shielded?

A: The chip inductor technology used in MicroSiP power modules entirely encloses the inductor winding for maximum shielding. Most MicroSiP devices use an inductor with a magnetic mold compound for best shielding.

Q: How can I measure the temperature of a MicroSiP module?

A: Each MicroSiP data sheet provides safe operating area (SOA) curves that show the thermal limits of the power module on the evaluation module (EVM). If the actual surface temperature of the MicroSiP is desired, a fiber optic temperature measurement setup yields the most accurate results. Many infrared (IR) imaging cameras display lower temperatures than in reality due to reflections off of the integrated inductor on the MicroSiP. Using a thin NiCrNi Thermal couple attached to the integrated inductor can be another precise method to measure the inductor temperature. Use the method described in the application report, An Accurate Thermal-Evaluation Method for the TLV62065 to measure the internal die temperature.

Q: Do I need to solder the exposed thermal pad on the bottom of the MicroSiP?

A: Yes. Just like for most discrete ICs and QFN-packaged devices, the exposed thermal pad (if present) must be soldered to the PCB. It is also recommended to place thermal vias under the exposed thermal pad for maximum height transfer, since the exposed thermal pad is the primary path of heat removal for many MicroSiPs.

Q: How does TI maintain supply chain continuity with the multiple components in each MicroSiP?

A: The passive components used in MicroSiPs are almost always catalog, off-the-shelf components available at multiple suppliers. See also TI’s Product Longevity Statement.

Q: Are MicroSiP modules compliant with EMI standards?

A: Many MicroSiPs, such as the TPSM82823, TPS82085 and LMZ20502, are compliant with CISPR standards for radiated emissions. Consult the device data sheet to see if a specific module has been tested.

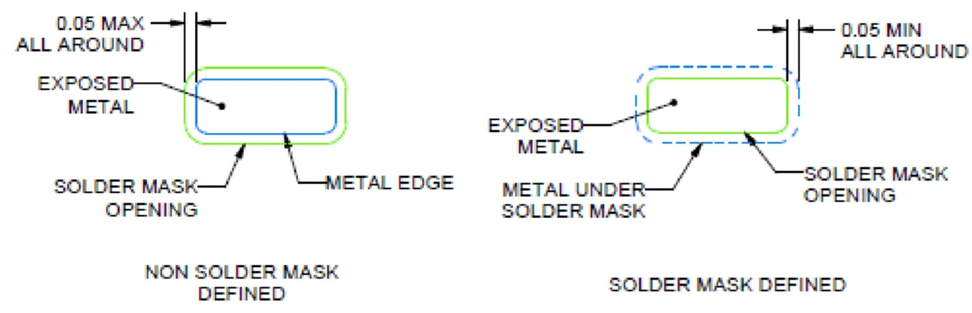

Q: What is the difference between solder mask defined (SMD) and non-solder mask defined (NSMD) land pads?

A: In an SMD pad, there is a flood of copper and the solder mask is pulled back to expose the land pad. There is copper in the entire solder mask opening and extending under the solder mask. In a NSMD pad, the solder mask is pulled back to expose both the copper land pad and a gap between the copper land pad and the solder mask. Since many pins of a MicroSiP are routed to copper pours and planes, the NSMD gap between the copper and the solder mask is filled with copper and the land pad size is larger than expected. SMD land pads usually provide a more consistent land pad size for MicroSiLs with LGA pins, which results in improved solderability. Consult the specific device data sheet and its package drawing for the recommended land pattern. Figure 6-1 shows the difference in SMD and NSMD pads.

Figure 6-1 NSMD Pads Create a Gap Between the Exposed Copper and the Solder Mask, While SMD Pads Expose Only Copper Without any Gap