SLUAA11B February 2020 – August 2021 BQ769142 , BQ76922 , BQ76942 , BQ76952

- Trademarks

- 1Direct Commands

- 2Subcommands

- 3Reading and Writing RAM Registers

- 4I2C With CRC

-

5SPI

With

CRC Examples

- 5.1 Direct Command Example: Alarm Enable - 0x66

- 5.2 Direct Command Example: Cell 1 Voltage - 0x14

- 5.3 Subcommand Example: Device Number - 0x0001

- 5.4 Subcommand Example: FET_ENABLE - 0x0022

- 5.5 Subcommand Example: RESET - 0x0012

- 5.6 RAM Register Read Example: Enabled Protections A

- 5.7 RAM Register Write Example: Enabled Protections A

- 6Simple Code Examples

- 7References

- 8Revision History

4 I2C With CRC

The I2C interface on the BQ769x2 family includes an optional CRC check. The CRC feature can be enabled in the Settings:Configuration:Comm Type register. If this register is changed while using BQStudio, the SWAP_COMM_MODE() subcommand should be executed and then BQStudio should be restarted so that it can detect the new communication mode. Two examples follow of I2C waveform captures with the CRC check enabled.

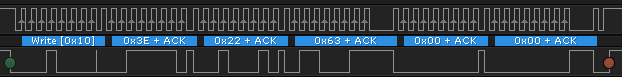

The CRC for the first data byte is computed on all of the bytes after the I2C start up to and including the first data byte. For every data byte after the first byte, the CRC byte is computed for only that byte. In Figure 4-1, using the FET_ENABLE subcommand, the CRC for the first byte is computed for [0x10 0x3E 0x22] - the resulting CRC is 0x63. The CRC for the second byte [0x00] is 0x00.

Figure 4-1 Captured I2C Waveform for FET_ENABLE

Subcommand With CRC

Figure 4-1 Captured I2C Waveform for FET_ENABLE

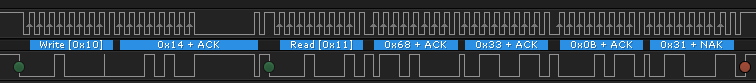

Subcommand With CRCFigure 4-2, using the VCell 1 command, the CRC for the first byte is computed for [0x10 0x14 0x11 0x68] - the resulting CRC is 0x33. The CRC for the second byte [0x0B] is 0x31.

Figure 4-2 Captured I2C Waveform for VCell 1

Command With CRC

Figure 4-2 Captured I2C Waveform for VCell 1

Command With CRC