SLUAA11B February 2020 – August 2021 BQ769142 , BQ76922 , BQ76942 , BQ76952

- Trademarks

- 1Direct Commands

- 2Subcommands

- 3Reading and Writing RAM Registers

- 4I2C With CRC

-

5SPI

With

CRC Examples

- 5.1 Direct Command Example: Alarm Enable - 0x66

- 5.2 Direct Command Example: Cell 1 Voltage - 0x14

- 5.3 Subcommand Example: Device Number - 0x0001

- 5.4 Subcommand Example: FET_ENABLE - 0x0022

- 5.5 Subcommand Example: RESET - 0x0012

- 5.6 RAM Register Read Example: Enabled Protections A

- 5.7 RAM Register Write Example: Enabled Protections A

- 6Simple Code Examples

- 7References

- 8Revision History

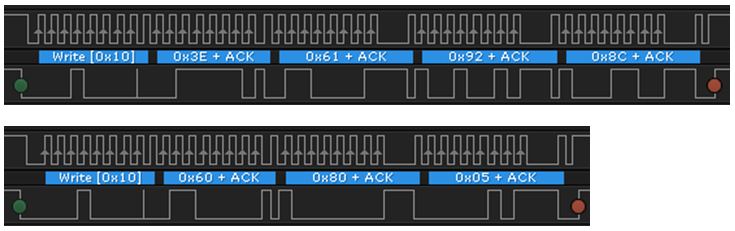

3.3 Write 'Enabled Protections A'

In this example, the CUV (undervoltage) protection feature is enabled along with the default protections. This requires writing 0x8C to RAM address 0x9261. The checksum is calculated on the address and data (0x61, 0x92, 0x8C) and is the complement of the sum of these bytes. The length also includes the two bytes for device address and command address for a total length of 5.

Figure 3-3 Captured Waveform for Writing

to Enabled Protections A

Figure 3-3 Captured Waveform for Writing

to Enabled Protections A