SLUAAJ7 June 2022 UCC256402 , UCC256403 , UCC256404

- Abstract

- Trademarks

- 1UCC25640x Selection Guide

- 2UCC25640x Features Brief Overview

- 3UCC25640x Power Up Guidelines and Debugging Notes

- 4References

2.8.4 Restart or Latch

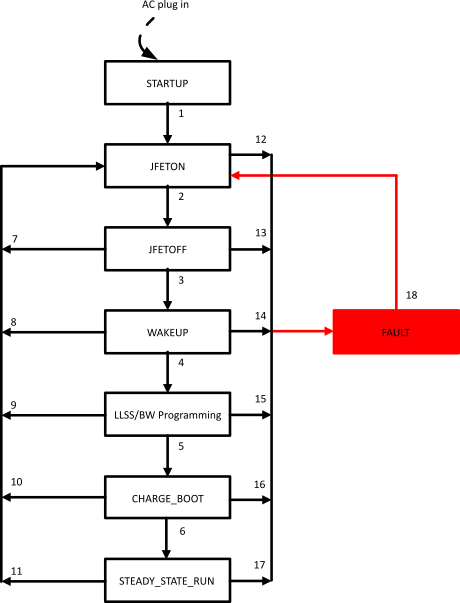

Figure 2-38 State Diagram for UCC25640x

Figure 2-38 State Diagram for UCC25640x- Over Temperature (OTP), Low DC Input Voltage (BLK UVLO), Over voltage at the DC Input (BLK OVP), RVCC UVLO will also get part into fault state

- For “restart” IC version, IC goes into fault state (gate turns off, RVCC shut down, etc) and stays in fault idle state for 1s, before entering JFETON.

- For “latch” IC version, IC goes into fault state and stay latched. VCC is supplied from HV pin and regulated at ~14.5 V.

- For external fault protection, pull down the BLK pin voltage.