SLUAAJ7 June 2022 UCC256402 , UCC256403 , UCC256404

- Abstract

- Trademarks

- 1UCC25640x Selection Guide

- 2UCC25640x Features Brief Overview

- 3UCC25640x Power Up Guidelines and Debugging Notes

- 4References

2.6.6 Operation when Burst Mode Disabled

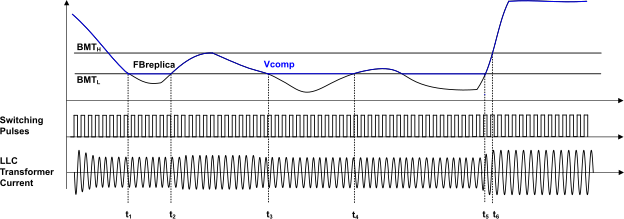

Figure 2-29 Switching Pattern with Burst Mode Disabled

Figure 2-29 Switching Pattern with Burst Mode Disabled- Figure 2-29 shows that, when the burst mode is disabled (using option 7 given in Table 2-1), switching pulses are not turned off even when the Fbreplica becomes lower than BMTL.

- BMTL becomes the effective maximum switching frequency limiter

- When burst mode is disabled, FBreplica needs to be higher than BMTL at steady state. Otherwise, LLC output voltage will lose regulation as it continues deliver more energy than what is demanded from the feedback. For a transient period, it is acceptable for FBreplica to be lower than BMTL.