SLVAF01 October 2020 TPS55340

3.2 Redesign Procedure to Mitigate Vsw

The first step is to check the VOR level and reduce it after ensuring the peak primary current does not touch IC’s internal current limit level because if we reduce VOR, as Figure 1-1, current will be increased. This then changes the zener diode rating accruing to VOR level again.

Figure 3-2 Design change about VOR and Zener Diode

|

Before |

After |

|

|---|---|---|

|

VOR |

10 V |

8 V |

|

Zener Rating |

15 V |

10 V |

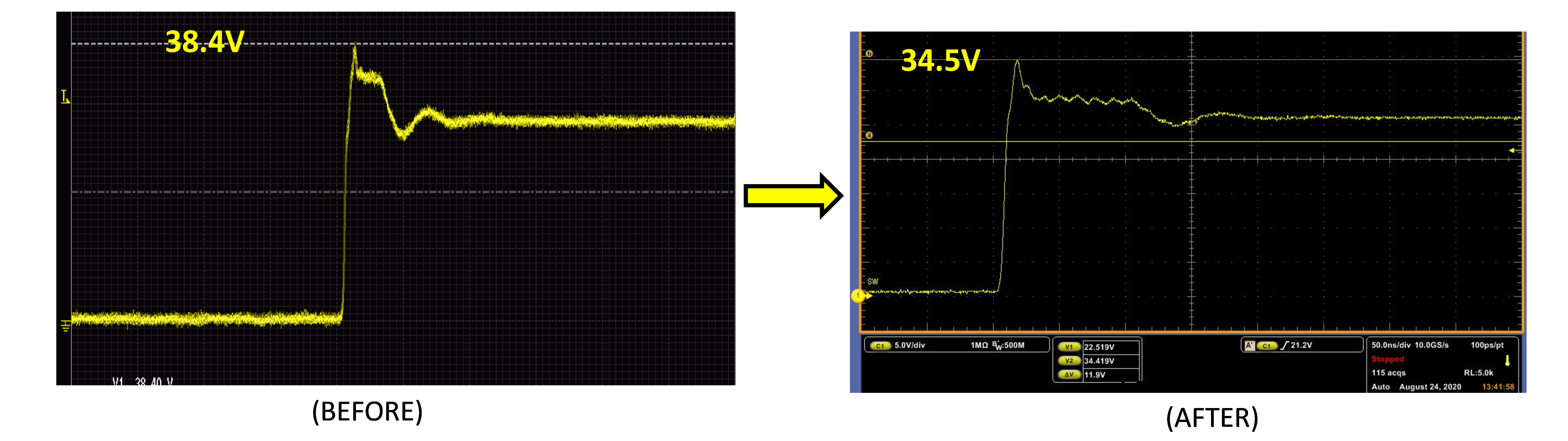

Figure 3-3 plots more mitigated Vsw’s peak voltage. It reduced from 38.4 V to 34.5 after redesign reflected voltage and zener diode rating. But it still needs some additional margin to 40V AMR

Figure 3-3 Scope Image After Changing VOR

and Zener Diode Rating

Figure 3-3 Scope Image After Changing VOR

and Zener Diode Rating