SLVUBX0A July 2021 – January 2022 TPSM8A28 , TPSM8A29

5.6 Startup and Shutdown

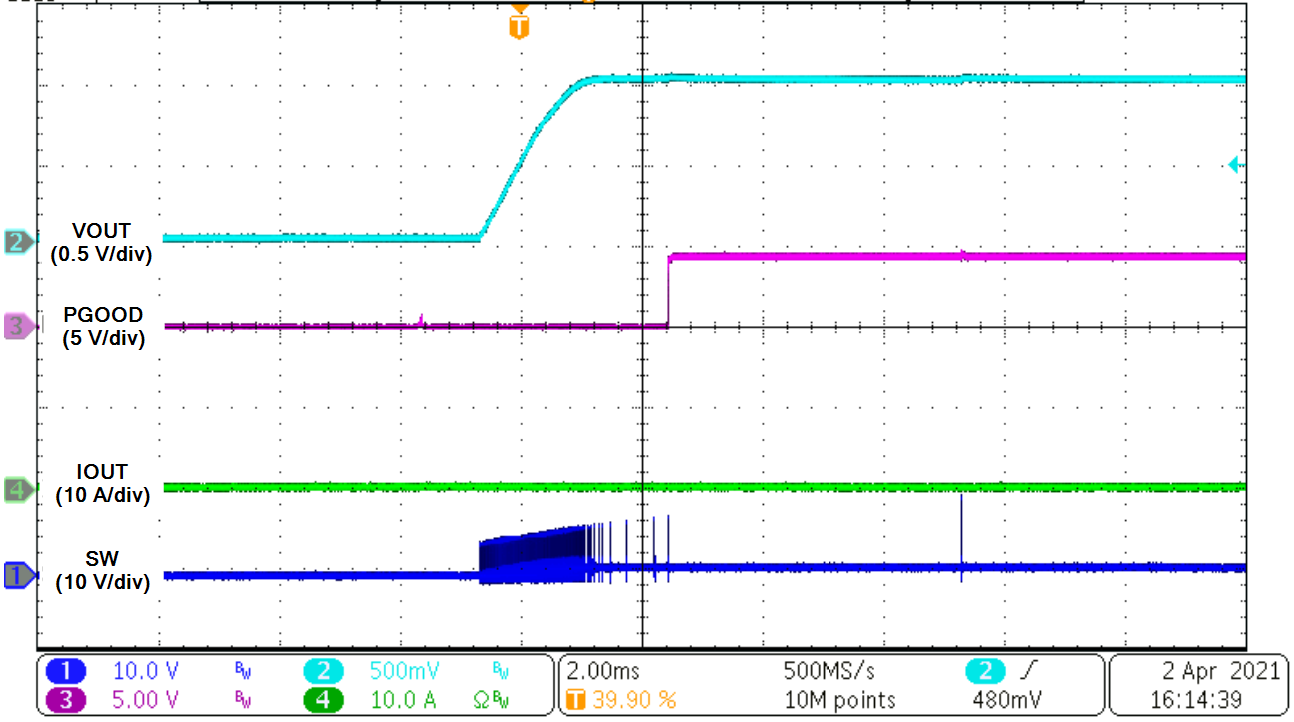

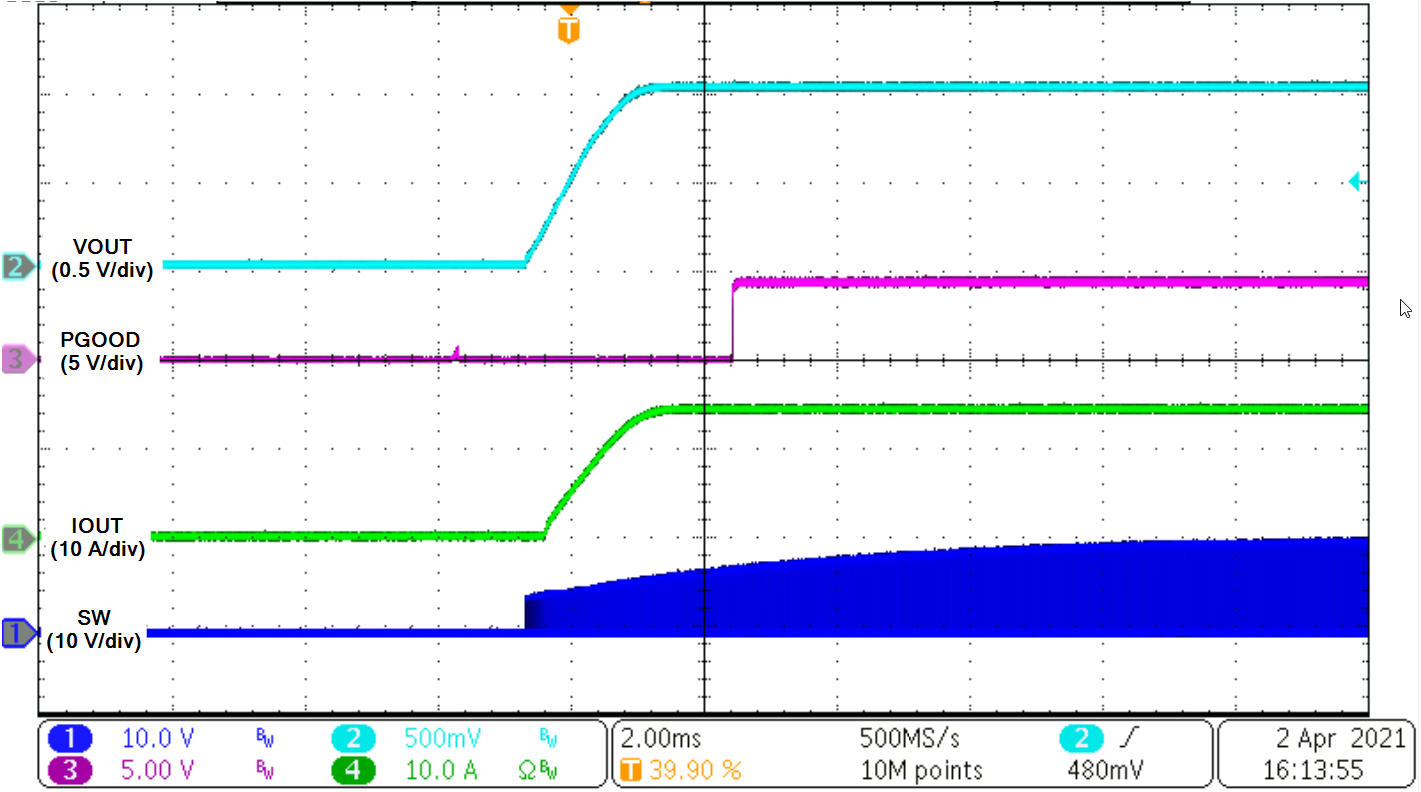

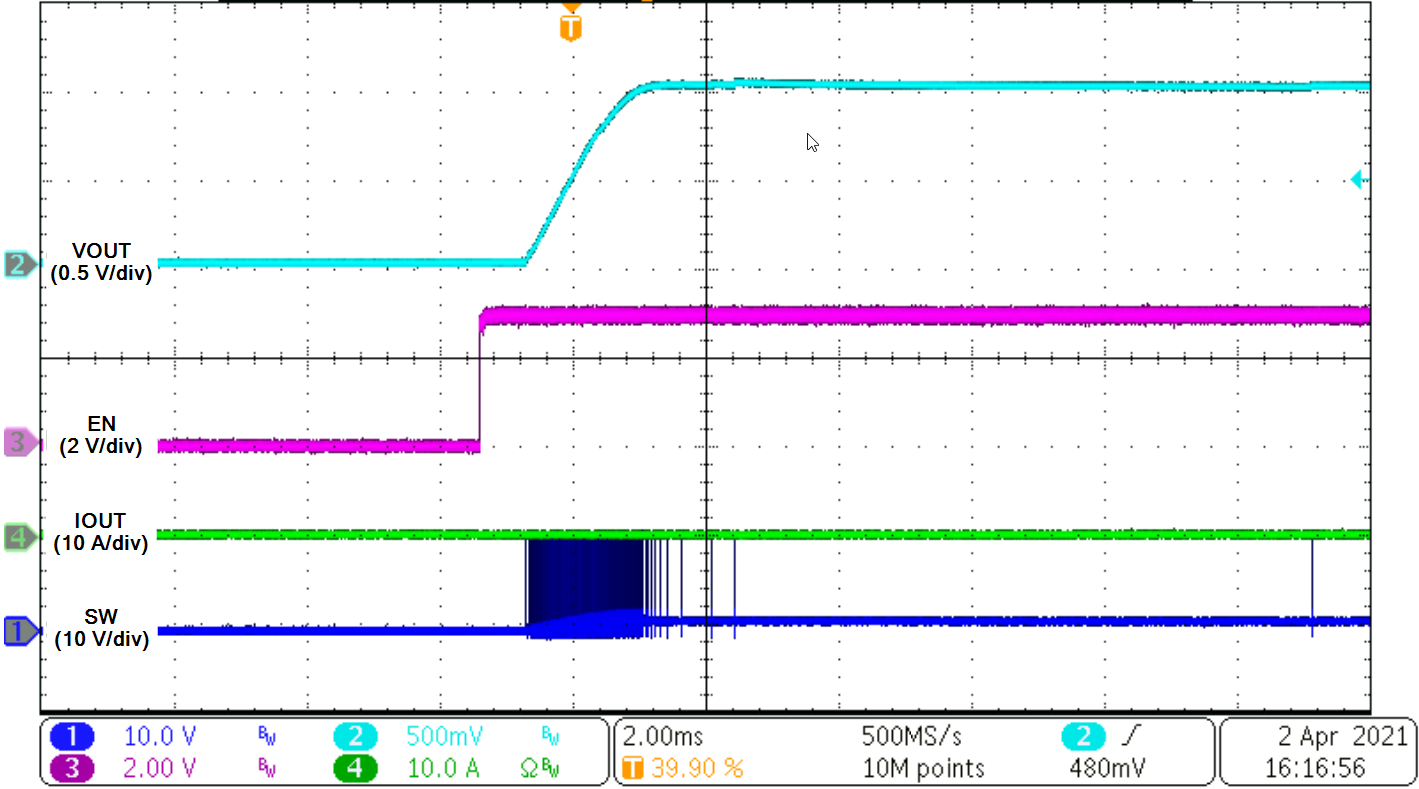

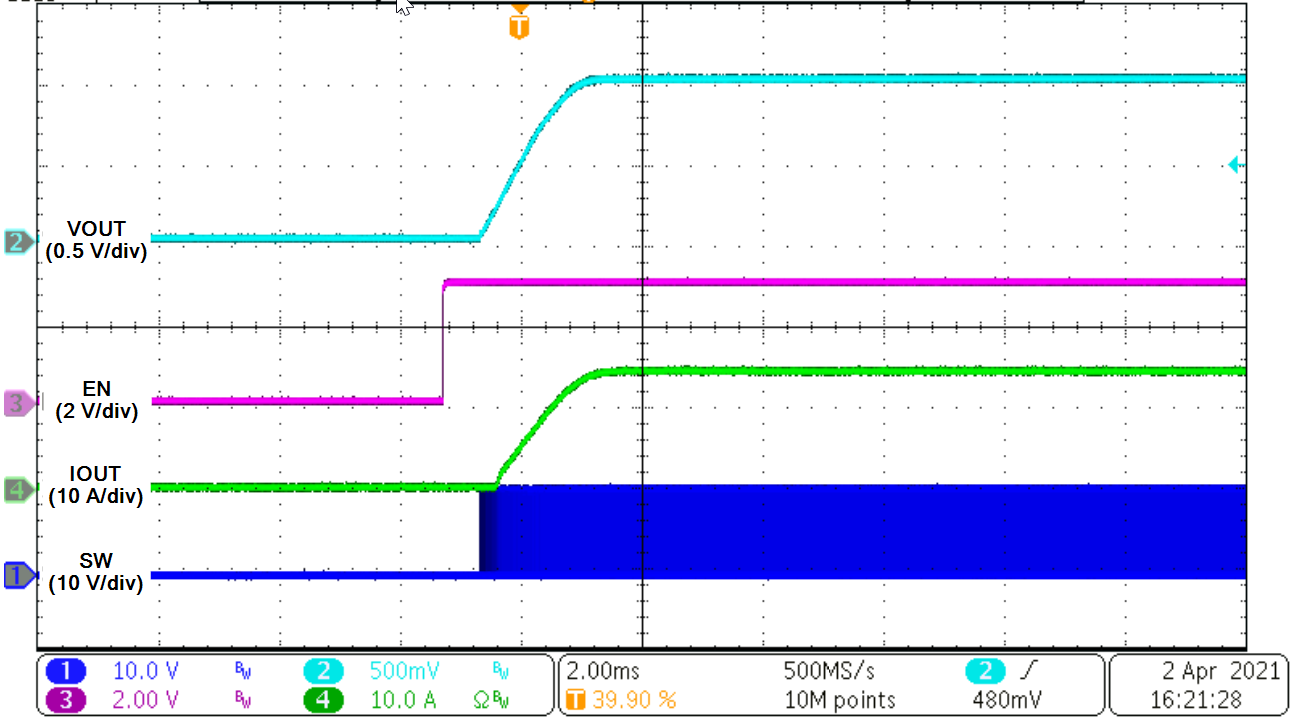

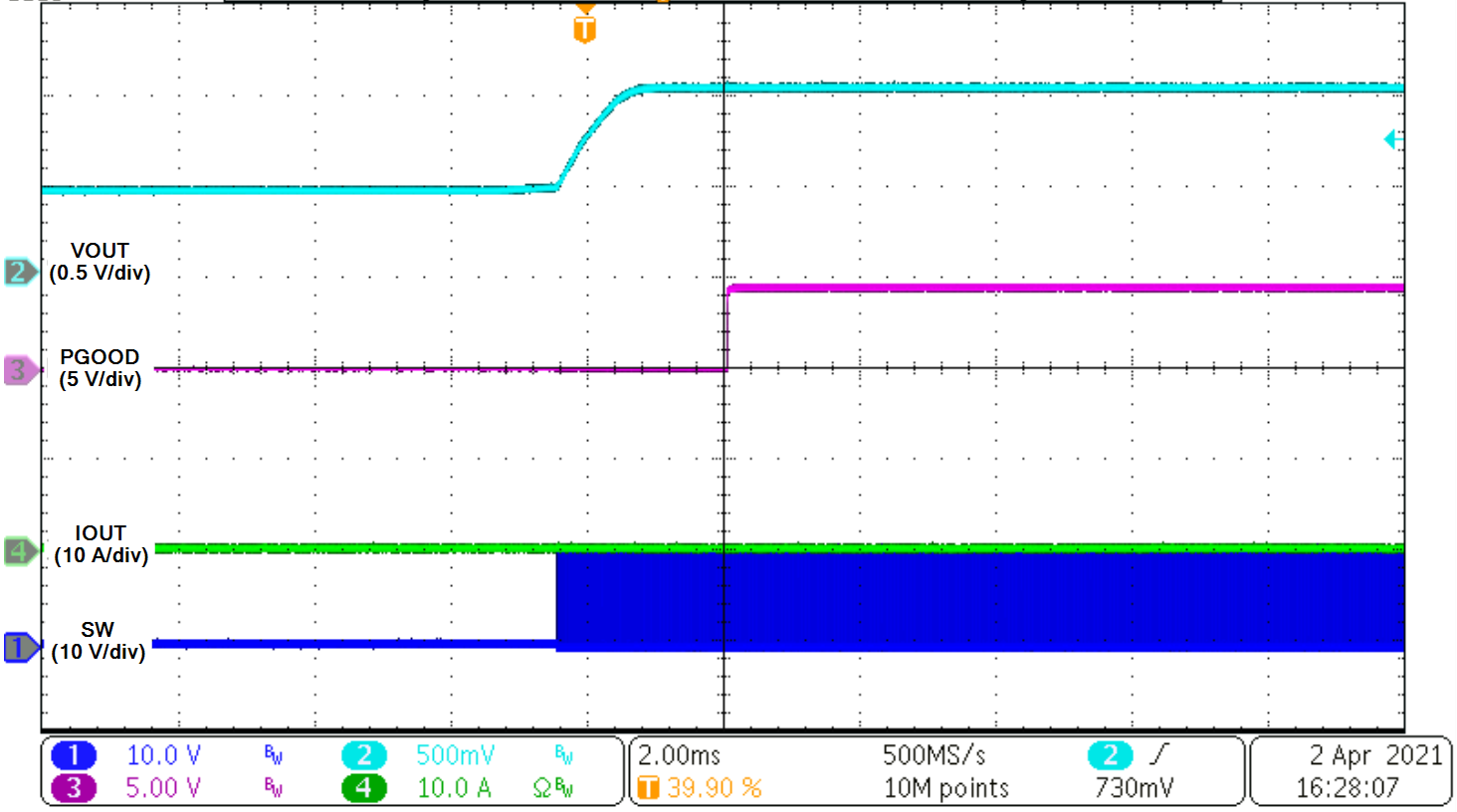

This section contains oscilloscope images showing the startup and shutdown behavior of the TPSM8A29 under different load conditions. All images were taken at 25°C.

Equation 8. VIN = 12 V, VOUT =

1.0 V, COUT = 8x47 μF

| VIN = 12 V | IOUT = 0 A | fsw = 600 kHz | Internal bias | DCM |

| VIN = 12 V | IOUT = 15 A | fsw = 600 kHz | Internal bias | FCCM |

| VIN = 12 V | IOUT = 0 A | fsw = 600 kHz | Internal bias | DCM |

| VIN = 12 V | IOUT = 15 A | fsw = 600 kHz | Internal bias | FCCM |

| VIN = 12 V | IOUT = 0 A | fsw = 600 kHz | Internal bias | FCCM |