JAJSQ89D december 2015 – september 2020 HD3SS3220

PRODUCTION DATA

3 概要

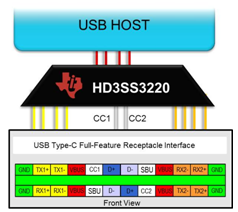

HD3SS3220 は、DRP ポート・コントローラ付きの USB SuperSpeed (SS) 2:1 マルチプレクサです。このデバイスは、USB Type-C を実装するエコシステム向けに、チャネル構成 (CC) ロジックと 5V VCONN ソースを提供します。HD3SS3220 は、ダウンストリーム側ポート (DFP)、アップストリーム側ポート (UFP)、またはデュアル・ロール・ポート (DRP) として構成できるため、あらゆるアプリケーションに理想的です。

HD3SS3220 が DRP モードの場合、Type-C 仕様に従って、自らを DFP または UFP として交互に提示します。CC ロジック・ブロックは、USB ポートが接続されたかどうかとポートの役割を判断するため、CC1 および CC2 ピンのプルアップ抵抗またはプルダウン抵抗を監視します。USB ポートが接続されると、CC ロジックはケーブルの向きも判定し、それに応じて USB SS マルチプレクサを構成します。最後に、CC ロジックは Type-C 電流モード (DFP および UFP モードでそれぞれデフォルト、中、高) をアドバタイズまたは検出します。

内蔵マルチプレクサの動的特性は非常に優れているため、SS 信号アイ・ダイアグラムへの減衰が最小限で、ジッタはわずかしか発生しない、スイッチングが可能です。このデバイスのスイッチ・パスは、適応型同相電圧トラッキングを採用しており、RX チャネルと TX チャネルの同相電圧が異なるのにもかかわらず、同一のチャネルを形成します。

| 部品番号 | パッケージ | 本体サイズ (公称) |

|---|---|---|

| HD3SS3220 | VQFN RNH (30) | 2.50mm × 4.50mm |

| HD3SS3220I |

概略回路図

概略回路図 代表的なアプリケーション

代表的なアプリケーション