SPRUJ51 june 2023

- 1

- 1Abstract

- 2EVM Revisions and Assembly Variants

- Trademarks

-

3System Description

- 3.1 Key Features

- 3.2 Functional Block Diagram

- 3.3 AM62x-Low Power SK EVM Interface Mapping

- 3.4 Power ON OFF Procedures

- 3.5

Peripheral and Major Component Description

- 3.5.1 Clocking

- 3.5.2 Reset

- 3.5.3 OLDI Display Interface

- 3.5.4 CSI Interface

- 3.5.5 Audio Codec Interface

- 3.5.6 HDMI Display Interface

- 3.5.7 JTAG Interface

- 3.5.8 Test Automation Header

- 3.5.9 UART Interface

- 3.5.10 USB Interface

- 3.5.11 Memory Interfaces

- 3.5.12 Ethernet Interface

- 3.5.13 GPIO Port Expander

- 3.5.14 GPIO Mapping

- 3.5.15 Power

- 3.5.16 AM62x-Low Power SK EVM User Setup and Configuration

- 3.5.17 Expansion Headers

- 3.5.18 Push Buttons

- 3.5.19 I2C Address Mapping

- 4Known Issues and Modifications

- 5Revision History

- 6IMPORTANT NOTICE AND DISCLAIMER

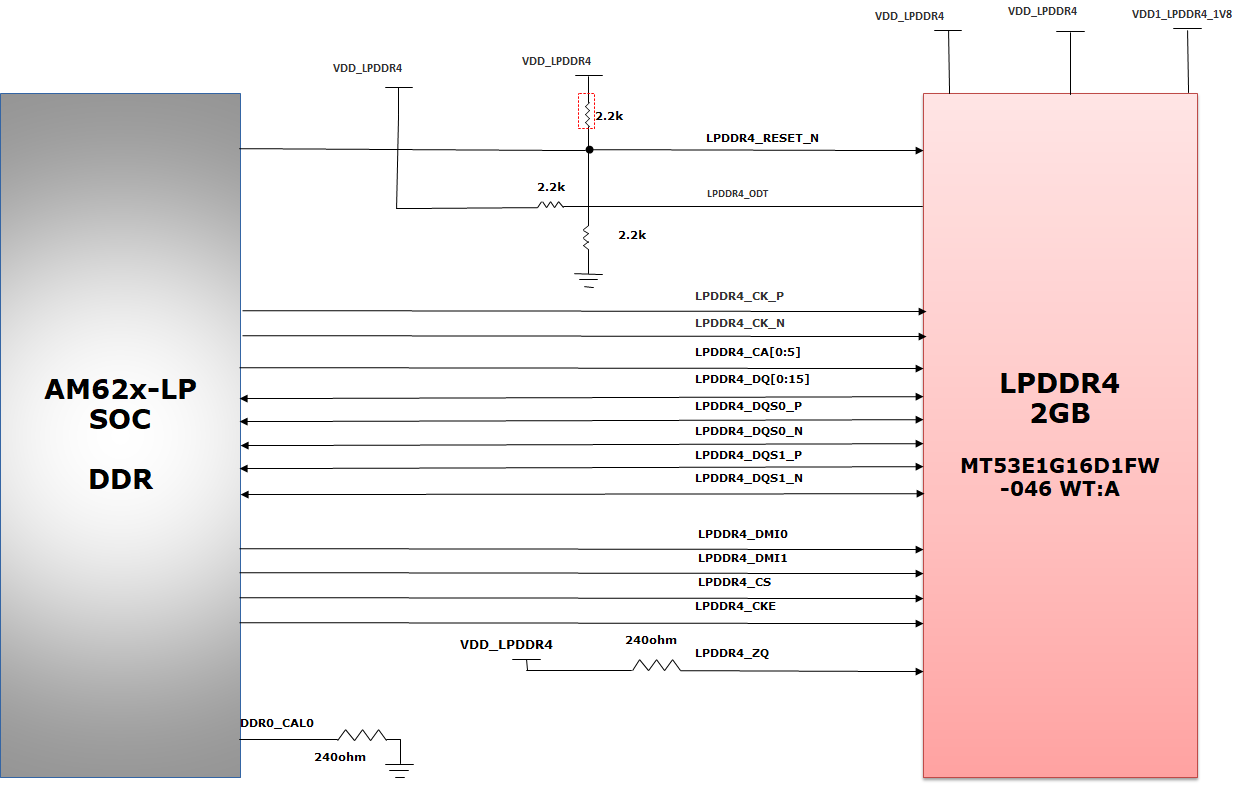

3.5.11.1 LPDDR4 Interface

AM62x-Low Power SK EVM has 2GB, 16bit wide LPDDR4 memory with operating speed of up to 2133MT/s. Micron's MT53E1G16D1FW-046 WT:A isused. This uses two x8 8Gb Micron dies to make one x16 interface. The LPDDR memory is mounted on-board (single chip). The Placement and routing of LPDDR4 device is point to point.

The LPDDR4 requires 1.8V and thus reduces power demand. The devices require I/O power of 1.1V. LPDDR4 reset is an active low signal, which is controlled by SoC and the signal is pulled down to set the default active state. A footprint for pull up is also provided.

Figure 3-18 LPDDR4 Interface Block Diagram

Figure 3-18 LPDDR4 Interface Block Diagram