SPRUJ51 june 2023

- 1

- 1Abstract

- 2EVM Revisions and Assembly Variants

- Trademarks

-

3System Description

- 3.1 Key Features

- 3.2 Functional Block Diagram

- 3.3 AM62x-Low Power SK EVM Interface Mapping

- 3.4 Power ON OFF Procedures

- 3.5

Peripheral and Major Component Description

- 3.5.1 Clocking

- 3.5.2 Reset

- 3.5.3 OLDI Display Interface

- 3.5.4 CSI Interface

- 3.5.5 Audio Codec Interface

- 3.5.6 HDMI Display Interface

- 3.5.7 JTAG Interface

- 3.5.8 Test Automation Header

- 3.5.9 UART Interface

- 3.5.10 USB Interface

- 3.5.11 Memory Interfaces

- 3.5.12 Ethernet Interface

- 3.5.13 GPIO Port Expander

- 3.5.14 GPIO Mapping

- 3.5.15 Power

- 3.5.16 AM62x-Low Power SK EVM User Setup and Configuration

- 3.5.17 Expansion Headers

- 3.5.18 Push Buttons

- 3.5.19 I2C Address Mapping

- 4Known Issues and Modifications

- 5Revision History

- 6IMPORTANT NOTICE AND DISCLAIMER

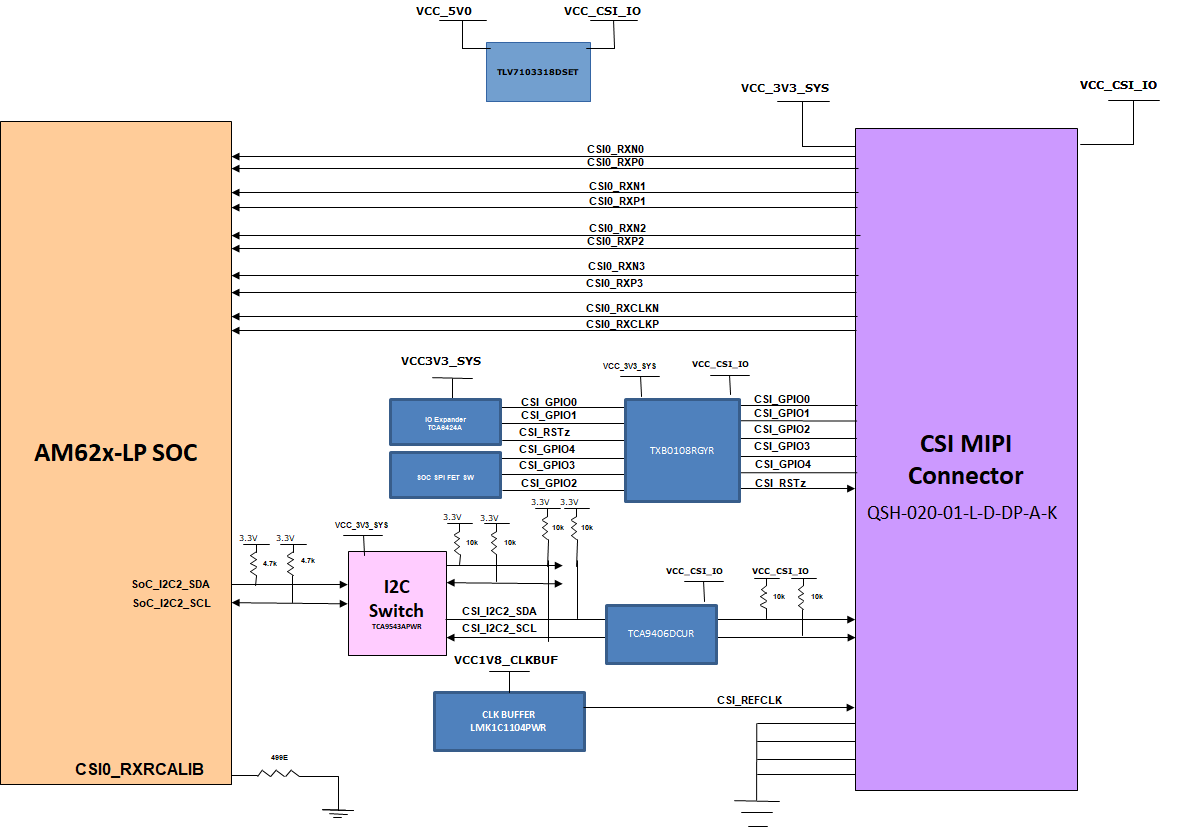

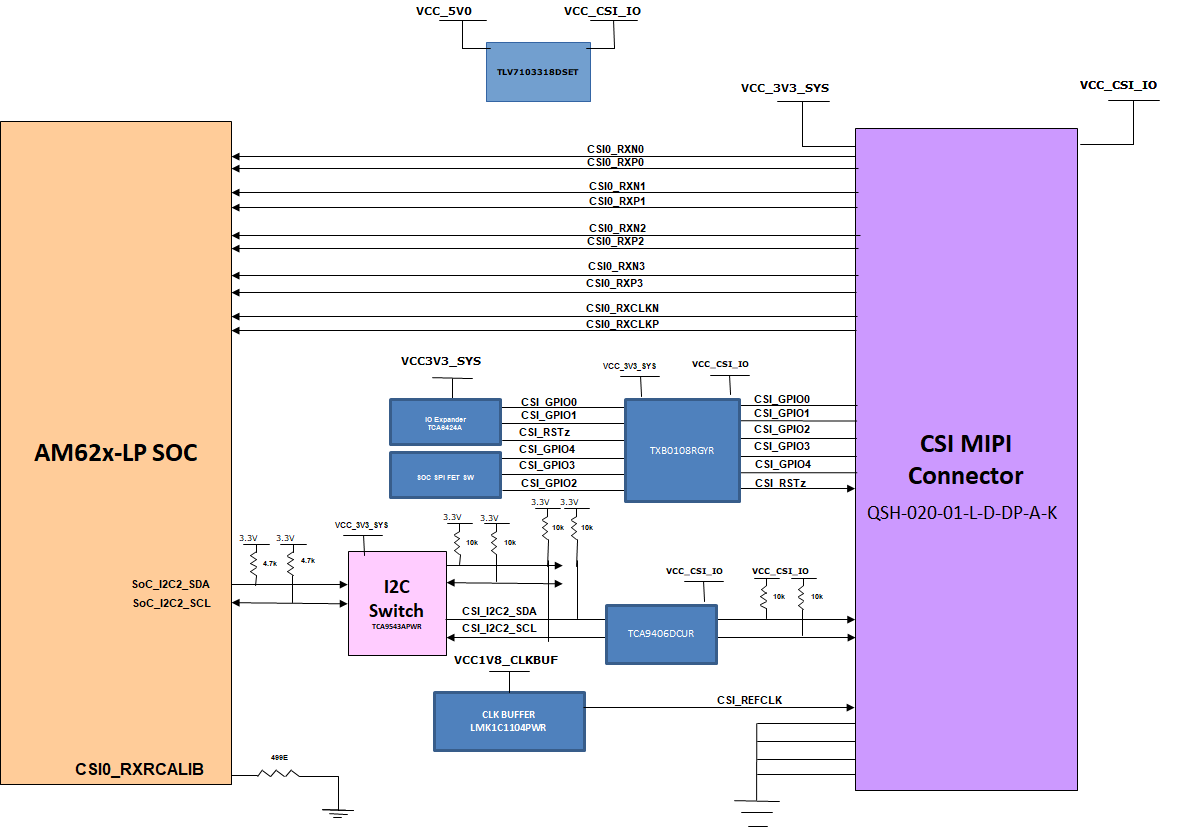

3.5.4 CSI Interface

The CSI-2 interface from the AM62x 17x17 SoC is terminated

to a 40 pin Camera MIPI connector QSH-020-01-L-D-DP-A-K. The SoC supports 4 CSI RX Lanes, four

are pinned out on the SKEVM. The table below contains 40 pin Camera MIPI connector pin-out.

SoC I2C2 signals are also connected to the CSI Header. IO Expander GPIO signals are connected

to the camera GPIO’s.

Figure 3-10 CSI Interface Block Diagram

Figure 3-10 CSI Interface Block Diagram

Figure 3-10 CSI Interface Block Diagram

Figure 3-10 CSI Interface Block DiagramTable 3-5 CSI Camera Connector J19

Pinout

| Pin No | Pin Description | Pin No | Pin Description |

| 1 | NC | 21 | CSI0_RXP3 |

| 2 | CSI_I2C2_SCL_BUFF | 22 | CSI_GPIO4_buff |

| 3 | NC | 23 | CSI0_RXN3 |

| 4 | CSI_I2C2_SDA_BUFF | 24 | Ground |

| 5 | CSI0_RXCLKP | 25 | NC |

| 6 | CSI_GPIO0_buff | 26 | NC |

| 7 | CSI0_RXCLKN | 27 | NC |

| 8 | CSI_GPIO1_buff | 28 | NC |

| 9 | CSI0_RXP0 | 29 | NC |

| 10 | CSI_REFCLK | 30 | VCC_3V3_SYS |

| 11 | CSI0_RXN0 | 31 | NC |

| 12 | Ground | 32 | VCC_3V3_SYS |

| 13 | CSI0_RXP1 | 33 | NC |

| 14 | CSI_RSTz_buff | 34 | VCC_3V3_SYS |

| 15 | CSI0_RXN1 | 35 | NC |

| 16 | Ground | 36 | VCC_3V3_SYS |

| 17 | CSI0_RXP2 | 37 | NC |

| 18 | CSI_GPIO2_buff | 38 | VCC_CSI_IO |

| 19 | CSI0_RXN2 | 39 | NC |

| 20 | CSI_GPIO3_buff | 40 | VCC_CSI_IO |