SPRUJ51 june 2023

- 1

- 1Abstract

- 2EVM Revisions and Assembly Variants

- Trademarks

-

3System Description

- 3.1 Key Features

- 3.2 Functional Block Diagram

- 3.3 AM62x-Low Power SK EVM Interface Mapping

- 3.4 Power ON OFF Procedures

- 3.5

Peripheral and Major Component Description

- 3.5.1 Clocking

- 3.5.2 Reset

- 3.5.3 OLDI Display Interface

- 3.5.4 CSI Interface

- 3.5.5 Audio Codec Interface

- 3.5.6 HDMI Display Interface

- 3.5.7 JTAG Interface

- 3.5.8 Test Automation Header

- 3.5.9 UART Interface

- 3.5.10 USB Interface

- 3.5.11 Memory Interfaces

- 3.5.12 Ethernet Interface

- 3.5.13 GPIO Port Expander

- 3.5.14 GPIO Mapping

- 3.5.15 Power

- 3.5.16 AM62x-Low Power SK EVM User Setup and Configuration

- 3.5.17 Expansion Headers

- 3.5.18 Push Buttons

- 3.5.19 I2C Address Mapping

- 4Known Issues and Modifications

- 5Revision History

- 6IMPORTANT NOTICE AND DISCLAIMER

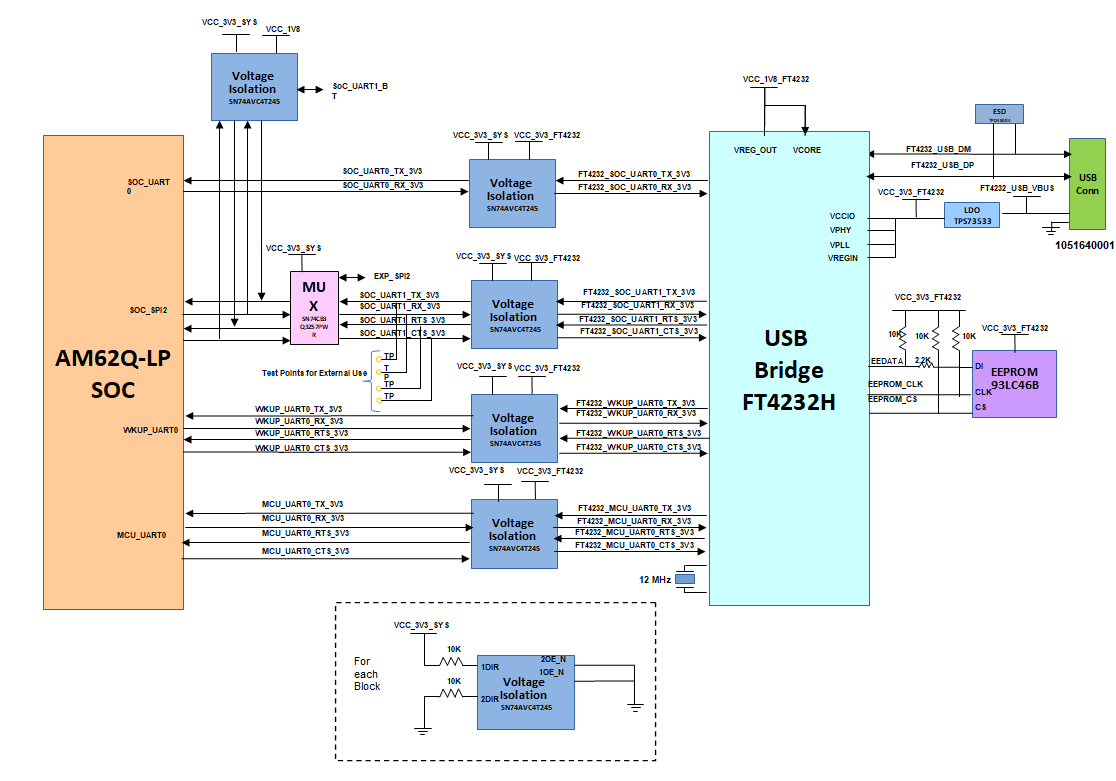

3.5.9 UART Interface

The four UART ports of the AM62x SoC (MCU UART0, WKUP UART0, SOC UART0 and SOC UART1) are interfaced with an FTDI FT4232HL for UART-to-USB functionality and terminated on a USB micro-B connector (J17) on board. When the AM62x-Low Power SK EVM is connected to a Host using USB cable, the computer can establish a Virtual Com Port which can be used with any terminal emulation application. The FT4232HL is bus powered.

Since the circuit is powered through BUS power, the connection to the COM port will not be lost when the SK EVM power is removed.

| UART Port | USB to UART Bridge | USB Connector | COM Port |

|---|---|---|---|

| SOC_UART0 | FT4232HL | J17 | COM1 |

| SOC_UART1 | COM2 | ||

| WKUP_UART0 | COM3 | ||

| MCU_UART0 | COM4 | ||

The FT4232 chip is configured to operate in ‘Single chip USB to four channel UART’ mode and will take the configuration file from the external SPI EEPROM connected to it. The EEPROM (93LC46B) supports 1Mbit/s cloc krate. The EEPROM is programmable in-circuit over USB using a utility program called FT_PROG available from FTDI's web site. The FT_PROG is also used for programming the board serial number for users to identify the connected COM port with board serial number when one or more boards are connected to the computer.

Figure 3-15 UART Interface Block Diagram

Figure 3-15 UART Interface Block Diagram