SLUSC16B November 2015 – March 2019

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- PW|16

Thermal pad, mechanical data (Package|Pins)

Orderable Information

8.2.3 Application Curves

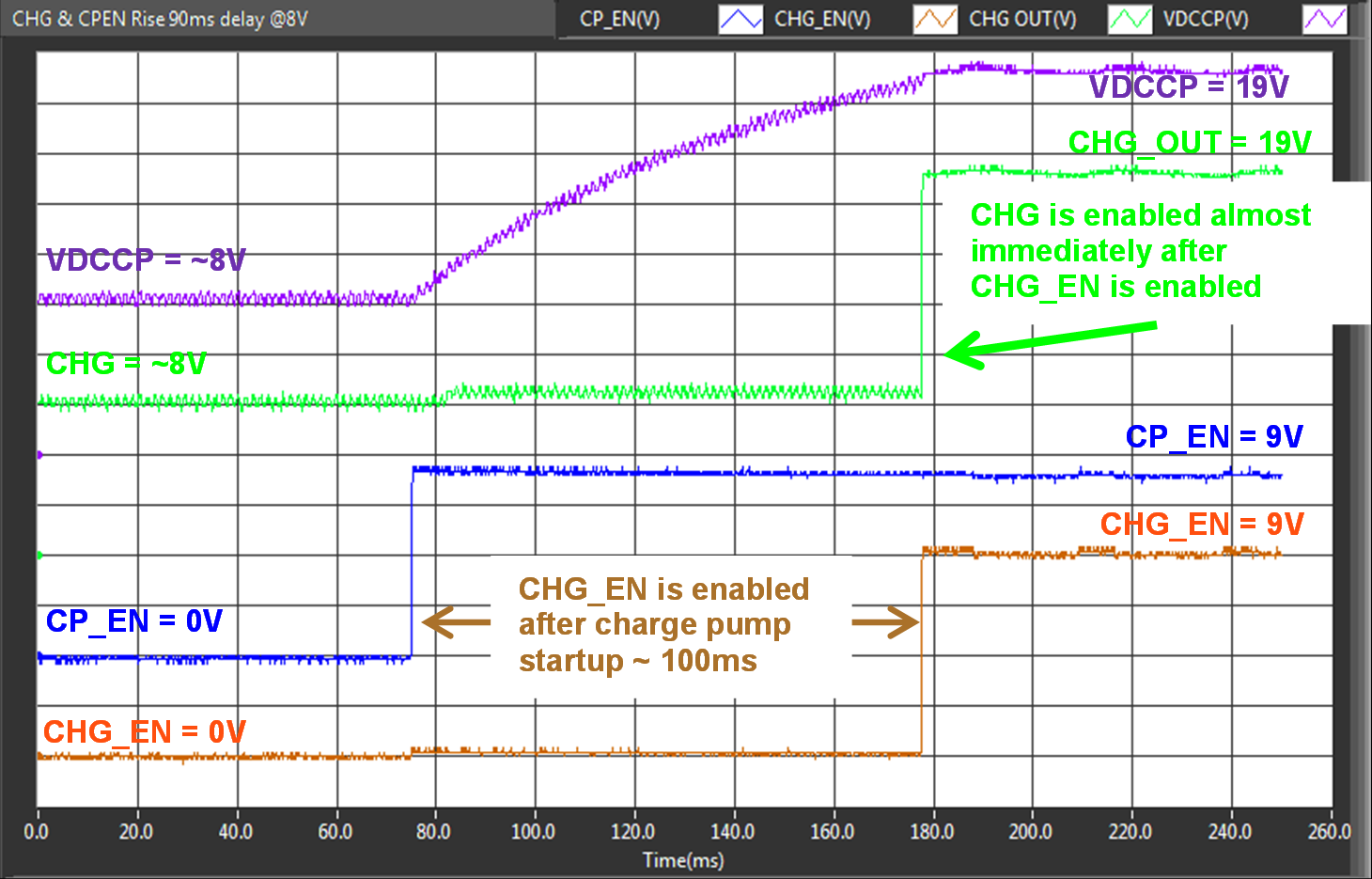

| CHG output reacts to the CHG_EN signal immediately. Similar behavior applies to the DSG pin. |

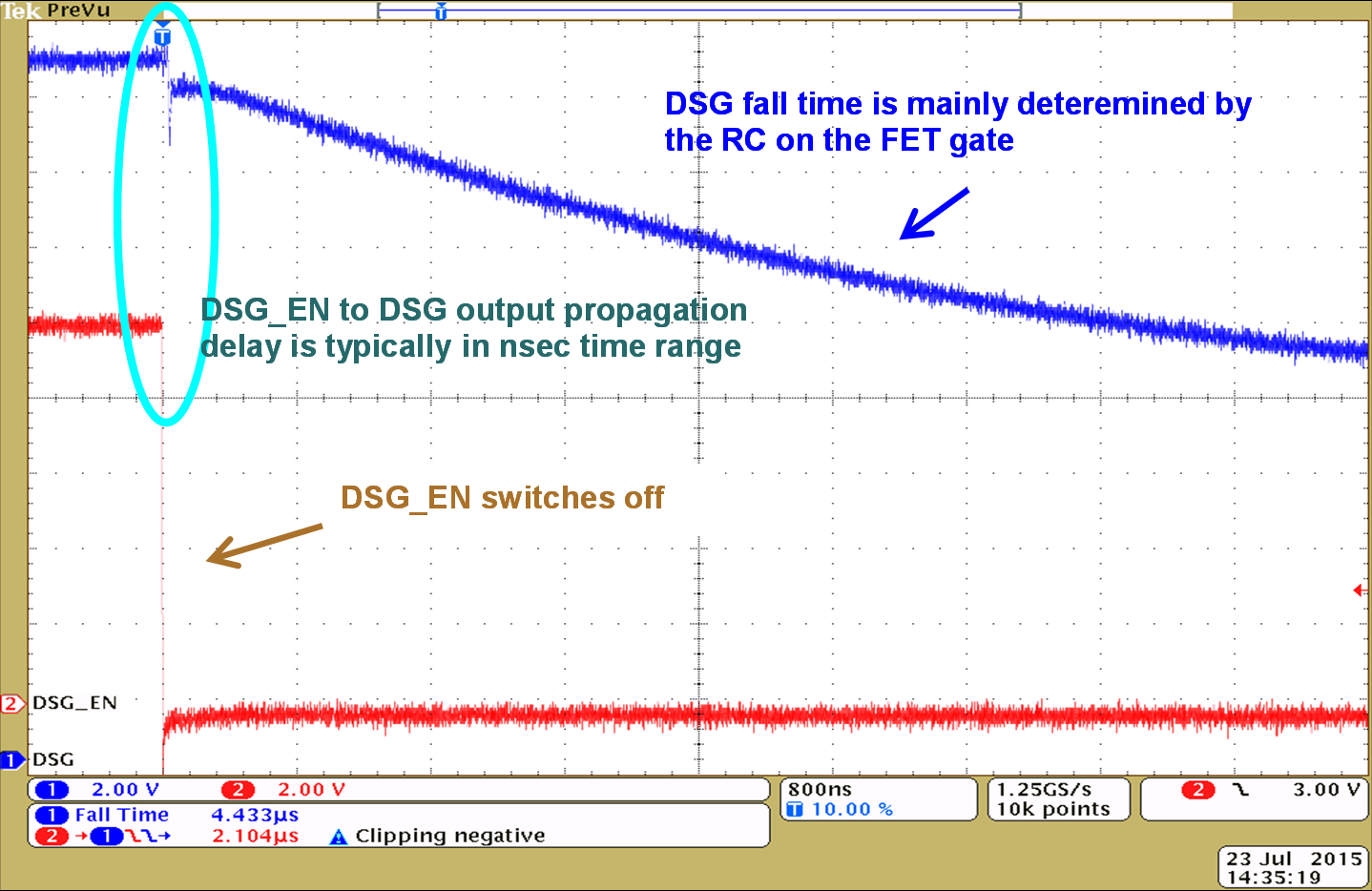

| With 10-nF loading and no Rgs on DSG output. Note the time scale was 800 ns/div; thus, the DSG waveform above is basically the DSG FET fall time. | ||

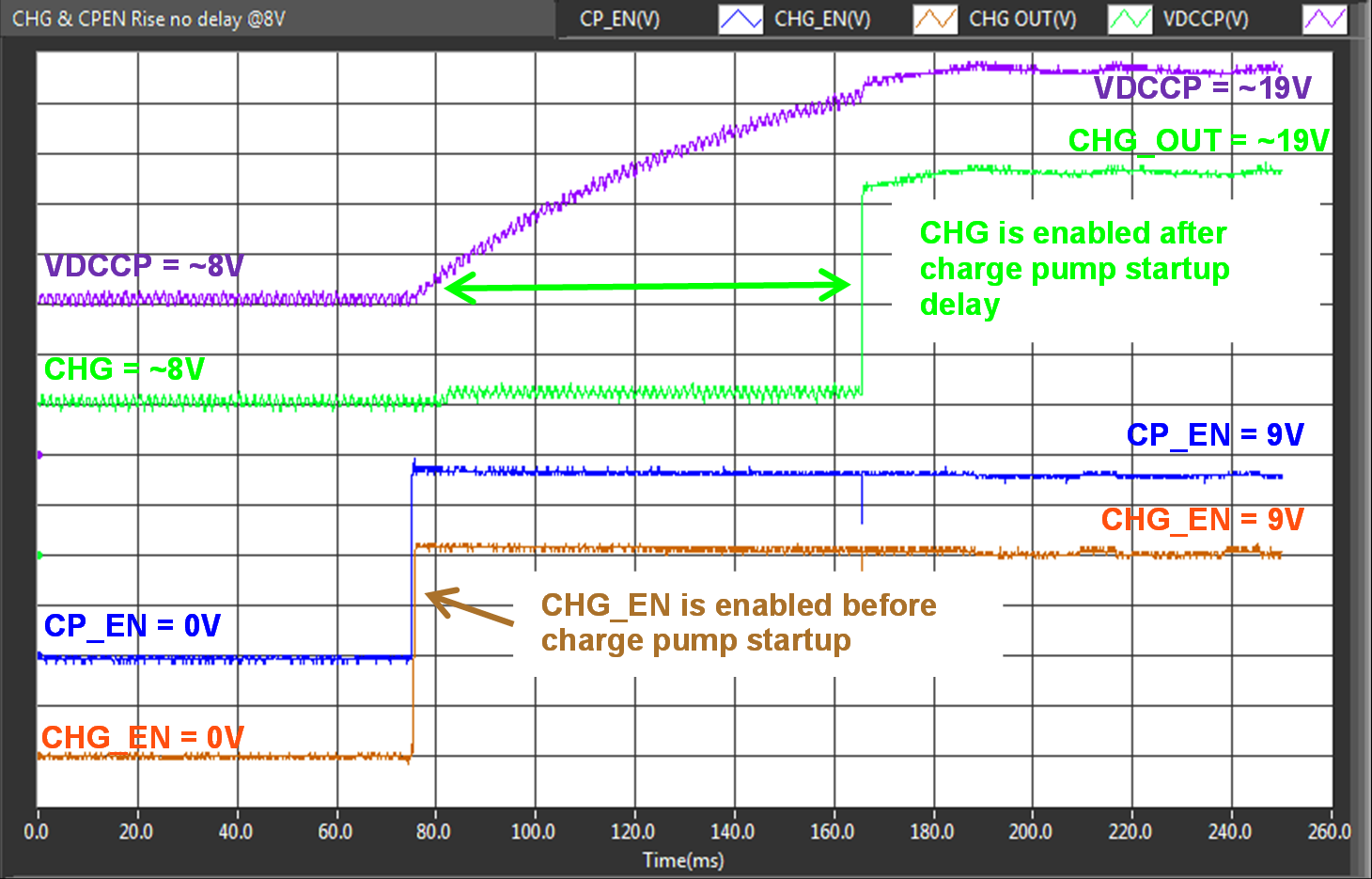

| CHG output reacts to the CHG_EN signal after charge pump startup delay. Similar behavior applies to the DSG pin. |