SLOSE98A December 2022 – September 2023 DRV8461

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Interface of Operation

- 7.3.2 Stepper Motor Driver Current Ratings

- 7.3.3 PWM Motor Drivers

- 7.3.4 Microstepping Indexer

- 7.3.5 Indexer Output

- 7.3.6 Automatic Microstepping Mode

- 7.3.7 Custom Microstepping Table

- 7.3.8 Current Regulation

- 7.3.9 Standstill Power Saving Mode

- 7.3.10 Current Regulation Decay Modes

- 7.3.11 Current Sensing with External Resistor

- 7.3.12 Silent step decay mode

- 7.3.13 Auto-torque Dynamic Current Adjustment

- 7.3.14 Charge Pump

- 7.3.15 Linear Voltage Regulator

- 7.3.16 VCC Voltage Supply

- 7.3.17 Logic Level, Tri-Level and Quad-Level Pin Diagrams

- 7.3.18 Spread Spectrum

- 7.3.19

Protection Circuits

- 7.3.19.1 VM Undervoltage Lockout

- 7.3.19.2 VCP Undervoltage Lockout (CPUV)

- 7.3.19.3 Logic Supply Power on Reset (POR)

- 7.3.19.4 Overcurrent Protection (OCP)

- 7.3.19.5 Stall Detection

- 7.3.19.6 Open-Load Detection (OL)

- 7.3.19.7 Overtemperature Warning (OTW)

- 7.3.19.8 Thermal Shutdown (OTSD)

- 7.3.19.9 Supply voltage sensing

- 7.3.19.10 nFAULT Output

- 7.3.19.11 Fault Condition Summary

- 7.3.20 Device Functional Modes

- 7.4 Programming

- 7.5

Register Maps

- 7.5.1 Status Registers

- 7.5.2

Control Registers

- 7.5.2.1 CTRL1 (address = 0x04) [Default = 0Fh]

- 7.5.2.2 CTRL2 (address = 0x05) [Default = 06h]

- 7.5.2.3 CTRL3 (address = 0x06) [Default = 38h]

- 7.5.2.4 CTRL4 (address = 0x07) [Default = 49h]

- 7.5.2.5 CTRL5 (address = 0x08) [Default = 03h]

- 7.5.2.6 CTRL6 (address = 0x09) [Default = 20h]

- 7.5.2.7 CTRL7 (address = 0x0A) [Default = FFh]

- 7.5.2.8 CTRL8 (address = 0x0B) [Default = 0Fh]

- 7.5.2.9 CTRL9 (address = 0x0C) [Default = 10h]

- 7.5.2.10 CTRL10 (address = 0x0D) [Default = 80h]

- 7.5.2.11 CTRL11 (address = 0x0E) [Default = FFh]

- 7.5.2.12 CTRL12 (address = 0x0F) [Default = 20h]

- 7.5.2.13 CTRL13 (address = 0x10) [Default = 10h]

- 7.5.2.14 CTRL14 (address = 0x3C) [Default = 58h]

- 7.5.3 Indexer Registers

- 7.5.4

Custom Microstepping Registers

- 7.5.4.1 CUSTOM_CTRL1 (address = 0x16) [Default = 00h]

- 7.5.4.2 CUSTOM_CTRL2 (address = 0x17) [Default = 00h]

- 7.5.4.3 CUSTOM_CTRL3 (address = 0x18) [Default = 00h]

- 7.5.4.4 CUSTOM_CTRL4 (address = 0x19) [Default = 00h]

- 7.5.4.5 CUSTOM_CTRL5 (address = 0x1A) [Default = 00h]

- 7.5.4.6 CUSTOM_CTRL6 (address = 0x1B) [Default = 00h]

- 7.5.4.7 CUSTOM_CTRL7 (address = 0x1C) [Default = 00h]

- 7.5.4.8 CUSTOM_CTRL8 (address = 0x1D) [Default = 00h]

- 7.5.4.9 CUSTOM_CTRL9 (address = 0x1E) [Default = 00h]

- 7.5.5

Auto torque Registers

- 7.5.5.1 ATQ_CTRL1 (address = 0x1F) [Default = 00h]

- 7.5.5.2 ATQ_CTRL2 (address = 0x20) [Default = 00h]

- 7.5.5.3 ATQ_CTRL3 (address = 0x21) [Default = 00h]

- 7.5.5.4 ATQ_CTRL4 (address = 0x22) [Default = 20h]

- 7.5.5.5 ATQ_CTRL5 (address = 0x23) [Default = 00h]

- 7.5.5.6 ATQ_CTRL6 (address = 0x24) [Default = 00h]

- 7.5.5.7 ATQ_CTRL7 (address = 0x25) [Default = 00h]

- 7.5.5.8 ATQ_CTRL8 (address = 0x26) [Default = 00h]

- 7.5.5.9 ATQ_CTRL9 (address = 0x27) [Default = 00h]

- 7.5.5.10 ATQ_CTRL10 (address = 0x28) [Default = 08h]

- 7.5.5.11 ATQ_CTRL11 (address = 0x29) [Default = 0Ah]

- 7.5.5.12 ATQ_CTRL12 (address = 0x2A) [Default = FFh]

- 7.5.5.13 ATQ_CTRL13 (address = 0x2B) [Default = 05h]

- 7.5.5.14 ATQ_CTRL14 (address = 0x2C) [Default = 0Fh]

- 7.5.5.15 ATQ_CTRL15 (address = 0x2D) [Default = 00h]

- 7.5.5.16 ATQ_CTRL16 (address = 0x2E) [Default = FFh]

- 7.5.5.17 ATQ_CTRL17 (address = 0x2F) [Default = 00h]

- 7.5.5.18 ATQ_CTRL18 (address = 0x30) [Default = 00h]

- 7.5.6 Silent Step Registers

- 8 Application and Implementation

- 9 Thermal Considerations

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

Orderable Information

7.3.4 Microstepping Indexer

Built-in indexer logic in the device allows a number of different step modes. The MICROSTEP_MODE bits in the SPI register or the M0 and M1 pins are used to configure the step mode as shown in Table 7-5.

MODE = 1 | MODE = 0 | ||

|---|---|---|---|

MICROSTEP_MODE | M0 | M1 | STEP MODE |

0000b | 0 | 0 | Full step (2-phase excitation) with 100% current |

0001b | 0 | 330 kΩ to GND | Full step (2-phase excitation) with 71% current |

0010b | 1 | 0 | Non-circular 1/2 step |

0011b | Hi-Z | 0 | 1/2 step |

0100b | 0 | 1 | 1/4 step |

0101b | 1 | 1 | 1/8 step |

0110b | Hi-Z | 1 | 1/16 step |

0111b | 0 | Hi-Z | 1/32 step |

1000b | Hi-Z | 330 kΩ to GND | 1/64 step |

1001b | Hi-Z | Hi-Z | 1/128 step |

1010b | 1 | Hi-Z | 1/256 step |

When operating with SPI, the device allows stepping and direction change over SPI interface as well, as shown in Table 7-6. Four bits are dedicated for this purpose -

|

Bit |

0b (default) |

1b |

|---|---|---|

|

SPI_DIR |

Driver changes direction based on DIR pin inputs | Direction changes depend on the DIR bit |

|

SPI_STEP |

Stepping depends on the STEP pin inputs | Step changes depend on the STEP bit |

|

DIR |

Motor moves in the reverse direction | Motor moves in the forward direction |

|

STEP |

X |

Indexer advances by one step. STEP bit is self-clearing, becomes 0b after writing 1b to it. |

Table 7-7 shows the relative current and step directions for full-step (71% current), 1/2 step, 1/4 step and 1/8 step operation for the case when DIR pin is logic high or DIR bit is '1'. Higher microstepping resolutions follow the same pattern. The AOUT current is the sine of the electrical angle and the BOUT current is the cosine of the electrical angle. Positive current is defined as current flowing from the xOUT1 pin to the xOUT2 pin while driving.

| 1/8 STEP | 1/4 STEP | 1/2 STEP | FULL STEP 71% | AOUT CURRENT (% FULL-SCALE) | BOUT CURRENT (% FULL-SCALE) | ELECTRICAL ANGLE (DEGREES) |

|---|---|---|---|---|---|---|

| 1 | 1 | 1 | 0% | 100% | 0.00 | |

| 2 | 20% | 98% | 11.25 | |||

| 3 | 2 | 38% | 92% | 22.50 | ||

| 4 | 56% | 83% | 33.75 | |||

| 5 | 3 | 2 | 1 | 71% | 71% | 45.00 |

| 6 | 83% | 56% | 56.25 | |||

| 7 | 4 | 92% | 38% | 67.50 | ||

| 8 | 98% | 20% | 78.75 | |||

| 9 | 5 | 3 | 100% | 0% | 90.00 | |

| 10 | 98% | -20% | 101.25 | |||

| 11 | 6 | 92% | -38% | 112.50 | ||

| 12 | 83% | -56% | 123.75 | |||

| 13 | 7 | 4 | 2 | 71% | -71% | 135.00 |

| 14 | 56% | -83% | 146.25 | |||

| 15 | 8 | 38% | -92% | 157.50 | ||

| 16 | 20% | -98% | 168.75 | |||

| 17 | 9 | 5 | 0% | -100% | 180.00 | |

| 18 | -20% | -98% | 191.25 | |||

| 19 | 10 | -38% | -92% | 202.50 | ||

| 20 | -56% | -83% | 213.75 | |||

| 21 | 11 | 6 | 3 | -71% | -71% | 225.00 |

| 22 | -83% | -56% | 236.25 | |||

| 23 | 12 | -92% | -38% | 247.50 | ||

| 24 | -98% | -20% | 258.75 | |||

| 25 | 13 | 7 | -100% | 0% | 270.00 | |

| 26 | -98% | 20% | 281.25 | |||

| 27 | 14 | -92% | 38% | 292.50 | ||

| 28 | -83% | 56% | 303.75 | |||

| 29 | 15 | 8 | 4 | -71% | 71% | 315.00 |

| 30 | -56% | 83% | 326.25 | |||

| 31 | 16 | -38% | 92% | 337.50 | ||

| 32 | -20% | 98% | 348.75 |

Table 7-8 shows the full step operation with 100% full-scale current for the DIR = 1 case. This stepping mode consumes more power than full-step mode with 71% current, but provides a higher torque at high motor RPM.

| FULL STEP 100% | AOUT CURRENT (% FULL-SCALE) | BOUT CURRENT (% FULL-SCALE) | ELECTRICAL ANGLE (DEGREES) |

|---|---|---|---|

| 1 | 100 | 100 | 45 |

| 2 | 100 | -100 | 135 |

| 3 | -100 | -100 | 225 |

| 4 | -100 | 100 | 315 |

Table 7-9 shows the noncircular 1/2–step operation for the DIR = 1 case. This stepping mode consumes more power than circular 1/2-step operation, but provides a higher torque at high motor RPM.

| NON-CIRCULAR 1/2-STEP | AOUT CURRENT (% FULL-SCALE) | BOUT CURRENT (% FULL-SCALE) | ELECTRICAL ANGLE (DEGREES) |

|---|---|---|---|

| 1 | 0 | 100 | 0 |

| 2 | 100 | 100 | 45 |

| 3 | 100 | 0 | 90 |

| 4 | 100 | –100 | 135 |

| 5 | 0 | –100 | 180 |

| 6 | –100 | –100 | 225 |

| 7 | –100 | 0 | 270 |

| 8 | –100 | 100 | 315 |

When operating with the SPI, depending on the STEP_EDGE bit, STEP active edge can be either rising edge or both rising and falling edge, as shown in Table 7-10. When configured with H/W interface, the STEP active edge is only the rising edge. For applications that need to run at high input STEP rate, configuring both edges as active edge reduces controller overhead by half, because the input STEP rate is effectively doubled.

|

Interface |

STEP_EDGE |

STEP Active Edge |

|---|---|---|

|

SPI |

0b (default) |

Rising edge |

|

1b |

Rising edge and falling edge |

|

|

H/W |

X |

Rising edge |

At each active edge of the STEP input the indexer advances to the next state in the table. The direction shown is with the DIR pin logic high. If the DIR pin is logic low, the sequence table is reversed. If the step mode is changed dynamically while stepping, the indexer advances to the next valid state for the new step mode setting at the active edge of STEP.

After power-up, after exiting logic undervoltage lockout, or after exiting sleep mode, the indexer moves to an initial excitation state (home position) of 45° electrical angle, corresponding to 71% of full-scale current in both coils. All the registers are restored to their deafult values in such scenario.

When operating with the SPI, if the IDX_RST bit is 1b, it resets the indexer to 45° electrical angle as shown in Figure 7-5, but the contents of the memory map registers do not change.

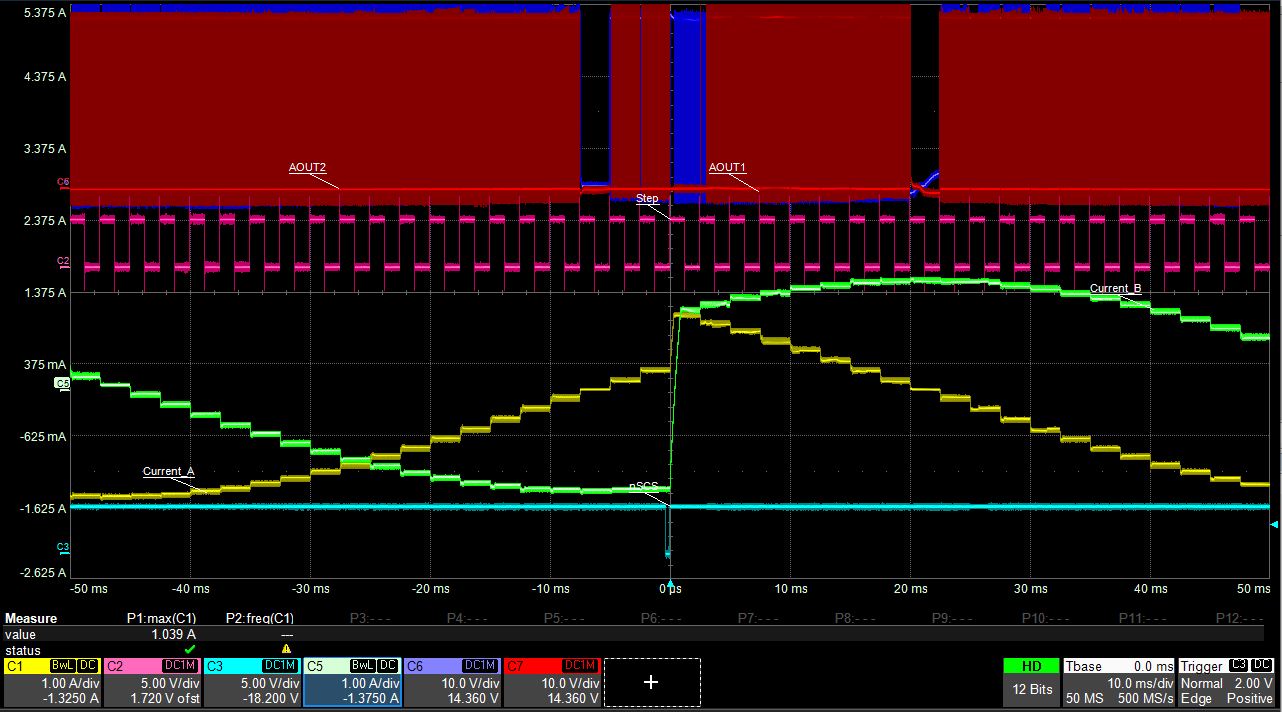

Figure 7-5 Indexer reset. Traces from top to bottom: AOUT2, AOUT1, STEP, coil B current, coil A current, nSCS

Figure 7-5 Indexer reset. Traces from top to bottom: AOUT2, AOUT1, STEP, coil B current, coil A current, nSCSIf the STEP input frequency is jittery, the device filters the signal for the purpose of stall detection. The FRQ_CHG and STEP_FRQ_TOL bits program the filter setting, as shown in Table 7-11. 2% filtering means up to 2% jitter around the center frequency will be filtered out to generate a clean STEP signal for internal circuits to detect motor stall.

|

FRQ_CHG |

STEP_FRQ_TOL |

Filtering |

|---|---|---|

|

0b (default) |

00b |

1% |

|

01b (default) |

2% |

|

|

10b |

4% |

|

|

11b |

6% |

|

|

1b |

Don't care |

No filtering |