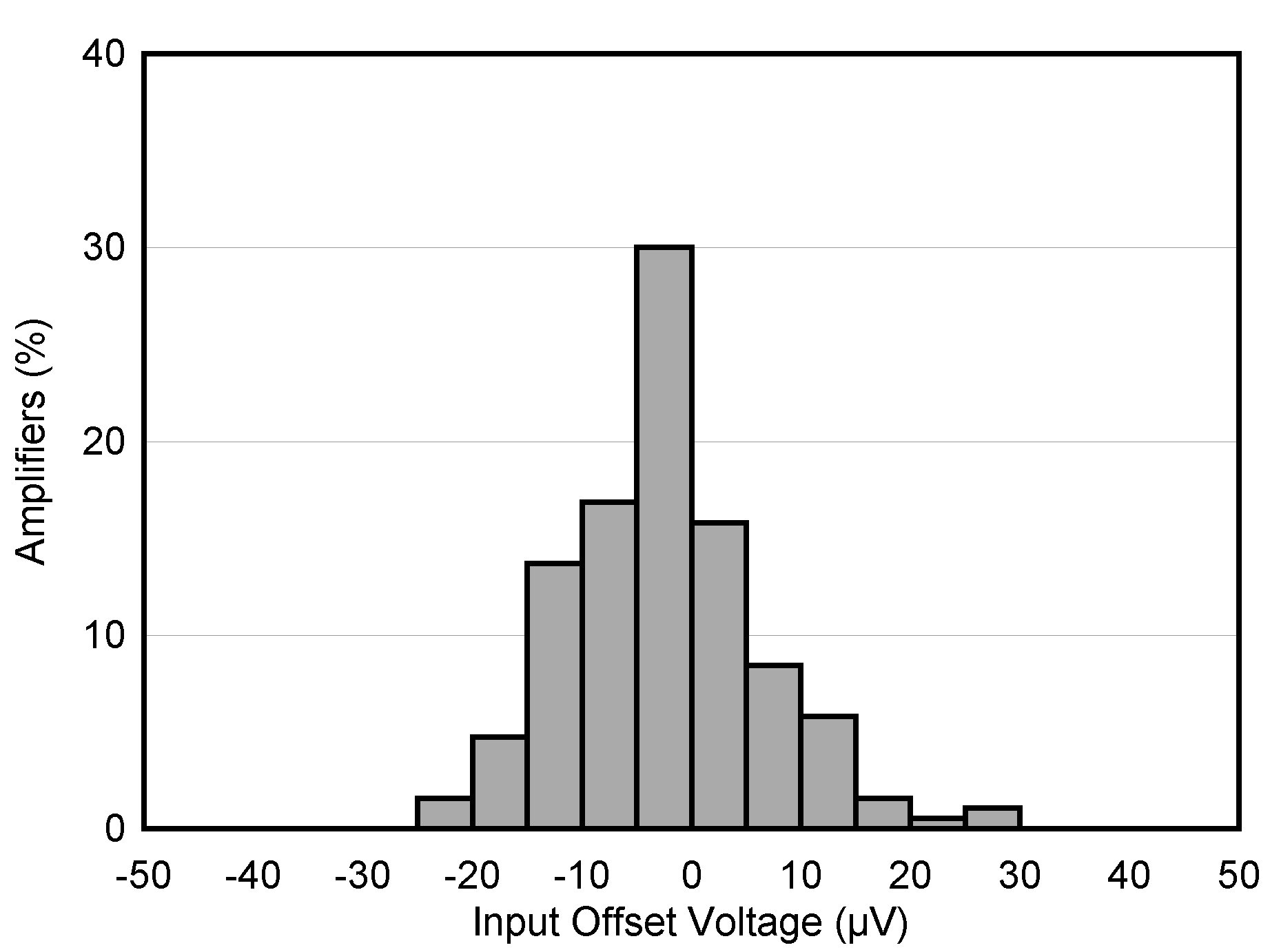

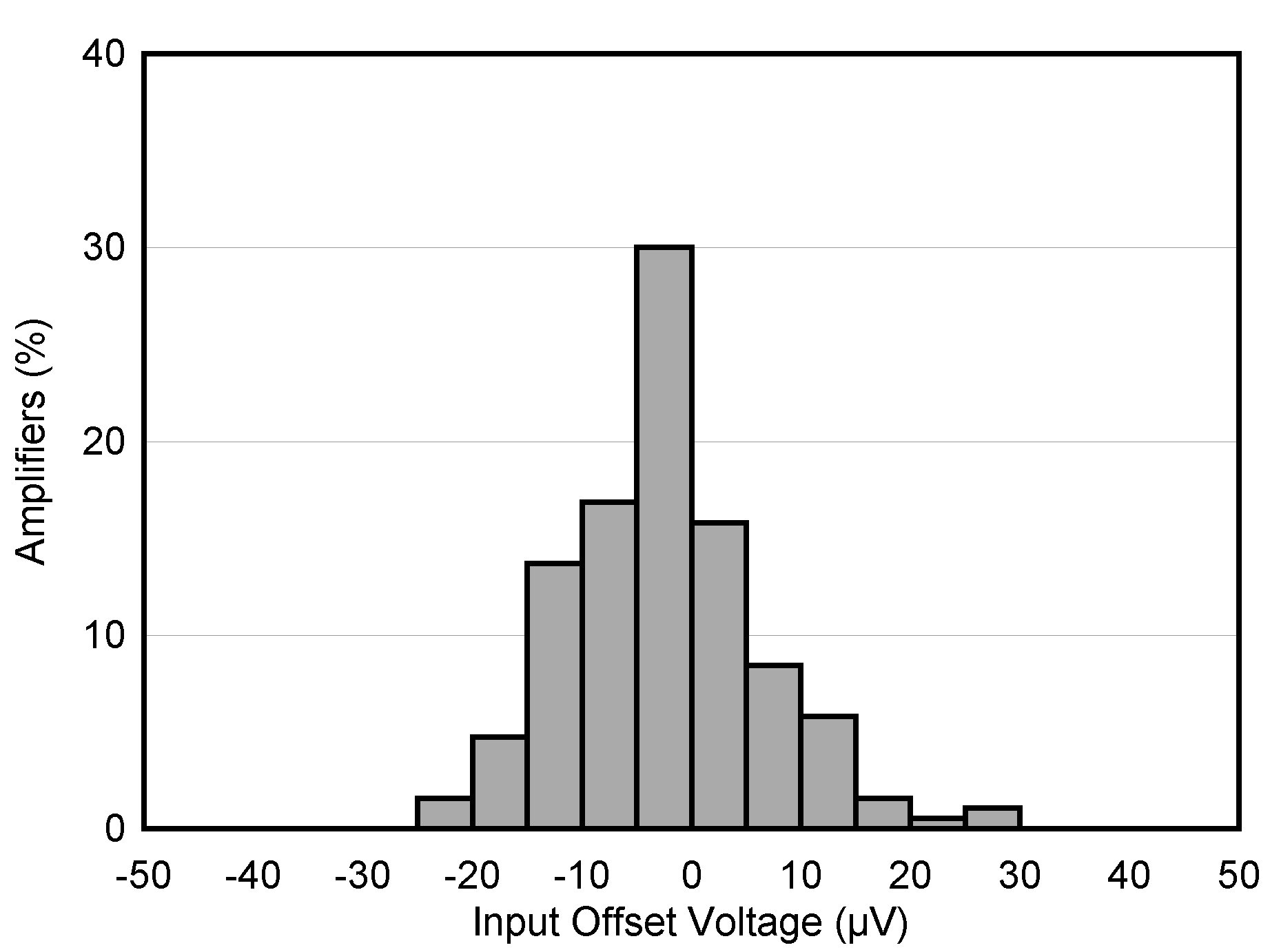

at VVS = ±15 V,

TA = 25°C, VVOCM = VVICM = 0 V, RF =

2 kΩ, RL = 10 kΩ, gain = –1 V/V, and VPD

= VVS+ (unless otherwise noted)

| VS = ±1.5 V, N = 190, mean = –2.66 µV,

std dev = 8.81 µV |

Figure 6-1 Input

Offset Voltage Histogram Figure 6-3 Input

Offset Voltage Drift Histogram

Figure 6-3 Input

Offset Voltage Drift Histogram Figure 6-5 Output Common Mode Voltage Offset

Figure 6-5 Output Common Mode Voltage Offset Figure 6-7 Input Bias Current vs Supply Voltage

Figure 6-7 Input Bias Current vs Supply Voltage Figure 6-9 Current Noise vs Frequency

Figure 6-9 Current Noise vs Frequency Figure 6-11 Total

Harmonic Distortion + Noise vs Amplitude

Figure 6-11 Total

Harmonic Distortion + Noise vs Amplitude Figure 6-13 Closed-Loop Gain vs Frequency

Figure 6-13 Closed-Loop Gain vs Frequency Figure 6-15 Common-Mode Rejection Ratio vs Temperature

Figure 6-15 Common-Mode Rejection Ratio vs Temperature Figure 6-17 Power-Supply Rejection Ratio vs Temperature

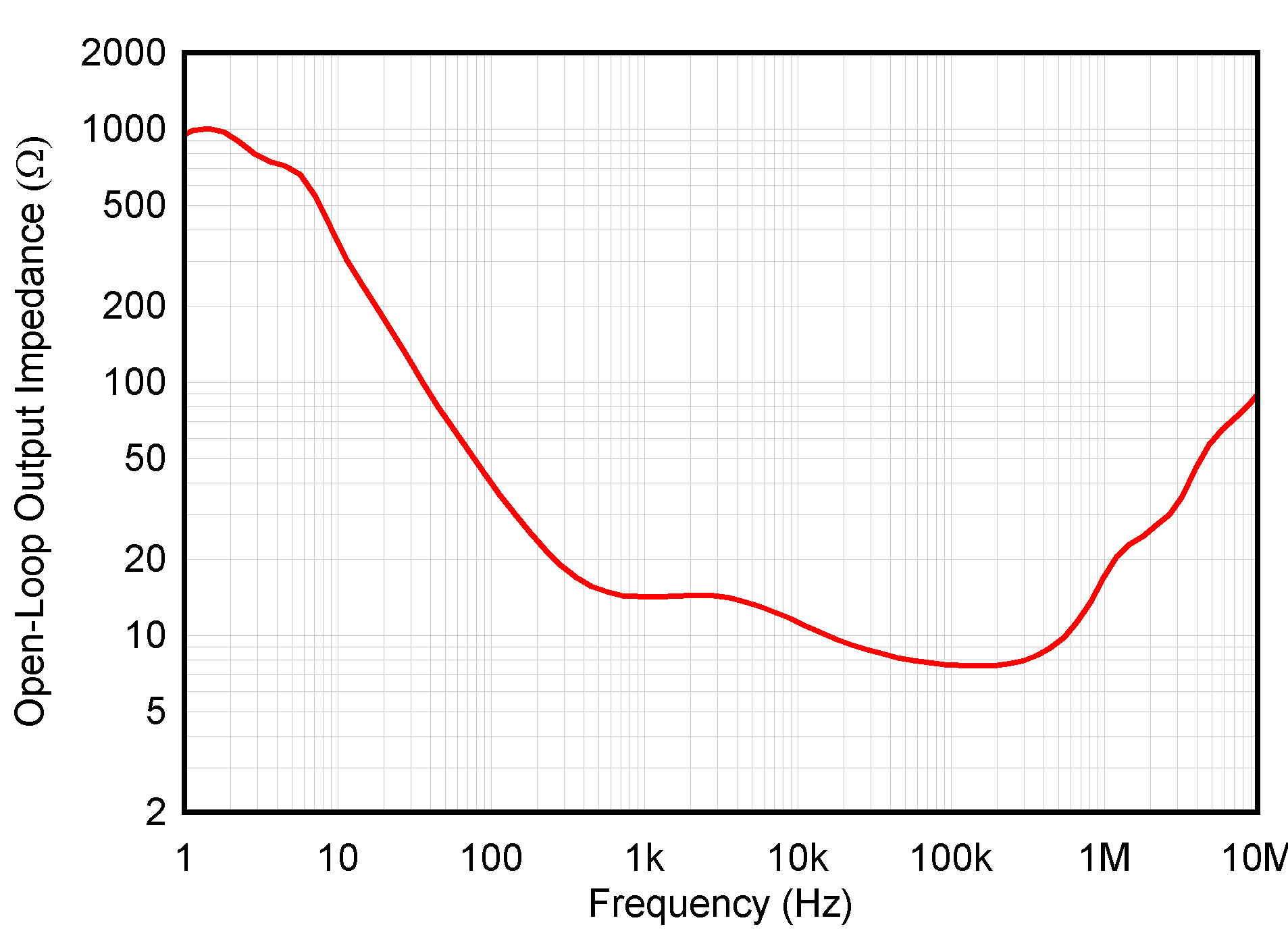

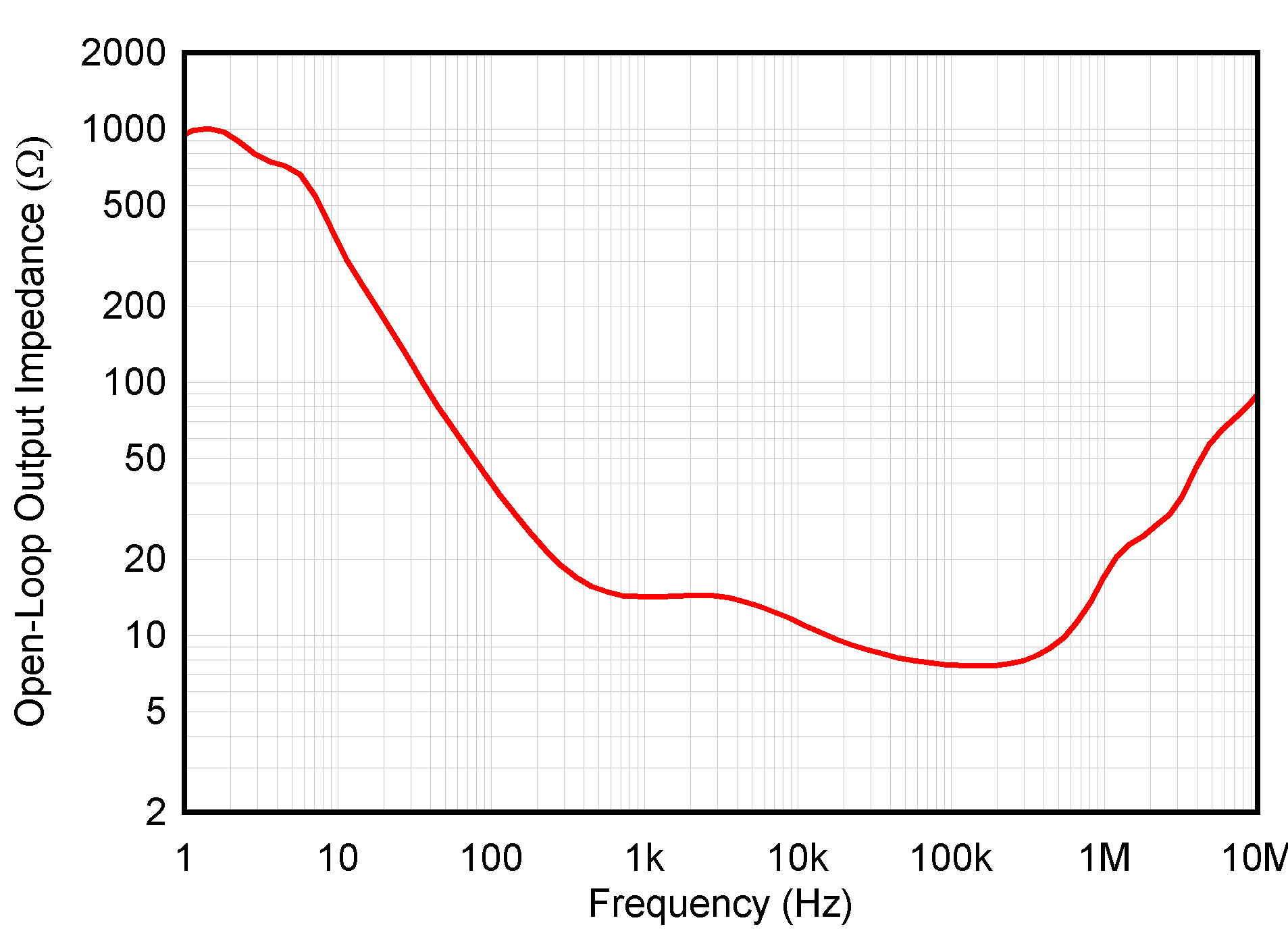

Figure 6-17 Power-Supply Rejection Ratio vs Temperature Figure 6-19 Output Impedance vs Frequency

Figure 6-19 Output Impedance vs Frequency Figure 6-21 Quiescent Current vs Temperature

Figure 6-21 Quiescent Current vs Temperature Figure 6-23 Input

Offset Voltage vs

Figure 6-23 Input

Offset Voltage vs

Input Common-Mode

Voltage Figure 6-25 Small-Signal Overshoot vs Capacitive Load

Figure 6-25 Small-Signal Overshoot vs Capacitive Load Figure 6-27 Small-Signal Step Response, Falling

Figure 6-27 Small-Signal Step Response, Falling Figure 6-29 Output Slew Rate vs Supply Voltage

Figure 6-29 Output Slew Rate vs Supply Voltage Figure 6-31 Open-Loop Gain vs Ouput Delta From Supply

Figure 6-31 Open-Loop Gain vs Ouput Delta From Supply Figure 6-33 Large-Signal Step Response

Figure 6-33 Large-Signal Step Response Figure 6-35 Output Common-Mode Step Response, Falling

Figure 6-35 Output Common-Mode Step Response, Falling Figure 6-37 Power-Down Time (

PD Low to High)

Figure 6-37 Power-Down Time (

PD Low to High) Figure 6-39 Output Negative Overload Recovery

Figure 6-39 Output Negative Overload Recovery

| VS = ±15 V, N = 120, mean = –1.13 µV,

std dev = 5.61 µV |

Figure 6-2 Input

Offset Voltage Histogram

| VS = ±18 V, VOCM = floating |

Figure 6-4 Output Common-Mode Offset Voltage Figure 6-6 Input

Bias Current vs Input Common-Mode Voltage

Figure 6-6 Input

Bias Current vs Input Common-Mode Voltage Figure 6-8 Input-Referred Voltage Noise vs Frequency

Figure 6-8 Input-Referred Voltage Noise vs Frequency

| VOUT = 3 VRMS, VS = ±15 V |

Figure 6-12 Open-Loop Gain vs Frequency

Figure 6-12 Open-Loop Gain vs Frequency Figure 6-14 Common-Mode Rejection Ratio vs Frequency

Figure 6-14 Common-Mode Rejection Ratio vs Frequency Figure 6-16 Power-Supply Rejection Ratio vs Frequency

Figure 6-16 Power-Supply Rejection Ratio vs Frequency Figure 6-18 Maximum Output Voltage vs Frequency

Figure 6-18 Maximum Output Voltage vs Frequency Figure 6-20 Quiescent Current vs Supply Voltage

Figure 6-20 Quiescent Current vs Supply Voltage Figure 6-22 Quiescent Current vs

Power-Down Delta

Figure 6-22 Quiescent Current vs

Power-Down Delta

From Supply Voltage Figure 6-24 Output Voltage vs Output Current

Figure 6-24 Output Voltage vs Output Current Figure 6-26 Small-Signal Overshoot vs Capacitive Load

Figure 6-26 Small-Signal Overshoot vs Capacitive Load Figure 6-28 Small-Signal Step Response, Rising

Figure 6-28 Small-Signal Step Response, Rising Figure 6-30 Output Voltage vs Output Current

Figure 6-30 Output Voltage vs Output Current Figure 6-32 Short-Circuit Current vs Temperature

Figure 6-32 Short-Circuit Current vs Temperature Figure 6-34 Output Common-Mode Step Response, Rising

Figure 6-34 Output Common-Mode Step Response, Rising Figure 6-36 Output Settling Time to ±0.01%

Figure 6-36 Output Settling Time to ±0.01% Figure 6-38 Power-Down Time (

PD High to Low)

Figure 6-38 Power-Down Time (

PD High to Low) Figure 6-40 Output Positive Overload Recovery

Figure 6-40 Output Positive Overload Recovery

Figure 6-21 Quiescent Current vs Temperature

Figure 6-21 Quiescent Current vs Temperature Figure 6-23 Input

Offset Voltage vs

Figure 6-23 Input

Offset Voltage vs

Figure 6-27 Small-Signal Step Response, Falling

Figure 6-27 Small-Signal Step Response, Falling

Figure 6-33 Large-Signal Step Response

Figure 6-33 Large-Signal Step Response Figure 6-35 Output Common-Mode Step Response, Falling

Figure 6-35 Output Common-Mode Step Response, Falling Figure 6-37 Power-Down Time (

PD Low to High)

Figure 6-37 Power-Down Time (

PD Low to High) Figure 6-39 Output Negative Overload Recovery

Figure 6-39 Output Negative Overload Recovery

Figure 6-22 Quiescent Current vs

Power-Down Delta

Figure 6-22 Quiescent Current vs

Power-Down Delta  Figure 6-24 Output Voltage vs Output Current

Figure 6-24 Output Voltage vs Output Current

Figure 6-28 Small-Signal Step Response, Rising

Figure 6-28 Small-Signal Step Response, Rising

Figure 6-34 Output Common-Mode Step Response, Rising

Figure 6-34 Output Common-Mode Step Response, Rising Figure 6-36 Output Settling Time to ±0.01%

Figure 6-36 Output Settling Time to ±0.01% Figure 6-38 Power-Down Time (

PD High to Low)

Figure 6-38 Power-Down Time (

PD High to Low) Figure 6-40 Output Positive Overload Recovery

Figure 6-40 Output Positive Overload Recovery