JAJSOX2 July 2022 TPS7A57

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 説明

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Output Voltage Setting and Regulation

- 7.3.2 Low-Noise, Ultra-High Power-Supply Rejection Ratio (PSRR)

- 7.3.3 Programmable Soft-Start (NR/SS Pin)

- 7.3.4 Precision Enable and UVLO

- 7.3.5 Charge Pump Enable and BIAS Rail

- 7.3.6 Power-Good Pin (PG Pin)

- 7.3.7 Active Discharge

- 7.3.8 Thermal Shutdown Protection (TSD)

- 7.4 Device Functional Modes

-

8 Application and Implementation

- 8.1

Application Information

- 8.1.1 Precision Enable (External UVLO)

- 8.1.2 Undervoltage Lockout (UVLO) Operation

- 8.1.3 Dropout Voltage (VDO)

- 8.1.4 Input and Output Capacitor Requirements (CIN and COUT)

- 8.1.5 Recommended Capacitor Types

- 8.1.6 Soft-Start, Noise Reduction (NR/SS Pin), and Power-Good (PG Pin)

- 8.1.7 Optimizing Noise and PSRR

- 8.1.8 Adjustable Operation

- 8.1.9 Load Transient Response

- 8.1.10 Current Limit and Foldback Behavior

- 8.1.11 Charge Pump Operation

- 8.1.12 Sequencing

- 8.1.13 Power-Good Functionality

- 8.1.14 Output Impedance

- 8.1.15 Paralleling for Higher Output Current and Lower Noise

- 8.1.16 Current Mode Margining

- 8.1.17 Voltage Mode Margining

- 8.1.18 Power Dissipation (PD)

- 8.1.19 Estimating Junction Temperature

- 8.1.20 TPS7A57EVM-081 Thermal Analysis

- 8.2 Typical Application

- 8.3 Power Supply Recommendations

- 8.4 Layout

- 8.1

Application Information

- 9 Device and Documentation Support

- 10Mechanical, Packaging, and Orderable Information

3 説明

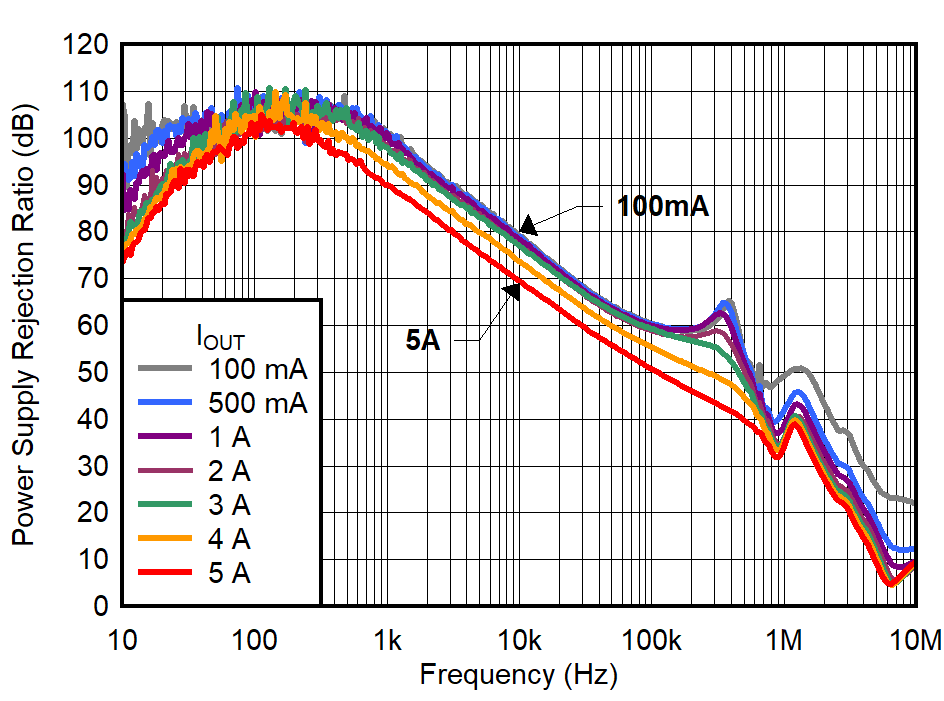

TPS7A57 は低ノイズ (2.45µVRMS)、超低ドロップアウトのリニア・レギュレータ (LDO) で、5A を供給でき、ドロップアウトは出力電圧に関係なく最大でわずか 75mV です。デバイスの出力電圧は、1 個の外付け抵抗を使って 0.5V~5.2V の範囲で調整可能です。低ノイズ、高 PSRR (1MHz で 36dB)、大出力電流能力を組み合わせた TPS7A57 は、レーダーの電源、通信、画像処理の各アプリケーションで使用される、ノイズに敏感な部品 (RFアンプ、レーダー・センサ、SerDes、アナログ・チップセットなど) への電力供給に最適です。

ASIC (Application-Specific Integrated Circuit)、FPGA (Field-Programmable Gate Array)、DSP (Digital Signal Processor) など、低入力電圧、低出力電圧 (LILO) での動作を必要とするデジタル負荷には、非常に優れた精度 (負荷、ライン、および温度の全範囲で 1%)、リモート・センシング、優れた過渡性能、ソフトスタート機能により、最適なシステム性能を提供します。汎用性、高性能、小型フットプリントを特長とするこの LDO は、A/D コンバータ (ADC)、D/A コンバータ (DAC)、イメージング・センサなどの大電流アナログ負荷や、シリアライザ/デシリアライザ (SerDes)、FPGA、DSP などのデジタル負荷用の優れた選択肢です。

パッケージ情報(1)

| 部品番号 | パッケージ | 本体サイズ (公称) |

|---|---|---|

| TPS7A57 | WQFN (16) | 3.00mm × 3.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

代表的なアプリケーション回路

代表的なアプリケーション回路 CP を有効にした 5A、1.2VIN、0.9VOUT PSRR

CP を有効にした 5A、1.2VIN、0.9VOUT PSRR