JAJA725B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

2.3 電源および電圧リファレンスを内蔵

MSPM0G ファミリ用の VREF モジュールは、さまざまなオンボード・アナログ・ペリフェラルで利用できる共有電圧リファレンス・モジュールです。

VREF モジュールの主な特長は次のとおりです。

- 1.4V および 2.5V の内部リファレンスをユーザーが選択可能。

- VREF+ および VREF- デバイス・ピンでの外部リファレンスの受信をサポート。

- サンプル / ホールド・モードは、スタンバイ動作モードまでの VREF 動作をサポートします。

- ADC、COMP、OPA の内部リファレンスをサポート。

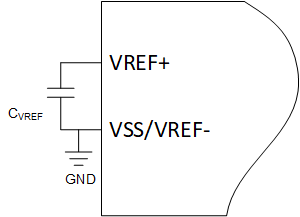

MCU に外部基準電圧を供給する場合、基準ピンのデカップリング・コンデンサを、電圧源に基づく値で接続することを、テキサス・インスツルメンツは推奨します (図 2-2 を参照)。

図 2-2 VREF 回路

図 2-2 VREF 回路